一、实验目的

1、掌握中规模集成译码器的逻辑功能和使用方法

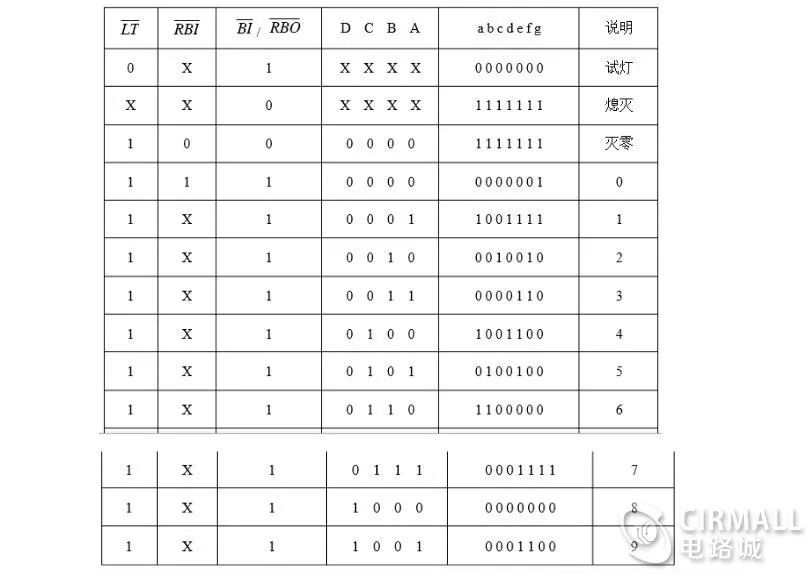

2、熟悉数码管的使用

二、实验原理

译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。不同的功能可选用不同种类的译码器。

译码器可分为通用译码器和显示译码器两大类。前者又分为变量译码器和代码变换译码器。

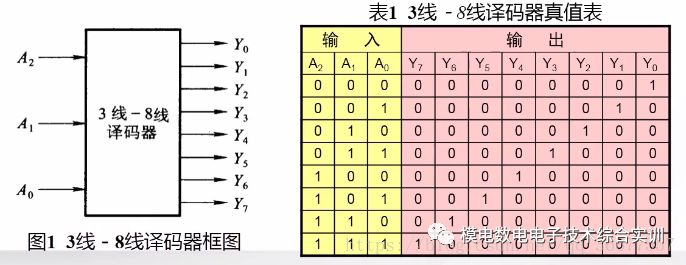

变量译码器(又称二进制译码器),用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。若有n个输入变量,则有2^n^个不同的组合状态,就有2^n^ 个输出端供其使用。而每一个输出所代表的函数对应于n个输入变量的最小项。

1、3线-8线译码器74LS138功能测试 。

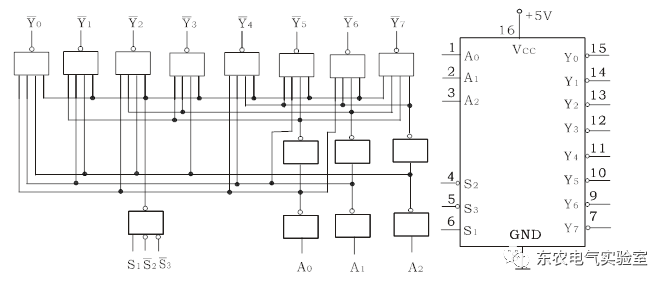

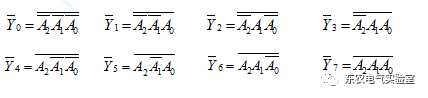

1)译码器的逻辑图与逻辑表达式

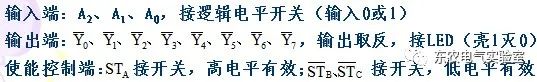

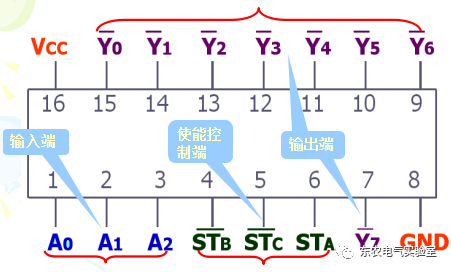

2)芯片介绍

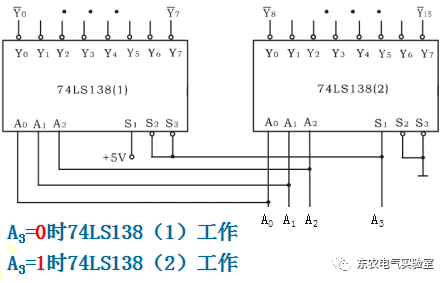

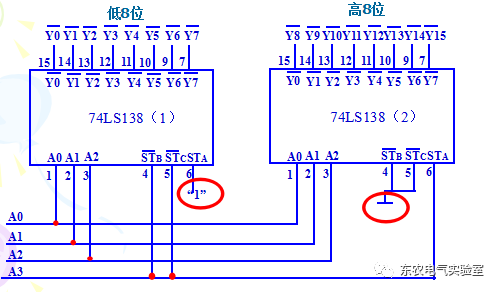

2. 4线-16线译码器

利用使能端能方便地将两个 3/8译码器组合成一个4/16译码器。

三、实验设备与器件

1.电子学综合实验装置

2.+5V直流电源

3.逻辑电平开关

4.LED

5.74LS138

四 实验内容

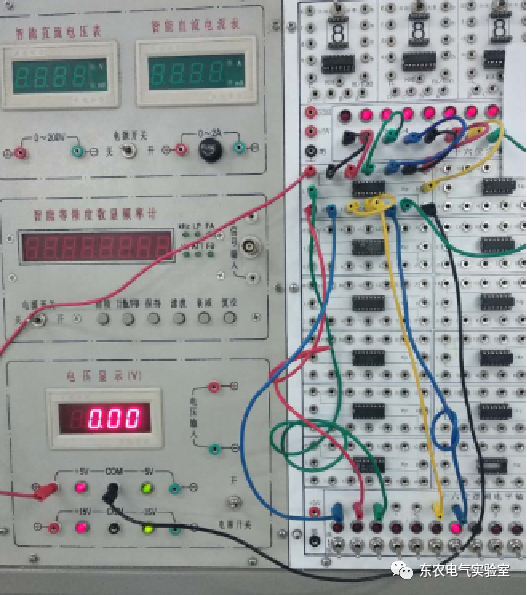

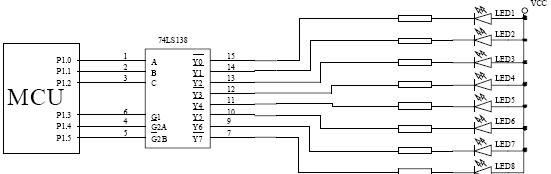

1.74LS138译码器逻辑功能测试

将译码器使能端STA、STB、STC与地址端A2、A1、A0分别接到逻辑电平开关输入口,八个输出端Y7…Y0依次连接在十六位逻辑电平显示上,拨动逻辑电平开关,逐项测试74LS138的逻辑功能。

2.排错检查

实验箱电源连接正确,电路自查确定无误后,电路验证还是不正确的情况下进行下面的排错检查:

1)检查芯片的电源和地的电平是否正确。

2)芯片的使能端连接的电平正确。

3)从逻辑电平开关输入信号是否正确。

4)从输出端按逻辑功能状态往前一步一步排查。

电路无异常,可完成相应功能测试 。

实验步骤- 按照芯片管脚接线:

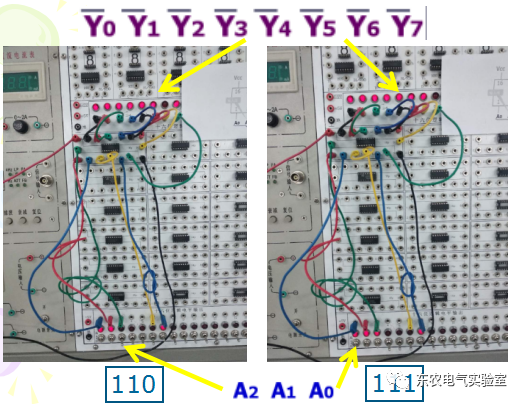

实验步骤- A2、A1、A0分别置为000、001,观察输出状态。

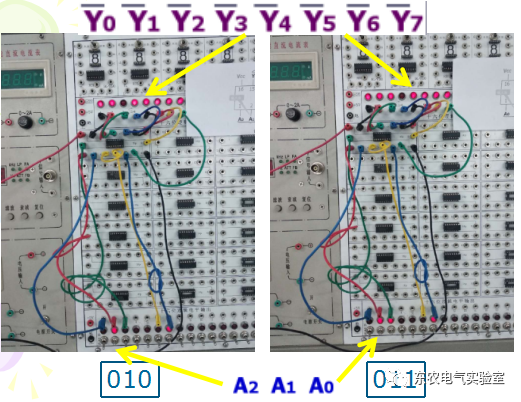

实验步骤- A2、A1、A0分别置为010、011,观察输出状态。

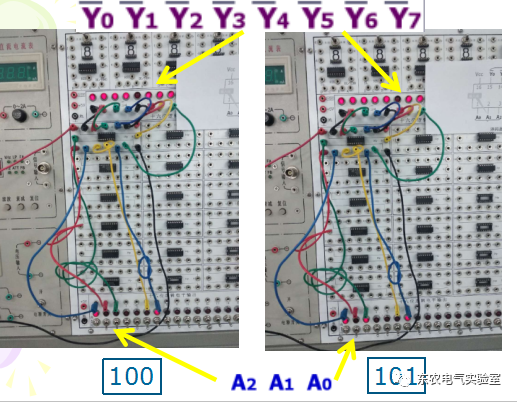

实验步骤- A2、A1、A0分别置为100、101,观察输出状态。

实验步骤- A2、A1、A0分别置为110、111,观察输出状态。

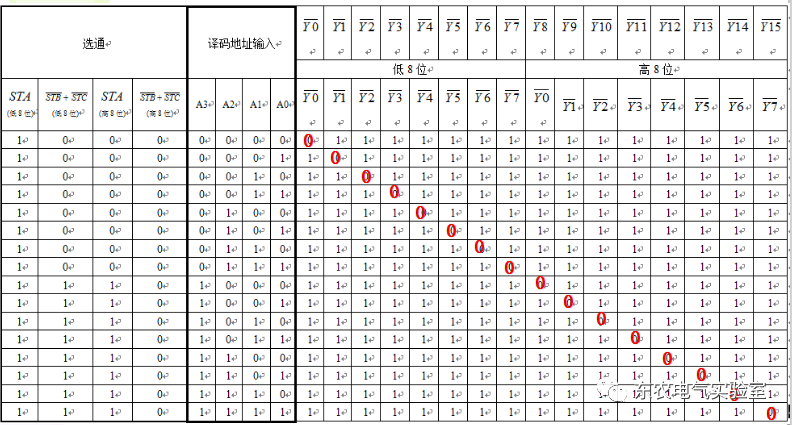

74LS138译码器的逻辑功能表

3.两片3线-8线译码器74LS138扩展为4线-16线译码器

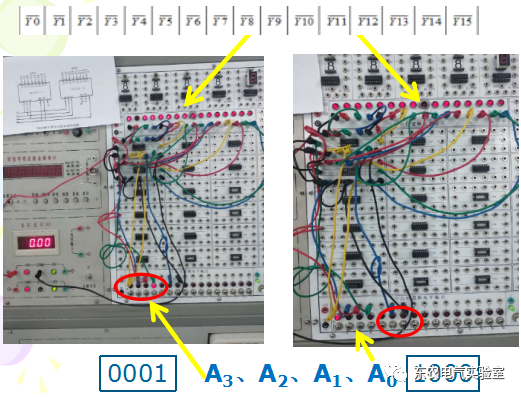

按下图接线,用两片74LS138组合成一个四线-十六线译码器进行实验,并分析逻辑功能。

实验步骤- A3、A2、A1、A0分别置为0001、1000,观察输出状态。

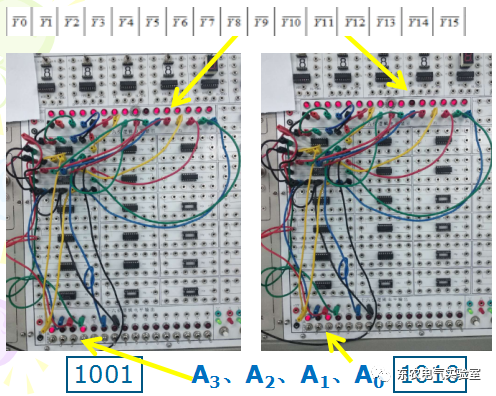

实验步骤- A3、A2、A1、A0分别置为1001、1010,观察输出状态。

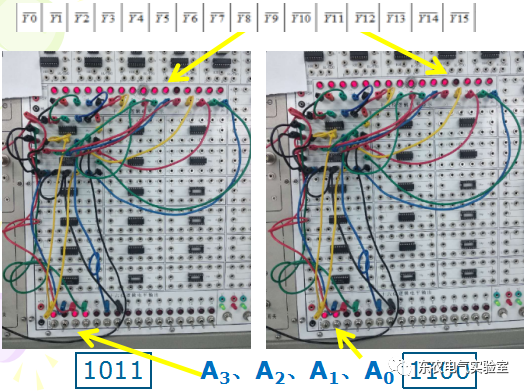

实验步骤- A3、A2、A1、A0分别置为1011、1100,观察输出状态。

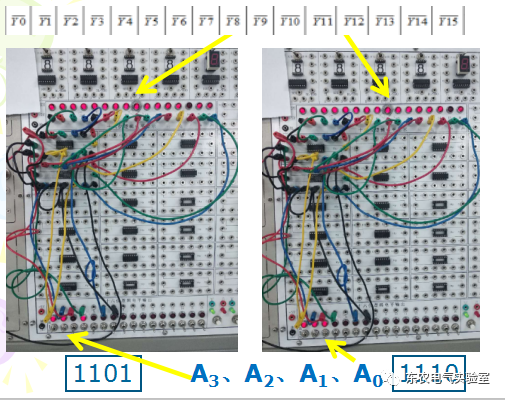

实验步骤- A3、A2、A1、A0分别置为1101、1110,观察输出状态。

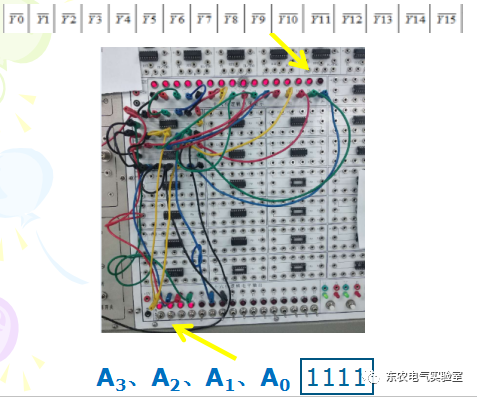

实验步骤- A3、A2、A1、A0置为1111,观察输出状态。

74LS138扩展为4线-16线译码器的逻辑功能表 :

-

逻辑电路

+关注

关注

13文章

494浏览量

42698 -

二进制

+关注

关注

2文章

796浏览量

41751 -

数码管

+关注

关注

32文章

1883浏览量

91381 -

译码器

+关注

关注

4文章

312浏览量

50444 -

74ls138

+关注

关注

13文章

50浏览量

36125

发布评论请先 登录

相关推荐

基于IP核的Viterbi译码器实现

请问一下缓冲器和译码器的使用方法

译码器定义

集成译码器的逻辑功能和使用方法

译码器的逻辑功能和使用方法

译码器的逻辑功能和使用方法

评论