低介电常数材料简介

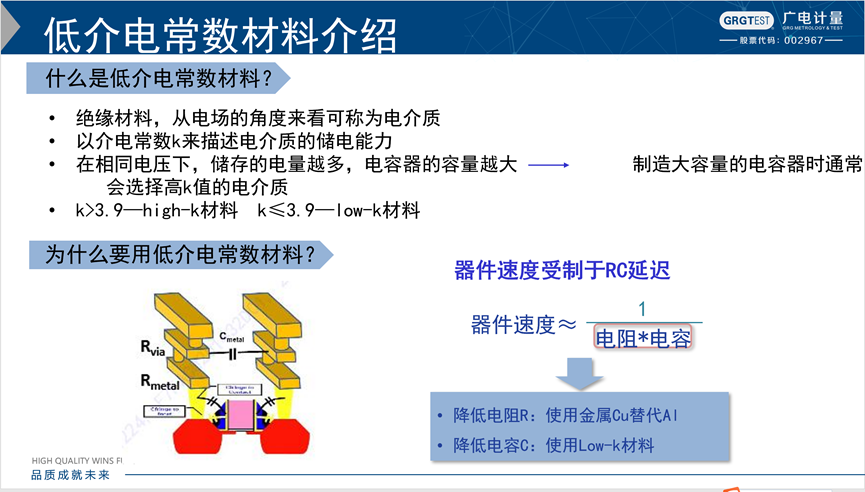

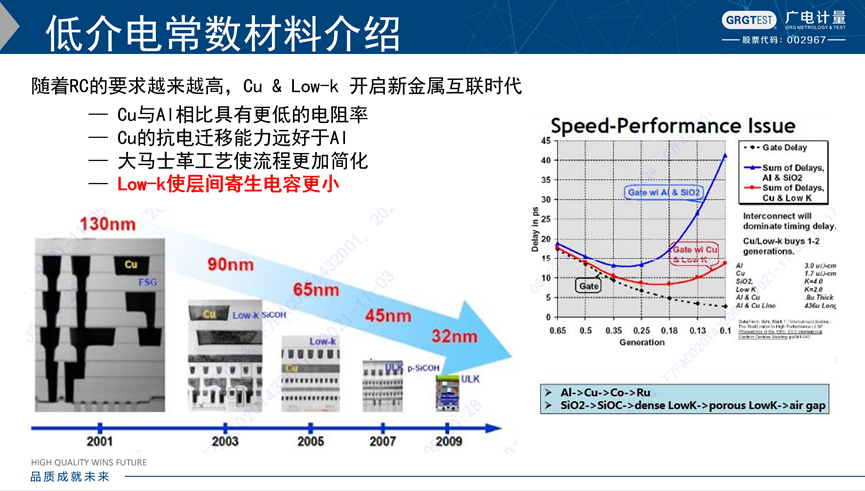

低介电常数材料是指介电常数较小的材料,通过降低集成电路中使用的介电材料的介电常数,可以降低集成电路的漏电电流、降低导线之间的电容效应、降低集成电路发热等等,更可以有效提升电子元器件的速度。

如何降低材料的介电常数?

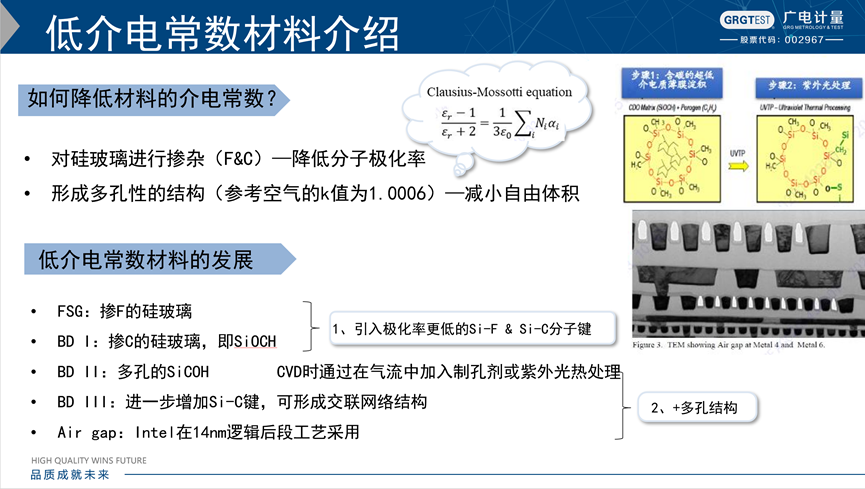

既然降低材料的介电常数有那多好处,那如何降低材料的介电常数呢?

降低介电常数的方法有多种方法,其中一种方法是通过添加一些添加剂来改变材料的物理和化学性质,从而降低其介电常数。例如,添加一些氟化物或氧化物可以降低陶瓷的介电常数。

另外,可以通过改变制备工艺来降低材料的介电常数,例如,通过等离子体增强化学气相沉积(PECVD)技术来制备低介电常数材料。

低介电常数材料应用存在的问题

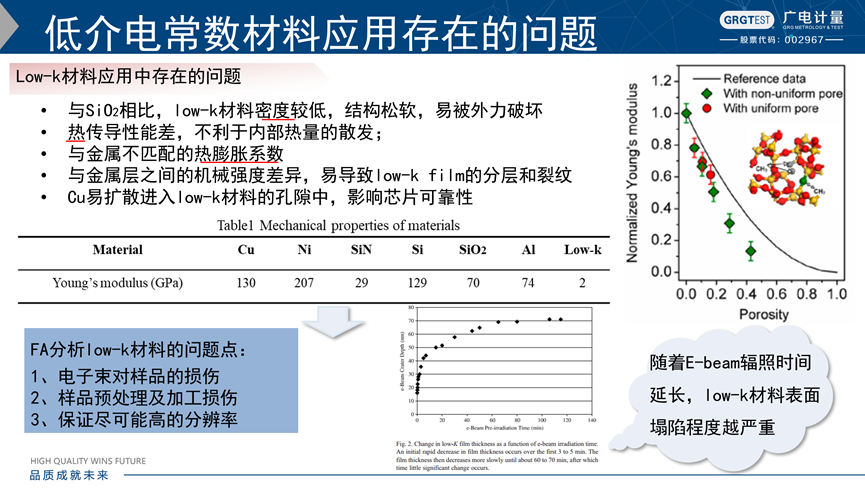

虽然低介电常数材料具有各种优点,但在实际应用中需要提前知悉使用低介电常数材料的相关风险。

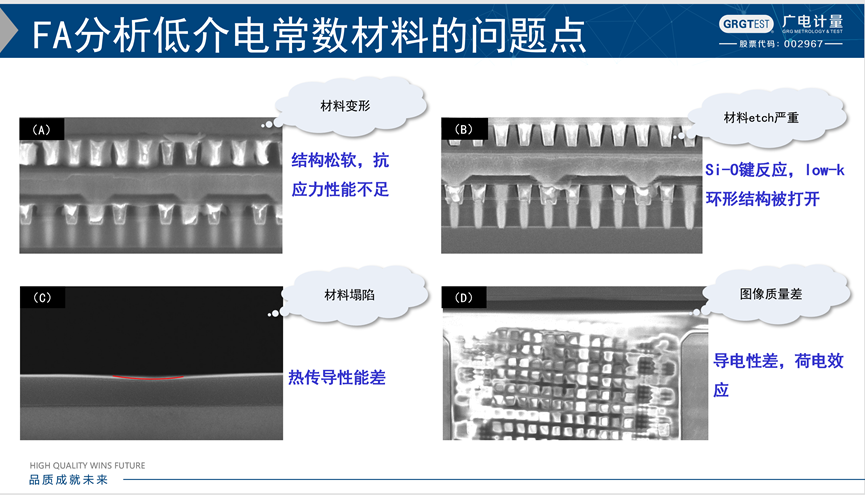

与二氧化硅相比,低介电常数材料有较低的密度和松软的结构,使其更容易受到外部力量的破坏。此外,由于其热传导性能较差,不利于内部热量的散发;同时,它的热膨胀系数也与金属不匹配,可能导致分层和裂纹的产生。另外,低介电常数材料与金属层之间的机械强度存在差异,这也易导致分层和裂纹的出现。最后,Cu易扩散进入低介电常数材料的孔隙中,从而影响芯片的可靠性。

低介电常数材料的失效分析难点

同样基于低介电常数材料的材料特点,在对低介电常数材料进行失效原因分析的时候容易由于分析设备电子束直接造成对样品的伤害,导致无法有效分析其失效原因。

其中有效的解决方法包括:

1. 涂层Pt可改善样品导电性,减弱荷电效应;

2. 降低SEM观察电压,减小高能电子束辐射损伤和荷电效应;

3. 减小工作距离,可提高图像分辨率,弥补电压降低的不利影响;

4. 减弱束流,弱化电子束的短时轰击损伤;

这些措施可以帮助保护样品,同时提高图像质量。

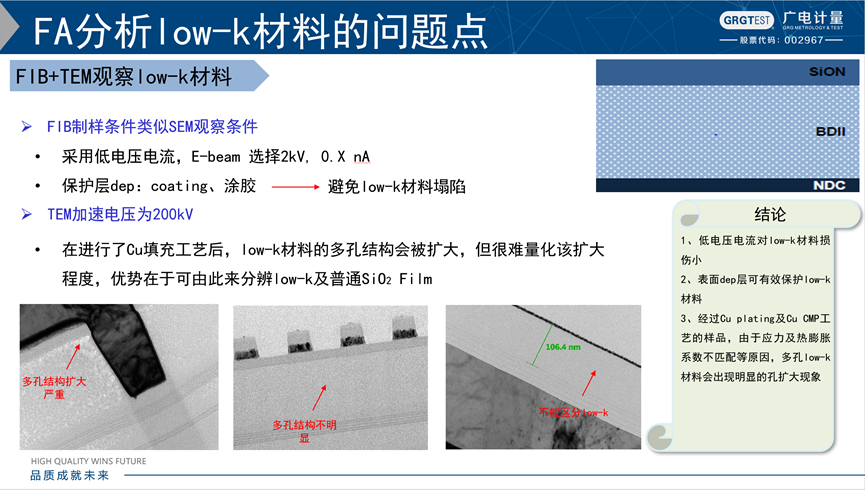

根据我们的研究结果,我们可以得出以下结论:

1. 低电压电流对低介电常数材料造成的损伤相对较小。在实验过程中,我们发现使用低电压电流进行操作可以有效地减少low-k材料的损伤程度,在相关失效分析操作中需要尽可能减低电压与电流;

2. 表面dep层可以有效地保护低介电常数材料不受损坏。通过在low-k材料表面添加dep层,可以形成一个保护层,有效地隔离试验本身对材料的影响;

3. 经过Cu plating及Cu CMP工艺处理的样品中,由于应力和热膨胀系数不匹配等原因,多孔低介电常数材料会出现明显的孔扩大现象,可以用于分辨低介电常数材料与普通的二氧化硅材料。

-

集成电路

+关注

关注

5387文章

11510浏览量

361538 -

电容

+关注

关注

99文章

6028浏览量

150235 -

材料

+关注

关注

3文章

1214浏览量

27266

发布评论请先 登录

相关推荐

介电常数在高频信号中的表现

如何选择适合的材料以满足介电常数要求

介电常数与电容器性能的关系

介电常数在无线通信中的应用

介电常数与频率的关系 影响介电常数的因素有哪些

如何测量介电常数 介电常数在电磁波中的作用

介电常数对电子设备的影响

介电常数的定义及应用 不同材料的介电常数比较

变介电常数型电容传感器的主要优点

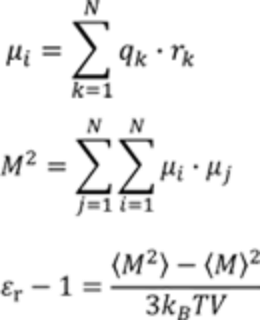

使用MD和MO/DFT计算相对介电常数

低介电常数材料的失效分析

低介电常数材料的失效分析

评论