设计人员在实现RISC-V解决方案的差异化方面有多种途径可供选择,

1)根据规范自定义和扩展各种RISC-V核心

2)围绕一个或多个RISC-V内核的完整片上系统(SoC)设计中选择和组装IP模块。

一个新的趋势正在兴起,即使用片上网络(NoC)而不是简单的总线结构来互连RISC-V内核和其他IP块,不仅适用于高端领域,而且在解决许多SoC设计挑战时具有潜力,尤其是在数据必须高效流动的各种工作负载中。

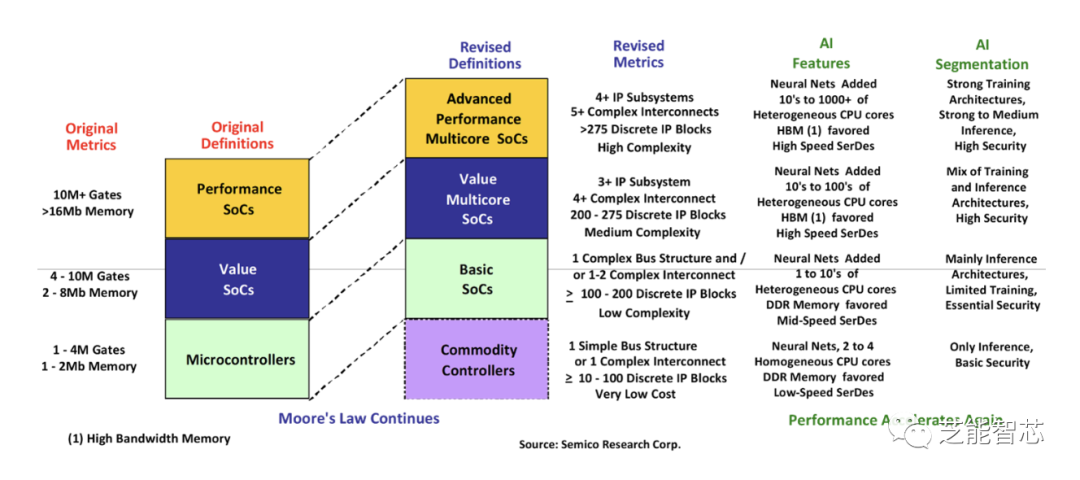

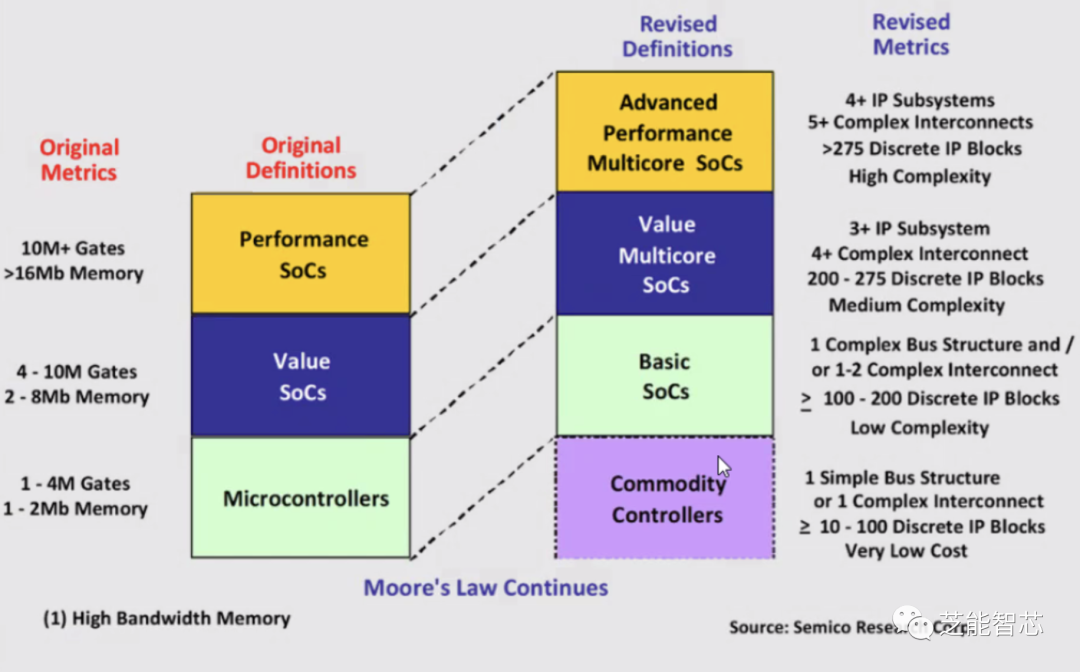

过去,常常以门数、内核数量和外围模块的简单计算来衡量SoC设计的性能潜力。随着技术的不断发展,互连方案现在已经成为定义SoC性能的关键因素之一。新的性能层次正在不断涌现,互连从简单的总线结构演变为更加复杂的解决方案。

Semico Research表示,现在互连方案已经在SoC性能层次之间划定了界限,并引入了新的性能等级,更新定义考虑了多核设计的普及、复杂设计的高标准以及"微控制器"和"SoC"之间的模糊边界。门数不再被视为衡量性能的标准,现代处理器核心可以拥有大量门。互连的复杂性则取决于子系统和不同IP块之间的不同。

根据Semico的性能等级,可以将SoC划分为不同的层次。在最低端,可以使用简单的总线结构,适用于具有单个处理器核心和低占用率外围设备的部件,这些外围设备不会竞争总线资源。在稍高一级的SoC中,可能包括一些竞争片上带宽和处理器核心的外围设备,这些设备被称为"商品控制器层"。更高一级的SoC则包括多个内核和多个IP子系统,每个子系统都使用了经过调整的互连技术。

01.NoC的崭露头角

随着更强大的RISC-V内核的出现,RISC-V迅速提升了各种性能等级,包括Semico的低端性能等级。对于较高层次的复杂互连方案,RISC-V设计人员可能会缺乏经验。Frank Schirrmeister(Arteris)"TileLink可能是RISC-V互连的第一个想法,但在更复杂的情景中使用可能会变得困难。"

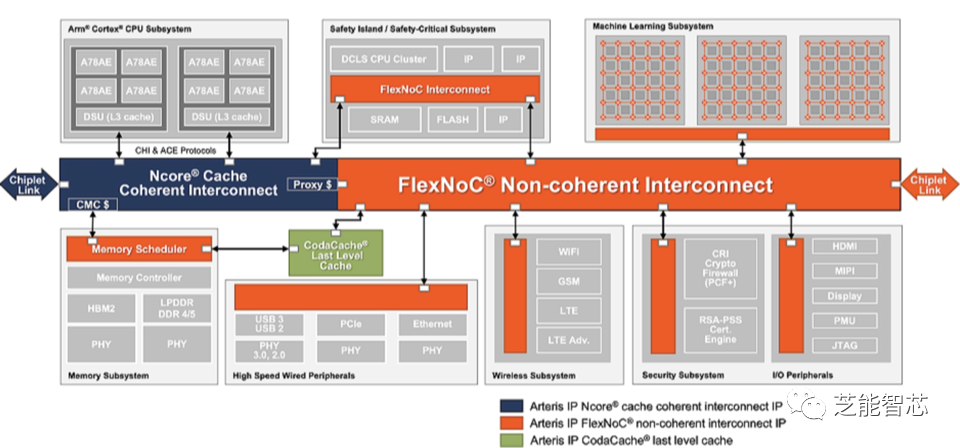

NoC的优势在于它能够使用不同的协议连接子系统,因此SoC设计人员可能需要处理多种不同复杂度的协议。例如,对于简单的IP块连接,AXI协议提供了公平的竞争环境。而对于具有协同处理块的多核解决方案,则需要CHI协议来确保缓存一致性。此外,I/O内存共享有助于形成更快速的CXL互连。Schirrmeister继续说道:"当需要与各种子系统和协议共同优化计算和数据传输时,NoC是更好的解决方案。"

02.RISC-V内核与NoC的完美配对

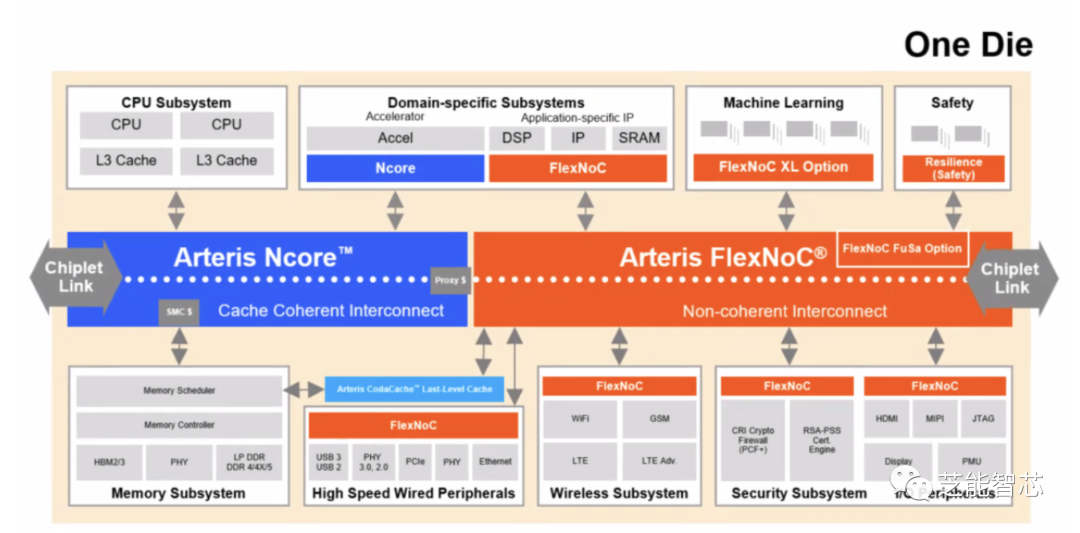

将RISC-V内核与NoC配对将会是什么样子呢?创建一个可重复使用的小芯片,结合了RISC-V内核、机器学习加速IP和标准外围设备,适用于各种边缘AI应用。这个设计还包括了智能内存控制器(SMC),用于提供高性能的内存连接,特别适用于内存密集型应用和服务器级内存连接。未命名的"小芯片链路"可能是UCIe,这是一种相对较新的规范,针对更紧密的小芯片集成进行了优化。在新的子系统互连出现时,调整NoC的一部分比重新设计整个芯片范围的结构更容易管理。

03.降低风险,加速上市时间

这个设计看起来很复杂,但大多数RISC-V应用目前可能并不那么复杂,随着创新步伐的加快,当今先进的RISC-V多核部件将成为明年的SoC的核心价值所在。将RISC-V内核与NoC配对不仅可以降低风险,还可以缩短复杂SoC设计的上市时间。此外,NoC还提供了其他优势,如更高的带宽和更有效的电源管理。考虑到不同协议的组合,RISC-V设计中的NoC正在成为一种强大的解决方案。

-

模块

+关注

关注

7文章

2661浏览量

47300 -

soc

+关注

关注

38文章

4112浏览量

217821 -

RISC-V

+关注

关注

44文章

2218浏览量

45972

原文标题:RISC-V与NoC:开创差异化的新途径

文章出处:【微信号:算力基建,微信公众号:算力基建】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ISA ARM 对比 RISC-V

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

risc-v的发展历史

rIsc-v的缺的是什么?

江苏移动携手华为率先完成全省范围智能差异化体验保障商用验证

RISC-V的MCU与ARM对比

鸿蒙ArkUI-X平台差异化:【运行态差异化(@ohos.deviceInfo)】

解锁RISC-V技术力量丨曹英杰:RISC-V与大模型探索

什么是RISC-V?RISC-V的关键技术

“芯”破局者RISC-V,风好正是扬帆时

赛昉科技重磅亮相RISC-V Summit 2023

RISC-V与NoC:开创差异化的新途径

RISC-V与NoC:开创差异化的新途径

评论