软件锁相环在频率突变时锁不住 锁相环无法锁定怎么办?

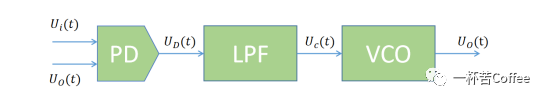

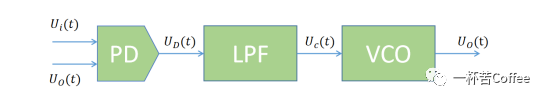

锁相环(PLL)是一种用于在电路中生成稳定频率的技术。它是在1960年代开发的,并被广泛应用于通信、雷达、卫星技术等领域中。锁相环的主要作用是将某一参考信号的频率和相位锁定到一个输出信号的频率和相位。

然而,在一些情况下,锁相环无法锁定输入信号。特别是在输入信号频率发生了剧烈变化时,锁相环的反应速度跟不上变化,导致无法锁定。此外,输入信号中存在噪声干扰,也会使锁相环无法正常工作。

在这种情况下,我们可以采取以下措施来解决问题:

1. 提高锁相环带宽:带宽越高,锁相环的响应速度越快,能够更快地适应输入信号的变化。因此,提高锁相环的带宽是最有效的方法之一。可以通过增加锁相环的环路增益来提高带宽。

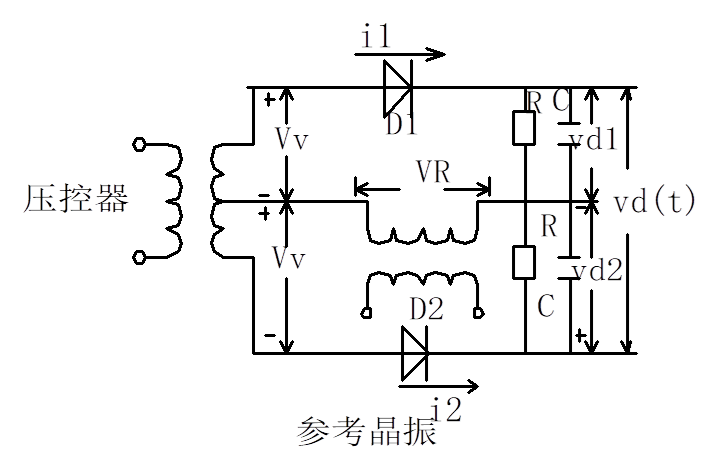

2. 减小噪声干扰:噪声干扰会干扰锁相环的输出,从而导致无法锁定输入信号。因此,我们可以采取一些措施来减小噪声干扰。例如,可以在输入端添加低通滤波器来减小高频噪声的影响;可以在锁相环输入端添加限幅电路来避免输入信号过大,从而减小噪声的影响。

3. 改变锁相环的工作模式:根据不同的应用场合,可以选择合适的锁相环工作模式。例如,当输入信号频率变化较快时,可以考虑使用自适应锁相环,它能够快速适应频率变化。当输入信号存在周期性扰动时,可以考虑使用数字锁相环,它能够更加精确地跟踪信号的相位和频率。

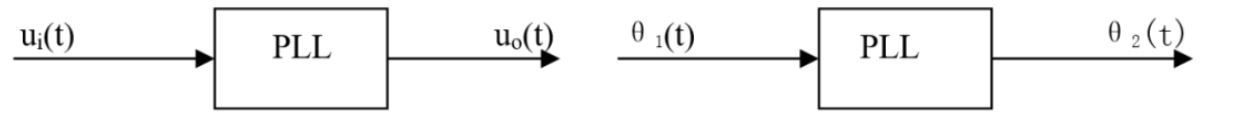

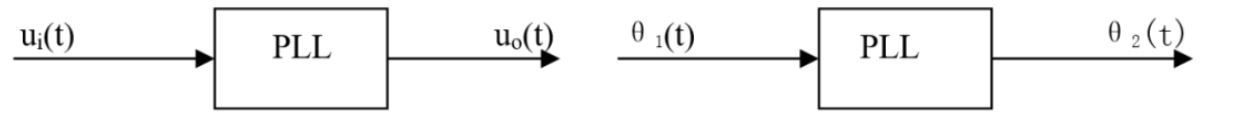

此外,还可以通过增加锁相环的阶数来提高精度。多级锁相环的输出频率精度比单级锁相环更高。然而,增加锁相环的阶数会增加复杂性,并且需要更多的时间来稳定输出信号。

总之,锁相环在频率突变时无法锁定输入信号是一个普遍存在的问题。通过充分理解锁相环的原理和特点,并采取相应的措施,我们可以更好地解决这个问题,提高锁相环的稳定性和可靠性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

锁相环PLL在无线电中的应用 1. 频率合成 在无线电通信中,频率合成是生成所需频率信号的关键技

![的头像]() 发表于

发表于 11-06 10:49

•150次阅读

锁相环(Phase-Locked Loop,简称PLL)是一种电子电路,它能够自动调整输出信号的相位,使其与输入信号的相位同步。这种电路在电子工程领域有着广泛的应用,特别是在频率合成、

![的头像]() 发表于

发表于 11-06 10:42

•187次阅读

锁相环频率合成器(Phase-Locked Loop Frequency Synthesizer, PLLFS)是一种利用锁相环(Phase-Locked Loop, PLL)技术实现频率

![的头像]() 发表于

发表于 08-05 15:01

•481次阅读

我在配置AD9694的过程中发现AD9694的采样率对应的线速率只有在6.75Gbps-13.5Gbps之间时,204b接口的锁相环才能锁定,现在想配置200M采样率,但是204B接口

发表于 07-03 06:18

我在配置AD9694的过程中遇到了AD9694输入时钟低于337.5MHz时,内部的serdes锁相环无法锁定的问题;但输入时钟高于337.5MHz时,如400M、600M就能

发表于 06-21 14:27

锁相环(Phase Locked Loop,简称PLL)是一种在电子系统中广泛应用的负反馈控制系统,其主要作用是实现输入信号与输出信号之间的相位同步。在现代通信、雷达、导航、测量等领域,锁相环

![的头像]() 发表于

发表于 05-24 16:28

•3267次阅读

锁相环锁定后一定不存在频差吗? 锁相环是一种常用的控制系统,用于将输入信号与参考信号之间的相位误差维持在一个可接受的范围内。它通过调节输出信号的相位和

![的头像]() 发表于

发表于 01-31 15:25

•715次阅读

方式有时会导致一些误解,有人认为它实际上是锁频而非锁相。在本文中,我将详细解释为什么锁相环既是锁频又是锁相,并解释两者之间的区别。 首先,让我们了解一下锁频和

![的头像]() 发表于

发表于 01-31 15:25

•1711次阅读

,也称为追踪带。它的主要功能是锁定输入信号与VCO(电压控制振荡器)输出信号的相位,使输出信号与输入信号保持相位一致。 - 锁相环捕获带:捕获带是锁相环的另一种工作模式,也称为拉住带。它的主要功能是

![的头像]() 发表于

发表于 01-31 11:31

•1047次阅读

的实时处理能力。数字锁相环广泛应用于物理和工程领域,包括用于测量和跟踪信号频率、提取原始信号的给定频率分量并在同时消除噪声和杂散分量,或者基于输入信号合成新信号。此外,数字锁相环

![的头像]() 发表于

发表于 01-02 17:20

•1845次阅读

10110111,reg10配置为11100000。锁定指示一直不能拉高,锁相环无法锁定,芯片不工作。检查了参考时钟,共模电压为400mv,vpp为900mv,时钟质量没有问题。

发表于 12-04 08:29

锁相环是一种 反馈系统 ,其中电压控制振荡器和相位比较器相互连接,使得振荡器频率(相位)可以准确跟踪施加的频率或相位调制信号的频率。锁相环可

![的头像]() 发表于

发表于 11-30 15:01

•2356次阅读

锁相环技术解析(上)

![的头像]() 发表于

发表于 11-29 16:51

•1067次阅读

锁相环技术解析(下)

![的头像]() 发表于

发表于 11-29 16:39

•919次阅读

电子发烧友网站提供《锁相环基本结构及原理.pdf》资料免费下载

发表于 11-29 11:23

•2次下载

软件锁相环在频率突变时锁不住 锁相环无法锁定怎么办?

软件锁相环在频率突变时锁不住 锁相环无法锁定怎么办?

评论