在电路设计过程中,应用工程师往往会忽略印刷电路板 (PCB)的布局 。一个常见的问题是电路原理图是正确的,但它不起作用,或者只能在低性能下运行。我将向您展示如何正确布置运算放大器的电路板以确保其功能、性能和稳健性。

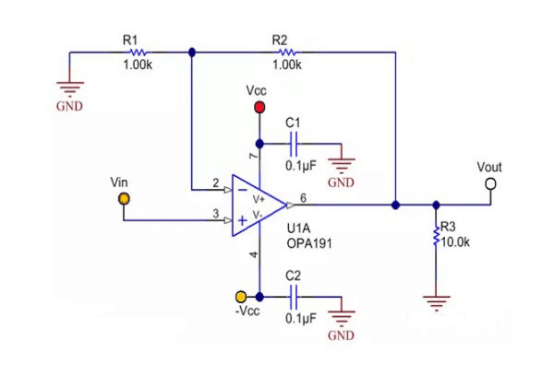

最近,我与一名实习生一起研究了增益为2V/V、负载为10kΩ、电源电压为+/-15V的同相配置OPA191运算放大器。图1显示了设计的原理图。

图1:具有同相配置的OPA191原理图OPA191原理图

我让实习生为设计做布板,同时给了他关于PCB布局的一般指导(例如:尽量减少电路板的走线路径,尽量保持元件排列紧密,以减少电路板占用空间) )空间),然后让他自己设计。设计过程有多难?其实就是几个电阻电容而已,不是吗?图2显示了他最初尝试设计的布局。红线是到板子顶部的路径,蓝线是底部路径。

图 2:第一次布局尝试

看到他的第一次布局尝试,我意识到电路板布局并不像我想象的那么直观;我至少应该给他做一些更详细的指导。他在设计上完全遵循了我的建议:缩短布线路径并将零件紧密地放在一起。但是,为了降低电路板的寄生阻抗并优化其性能,这种布局仍有很大的改进空间。

下一步是改进布局。我们所做的第一个改进是将电阻器R1和R2移到OPA191的反相引脚(引脚 2);这有助于减少反相引脚的杂散电容。运算放大器的反相引脚是一个高阻抗节点,因此具有高灵敏度。较长的走线路径可用作将高频噪声耦合到信号链中的导线。反相引脚上的PCB电容会导致稳定性问题。因此,反相引脚上的触点应尽可能小。

将R1和R2移至引脚2允许负载电阻器R3旋转180度,从而使去耦电容器C1更靠近 OPA191的正电源引脚(引脚 7)。去耦电容尽可能靠近电源引脚非常重要。如果去耦电容和电源引脚之间的走线路径很长,电源引脚的电感会增加,从而降低性能。

图 3:改进布局各部分的位置

将零件移动到新位置后,您仍然可以进行一些其他改进。您可以加宽走线路径以降低电感,这相当于走线路径所连接的焊盘的尺寸。还可以对电路板的顶部和底部接地层进行灌注,从而为返回电流创建可靠的低阻抗路径。图4显示了我们的最终布局。

图4:最终布局

下次布局印刷电路板时,建议您遵循以下布局约定:

- 尽量减少反相引脚的连接。

- 将去耦电容尽可能靠近电源引脚放置。

- 如果使用多个去耦电容,请将最小的去耦电容放置在最靠近电源引脚的位置。

- 不要在去耦电容和电源引脚之间放置过孔。

- 尽可能扩展路由路径。

在上文中,我们谈到了仪表放大器(运放)PCB 的正确布局方式,并提供了一系列良好的布局实践以供参考。接下来,我们将探讨布置仪表放大器 (INA) 时的常见错误,然后展示如何正确布置INA PCB。

INA 用于需要放大差分电压的应用,例如在高端电流检测应用中测量分流电阻器两端的电压。图5显示了典型的单电源高侧电流检测电路的原理图。

图5:高端电流检测原理图

图5通过RSHUNT测量差分电压,R1、R2、C1、C2和C3用于提供共模和差模滤波,R3和C4为U1 INA提供输出滤波,U2用于缓冲INA参考引脚. R4和C5用于形成一个低通滤波器,大限度地减少由运算放大器引入到INA参考引脚的噪声。

虽然图5中的原理图布局看起来很直观,但在PCB布局中很容易出错,导致电路性能降低。图6显示了工作人员在检查 INA 布局时常见的三个错误。

图 6:INA通用PCB布局

从上图可以看出,第一个误差是通过电阻测量差分电压Rshunt。可以看出Rshunt to R2线较短,因此其电阻小于Rshunt to R1线电阻。线路阻抗的这种差异可能会将输入偏置电流引入 INA,从而在U1输入侧产生差分电压。由于INA的任务是放大差分电压,输入侧的不平衡线路可能会导致错误。因此,需要保证INA输入线是平衡的,并且尽可能短。

第二个误差与INA增益设置电阻Rgain有关。U1引脚到Rgain焊盘的长度比实际需要的长度要长,因此会产生额外的电阻和电容。由于增益取决于INA增益设置引脚、引脚1和引脚8之间的电阻,因此额外的电阻可能会带来错误的目标增益。由于INA的增益设置引脚连接到INA中的反馈部分,额外的电容可能会导致稳定性问题。因此,确保连接增益设置电阻的线路尽可能短。

然后,可能需要改进缓冲电路参考引脚的位置。参考引脚缓冲电路远离参考引脚,这可能会增加参考引脚的电阻,导致噪声或其他信号耦合到线路中。参考引脚上的额外电阻可能会降低大多数INA提供的高共模抑制比 (CMRR)。因此,参考引脚缓冲电路应尽可能靠近INA参考引脚放置。

图7显示了纠正这三种错误后的布局。

在图7中,可以看到R1和R2到分流电阻器的线长相同,并且使用了开尔文连接。INA引脚的增益设置电阻尽可能短,基准缓冲电路尽可能靠近基准引脚。

如果您想在未来为INA布置PCB,请务必遵循以下指南:

1、确保输入端所有线路完全平衡;

- 减少线路长度并最小化增益设置引脚上的电容;

- 将参考缓冲电路布置在尽可能靠近INA参考引脚的位置;

4、去耦电容尽量靠近电源引脚布置;

- 至少覆盖一层实心地平面;

6.不要为了电子元件使用丝印而牺牲良好的布局 ;

- 遵循本文第一部分中提到的准则。

-

电路板

+关注

关注

140文章

5344浏览量

108963 -

运算放大器

+关注

关注

218文章

6462浏览量

181875 -

PCB

+关注

关注

1文章

2347浏览量

13204

发布评论请先 登录

BDS/GPS/GNSS 低噪声放大器 skyworksinc

1710-1950 MHz 可变增益放大器 skyworksinc

695 至 866 MHz 可变增益放大器 skyworksinc

2110-2170 MHz 可变增益放大器 skyworksinc

2620-2690 MHz 可变增益放大器 skyworksinc

791 至 821 MHz 可变增益放大器 skyworksinc

2.4 GHz 功率放大器 skyworksinc

1 GHz CATV 线路放大器 MMIC skyworksinc

InGaP 级联放大器 0.1–6 GHz skyworksinc

0.1 -7 GHz InGaP 级联放大器 skyworksinc

带步进衰减器的反向放大器 skyworksinc

线性放大器 skyworksinc

1.2 GHz CATV 线路放大器 MMIC skyworksinc

750/860 MHz CATV 线路放大器 MMIC skyworksinc

放大器PCB的接线技巧

放大器PCB的接线技巧

评论