我们从物理学中知道,自然界有四种基本力。它们是强核力(结合中子和质子)、弱核力(允许放射性衰变)、重力(赋予物体重量或拉向更大的吸引物体)和电磁力(这是磁引力)带电粒子之间)。在许多情况下,这种具有电和磁特性的吸引力是有利的。例如,磁性元件用于促进电机中转子周围的定子运动。然而,在其他情况下,这种自然产生的力可能会对所需的电路操作造成严重问题。

所有电子电路板都旨在允许甚至加强电子流以实现某些性能目标。这个动作——电流通过闭合路径——产生一个向外投射并垂直于电流流动的磁场。当该场内有附近的电子元件或信号路径时,就会发生电磁干扰(EMI)。对于许多 PCBA设计,尤其是高速电路板,控制 EMI 量是必须充分管理的首要考虑因素。对于带有散热器分类组件的电路板,常见的方法是实施EMI 滤波器设计。 尽管滤波器是有效的,但作为电路板设计师,了解用于降低 EMI 的其他 PCB 设计指南是您可能必须经常使用的工具。

EMC 和 EMI:有什么区别?

大多数 PCBA 并不是产品中唯一的电子或电气设备。因此,在我们深入研究单板EMI 问题之前,对EMI 问题有一个宏观或系统级的了解是有帮助的。正如电磁能从单个组件、导体或迹线发出一样,它也会从电路板本身辐射到环境中;如果您以前没有,请将高斯计放在 PCB 附近,您将获得读数。当多个板靠近时,实现电磁兼容性或 EMC就变得很重要。

EMC 可以被认为是在电磁元件之间实现可接受的和谐或平衡,以便干扰量最小或至少足够低,不会显着妨碍正常操作。不幸的是,消除所有 EMI 尚不可能;但是,获得 EMC是。EMI 实际上是来自电磁源的任何干扰,通常是指单个 PCBA 上的干扰。这种分类足以调查问题,因为最小化电路板上和来自电路板的 EMI 有助于电路板工作环境的 EMC。

PCB EMI来自哪里?

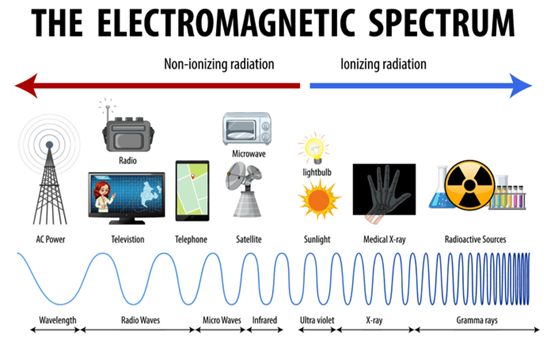

电磁跨越无限的频率范围,几乎无处不在。而且,如下图所示,它是由我们日常使用的许多工具、设备和产品产生的。

电磁频谱

只要有电流,就会存在 EMI 的可能性。对于 PCBA,EMI 的来源可分为以下几类之一:

成分

电子元件和元件——尤其是处理器、FPGA、放大器、发射器、天线等高功率设备——可能对 EMI 产生重大影响。此外,开关组件会产生具有破坏性的干扰。

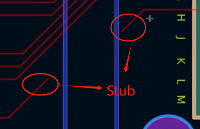

信号和轨迹

EMI 也可以沿着走线或在引脚和连接器点产生。例如,不平衡的差分对路由可能会导致信号衰减和沿传输路径的反射,这可能会严重影响信号完整性或准确识别信号的能力,从而导致错误的电路行为。此外,由于杂散电容,可能会在信号路径和接地层之间形成不需要的耦合。

外部来源

如果电路板太靠近辐射源(可能是另一个电路板或元件),EMI 可能会引入到您的 PCBA 上。其他设备或设备在电路板环境中的振动或移动也可能产生谐波。

显然,消除所有潜在的 EMI 来源是一项艰巨的任务。幸运的是,可以制定降低 EMI 的 PCB设计指南,以帮助最大限度地降低噪声和实现 EMC。

降低 EMI 的最佳 PCB设计指南

了解可能影响您的电路板的 EMI 来源对于制定策略以减轻这种对 PCBA 性能始终存在的威胁至关重要。此外,从源的角度来看 EMI,其中最小化方法针对特定的源,可以成为设计一套降低 EMI 的 PCB设计指南的良好有利位置。

降低组件的 EMI

如前所述,组件可能是 EM 辐射的主要来源,不仅会影响板载操作,还会破坏外部 PCBA 和电子电路。因此,定义减轻其负面影响的行动(如下所列)对于良好的 EMI 降低指南至关重要。

如何降低组件的 EMI

尽可能选择低功耗部件

电路板上最大的 EMI 发生器之一是需要大量功率的部件。随着降低功耗的推动,通常可以找到不会牺牲功能或质量的替代方案。

隔离不同类型的组件

一个好的设计实践是始终将处理相同类型信号的组件放在一起。例如,数字组件应该靠近其他数字部件并与模拟设备隔离。

利用 PCB围栏

另一种减轻 EMI 的工具是将元件或子电路封闭在围栏内;如PCB保护环和法拉第笼。这些也可以有效减少辐射到电路板周围的环境中。

采用散热技术

对于电子元件,能量会产生热量。因此,高效的散热器和通孔可以极大地帮助降低 EMI。

除了减轻组件的 EMI 之外,走线的运行方式也会极大地影响电路板的 EMI。

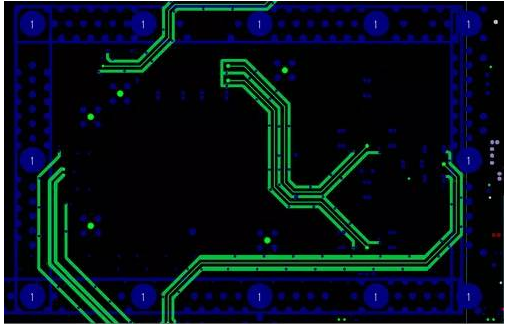

用于最小化 EMI 的 PCB布局设计

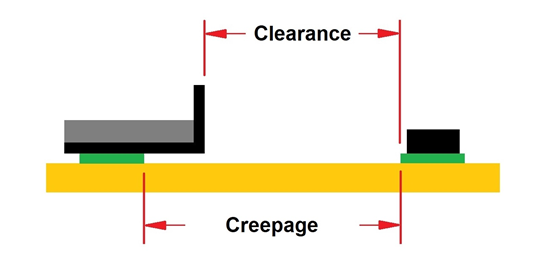

布置电路板时最重要的考虑因素之一是间距。这包括确保导电元件之间的间隙和爬电距离足够。

保持足够的间隙对于最大限度地减少 EMI 至关重要

对于多层板,导电层和接地层之间的顺序和距离也很重要,如下表所示。

如何减少来自信号和平面的 EMI

在信号走线之间留出足够的间隙

降低走线之间 EMI 的最重要因素是间距或间隙。遵循您的 CM 的建议,这些建议应该基于 IPC 标准。

确保去耦和旁路电容接地

杂散电容难以避免;然而,它的影响可以通过将电容器尽可能靠近引脚接地来减轻。

使用良好的 EMI 过滤

大多数设计,尤其是在使用数字信号的地方,都包含会产生信号失真的开关设备。在这些情况下,提高信号保真度的最佳方法是滤波。

最小化返回路径的长度

接地回路应尽可能短。

确保差分走线相同

对于差分信号路径,走线对必须相互镜像。这包括走线长度、铜重量和恒定间隔。如有必要,应使用曲折来保持长度和间隔。

避免锐角

布线时,请使用圆角边缘而不是尖角,这可能会由于特性阻抗修改而导致反射。

不要将导电层彼此相邻放置

您永远不应该在 PCB叠层中将两个导电层并排放置。最好通过地平面将它们分开。

小心分离地平面

最好为不同的信号类型使用单独的接地。但是,如果您确实使用分割地平面,请确保使用单个点来组合地面。

您的 PCB布局(包括其叠层)对于促进良好的信号完整性和降低 EMI非常重要。然而,如果不解决外部 EMI,任何一套降低 EMI 的 PCB设计指南都是不完整的。

避免外部 EMI

最大限度地减少外部 EMI 对电路板上的信号完整性和电路操作以及 PCBA 安装环境的 EMC 非常重要。可以采取的行动包括以下内容。

如何减少来自外部来源的 EMI

使用屏蔽

通常,屏蔽应用于特定组件或子电路。它们与围栏的不同之处在于它们通常由绝缘材料制成,并放置在零件的顶部或完全包围它们。

使用外壳

外壳通常被视为安全装置。然而,外壳也可以有效地保护电路板免受来自外部来源的碎片和 EMI 的影响。

上面针对组件、布局和外部源讨论的所有 PCB设计指南都可以有效地将电路板上的 EMI 降至最低,并有助于电路板操作环境的 EMC。但是,这些是否必要取决于您的设计、其功能和性能目标。因此,您应该努力优化您的设计以减少 EMI,最好使用分析工具(例如 Cadence 的 PSpice)来完成。

-

滤波器

+关注

关注

161文章

7846浏览量

178413 -

emi

+关注

关注

53文章

3593浏览量

127836 -

PCB

+关注

关注

1文章

1814浏览量

13204

发布评论请先 登录

相关推荐

高速PCB设计EMI防控手册:九大关键步骤详解

HDMI模块的PCB设计

高速PCB设计指南

专业PCB设计,高速PCB设计,PCB设计外包, PCB Layout,PCB Design,PCB画板公司,PCB设计公司,迅安通科技公司介绍

PCB设计中怎么降低EMC

PCB设计与PCB制板的紧密关系

PCB设计的EMC有哪些注意事项

这几招教你解决PCB设计中的电磁干扰(EMI)问题

多层pcb设计如何过孔的原理

DC电源模块的 PCB设计和布局指南

EMC之PCB设计技巧

降低EMI的最佳PCB设计指南

降低EMI的最佳PCB设计指南

评论