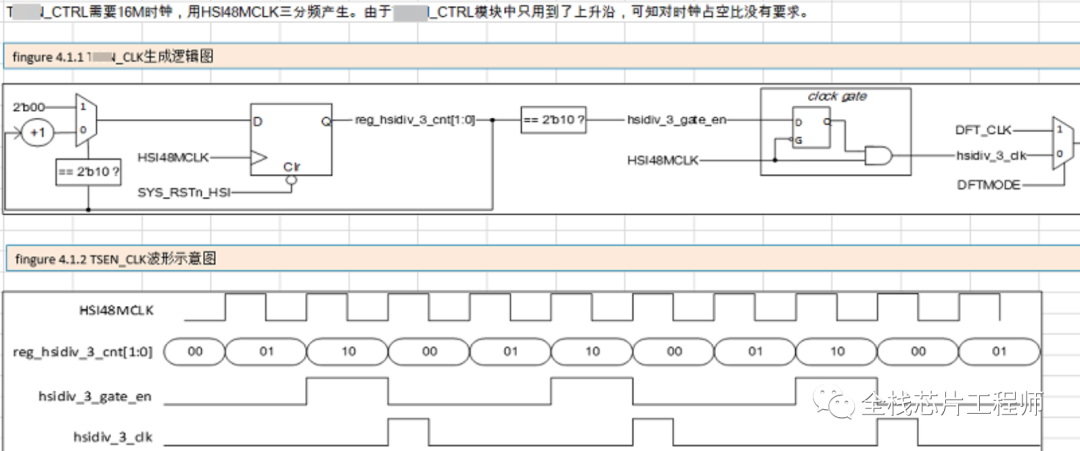

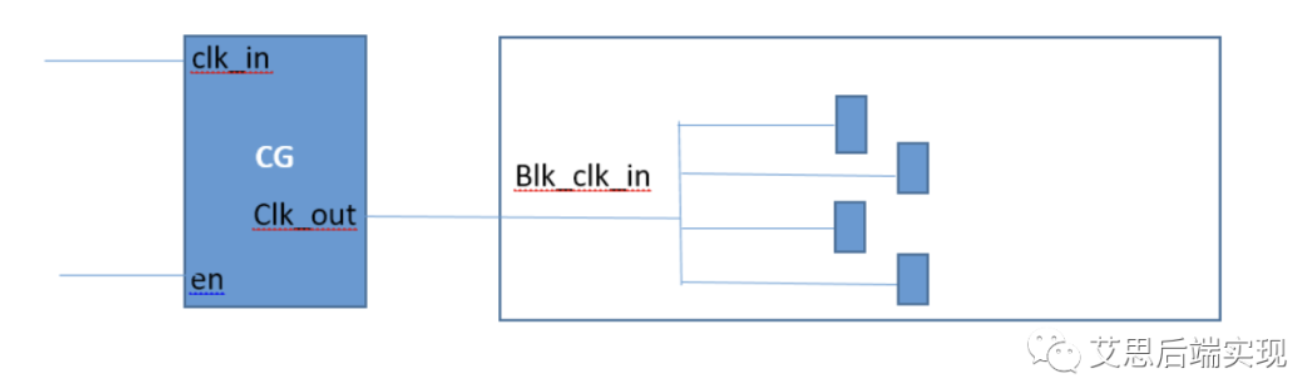

直接上硬菜,请问下面电路什么功能?

画出电路、画出波形,设计意图一目了然,笔者一直推荐这种设计方案风格,画出电路图、波形图绝对是设计辅助利器。

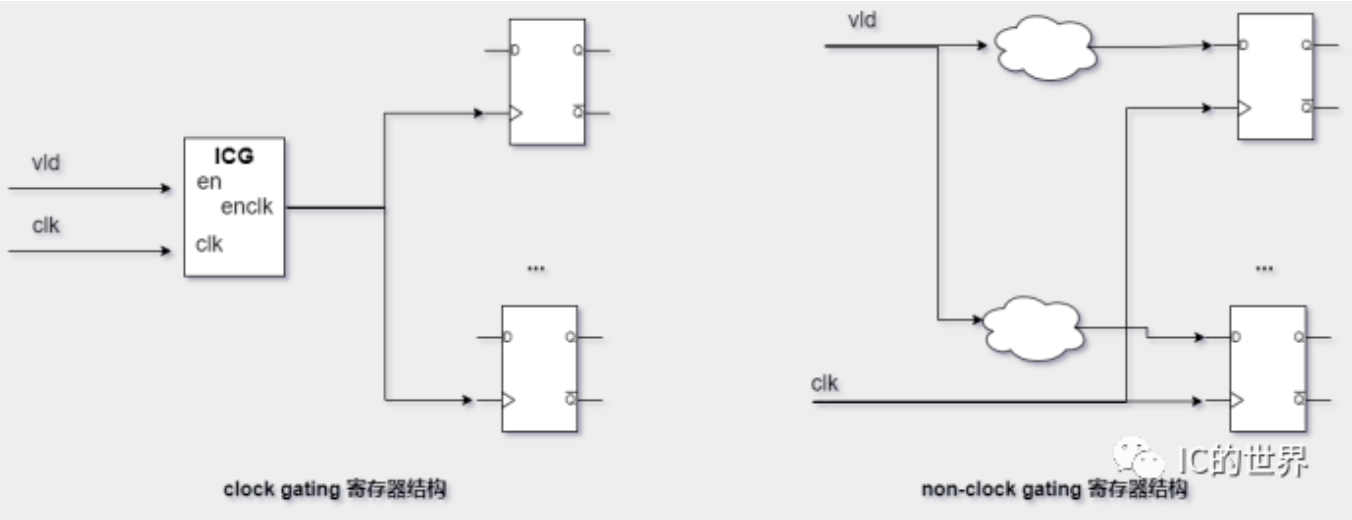

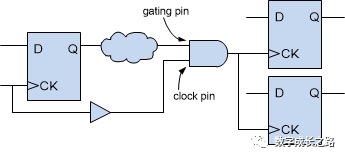

同学问,这个gate_en信号就已经是一个三分频信号了,图中这个clock gating 有什么用呢?

答:这个在景芯SoC培训里面专门讲过,虽然是三分频但是毕竟不是clock,只是reg的输出,驱动力不足,很少用这种三分频的信号去作为clock采数据。所以分频信号当EN信号用,接ICG的EN。

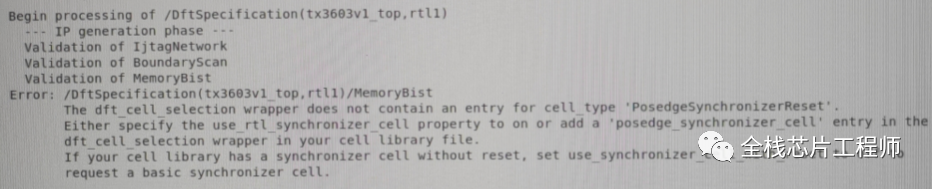

问:netlist flow第一步插mbist的时候报错说:

dft_cell_selection wrapper doesn't contain an entry for cell_type 'PosedgeSynchronizerReset',工艺库里面是没有这种cell的,这种情况该怎么处理?

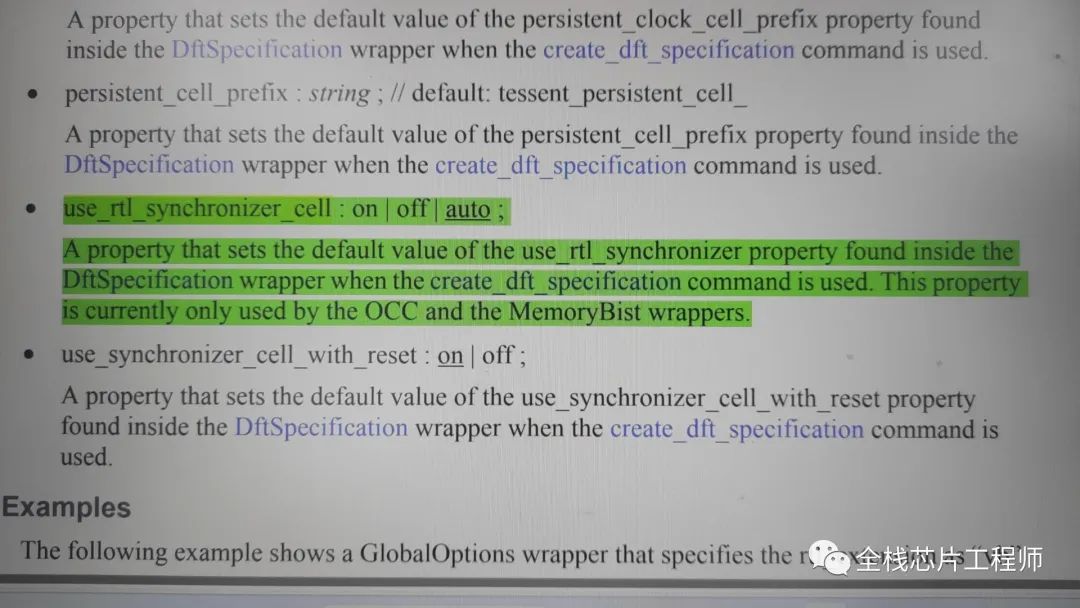

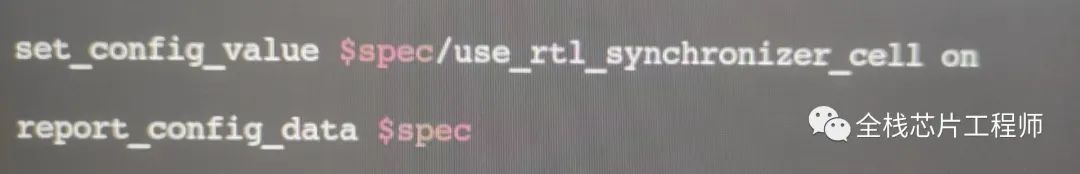

缺上升沿复位的同步器,如命令提示,我们直接将use_rtl_synchronizer_cell设置为on,默认是auto。

use_rtl_synchronizer_cell on

另外注意:

use_synchronizer_cell_with_reset on ,这个命令默认是on。

那么请问,netlist flow为何use_rtl_synchronizer_cell设置为auto就不行?

审核编辑:刘清

-

分频器

+关注

关注

43文章

447浏览量

50049 -

SoC芯片

+关注

关注

1文章

617浏览量

35023 -

同步器

+关注

关注

1文章

98浏览量

14692

原文标题:全流程学习SoC芯片设计【今日问题】

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

折叠屏幕有什么用

ASIC的clock gating在FPGA里面实现是什么结果呢?

gate_en信号中的clock gating有什么用呢?

gate_en信号中的clock gating有什么用呢?

评论