PG174中文文档简介

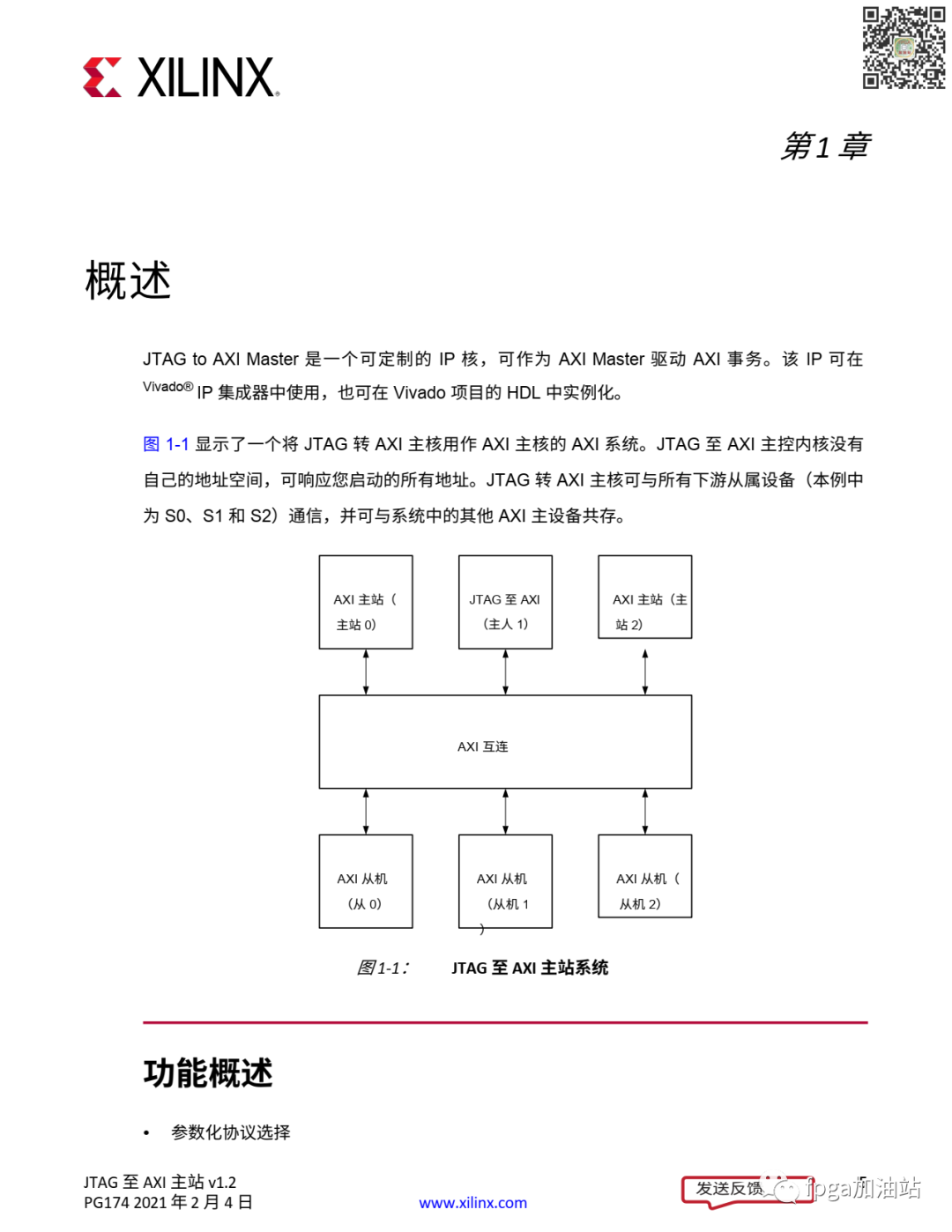

LogiCORE JTAG至AXI Master IP核是一个可定制的核,可生成AXIAXI总线可用于处理和驱动系统中FPGA内部的AXI信号。AXI总线接口协议可通过IP定制Vivado中的一个参数来选择。 集成设计环境(IDE)。AXI数据总线的宽度可定制。该IP可通过AXI4互连驱动AXI4-Lite或AXI4内存映射从站。运行时间与该内核的交互需要使用Vivado逻辑分析器功能。

特点

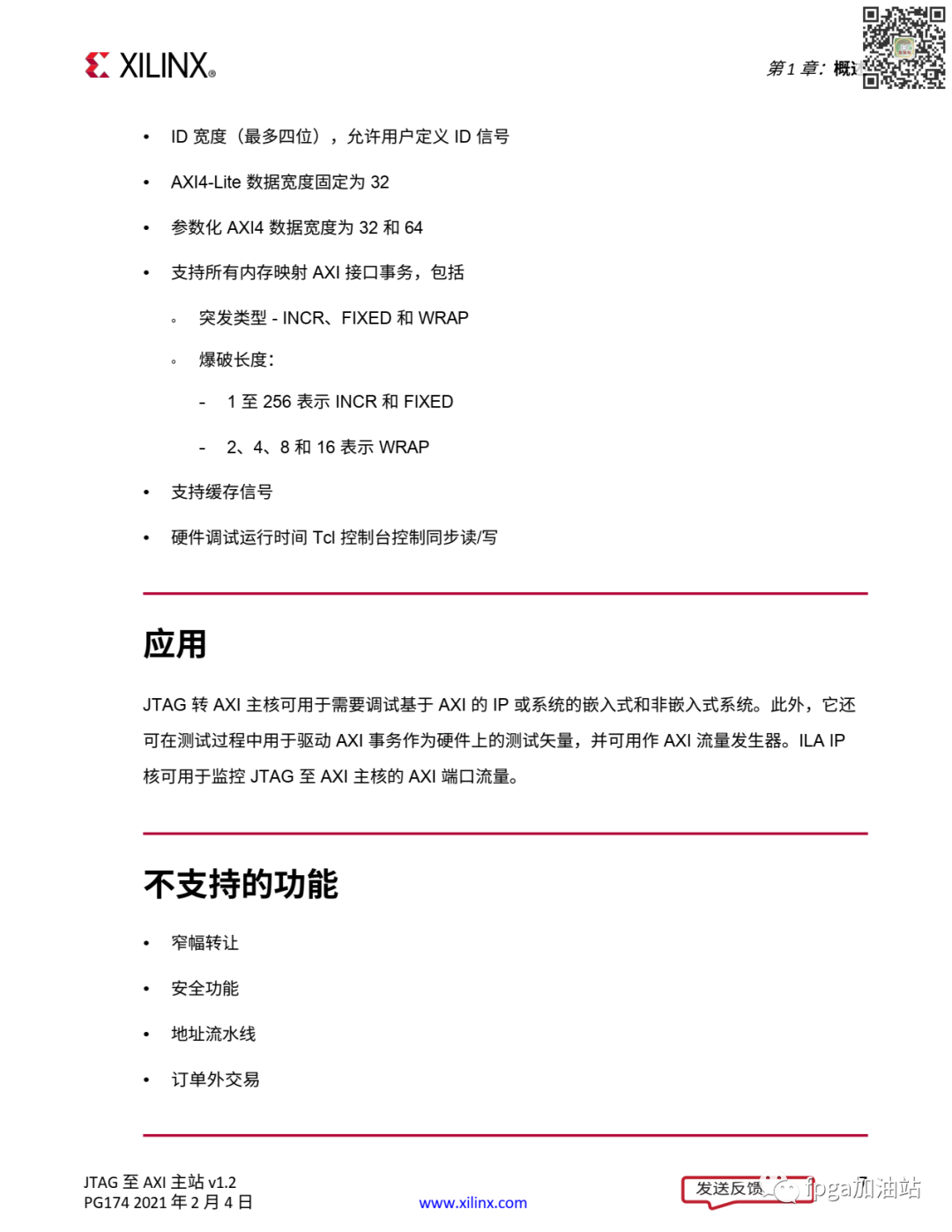

•提供AXI4主接口

•设置AXI4和AXI4-Lite接口的选项

•用户可选AXI数据宽度- 32和64

•用户可选AXI ID宽度,最多四位

•用户可选AXI地址宽度- 32和64

•与硬件交互的Vivado逻辑分析仪Tcl控制台界面

•支持AXI4和AXI4-Lite交易

PG174中文文档部分翻译预览

审核编辑:汤梓红

-

接口

+关注

关注

33文章

8573浏览量

151007 -

JTAG

+关注

关注

6文章

398浏览量

71673 -

IP核

+关注

关注

4文章

327浏览量

49485 -

AXI

+关注

关注

1文章

127浏览量

16622

原文标题:中文文档|PG174 JTAG to AXI Masterv1.2

文章出处:【微信号:fpga加油站,微信公众号:fpga加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

使用JTAG到AXI Master无法调试设计的解决办法?

FPGA——API函数实现JTAG to AXI Master的读写操作

Xilinx的LogiCORE IP Video In to AXI4

Xilinx Logicore IP直接数字合成器DDS的用户手册免费下载

如何使用MicroBlaze调用AXI IP核详细解析

AXI4-Stream Video 协议和AXI_VDMA的IP核介绍

Video In to AXI4-Stream IP核知识介绍

LogiCORE IP AXI4-Stream FIFO内核解决方案

LogiCORE IP AXI UART 16550内核简介

LogiCORE JTAG至AXI Master IP核简介

LogiCORE JTAG至AXI Master IP核简介

评论