Cadence Sigrity Aurora 分析的准确性如何?

答:Sigrity Aurora 仿真分析的准确性高度依赖于模型、输入信号、仿真环境和参数设置的准确性。准确的模型来描述Sigrity Aurora的特性和行为是保证仿真准确性的前提。

其次输入信号应该与实际应用中的信号相匹配,包括数据速率、幅度、时钟频率等。

再次,仿真环境应包括准确的电路拓扑、传输线线性和非线性特性、噪声、干扰等因素,以模拟实际的通信环境。

最后正确设置仿真参数和约束也是保证准确性的关键。例如,仿真时钟频率、仿真时间、仿真步长等参数需要根据具体应用和目标来选择和设置。确保这些因素准确可靠,并与实际应用情况相匹配,可以提高仿真分析的准确性。

此外,进行实际物理验证和测试也是评估仿真分析准确性的重要手段。

2

在 Allegro PCB 设计中,材料表格中找不到特定材料信息时,可以从哪些网站或论坛获取?

答:1. 电子元器件供应商网站:许多电子元器件供应商网站提供了详细的产品信息,包括材料参数、规格书、技术数据等。常见的供应商网站包括 Digi-Key、Mouser、RS Components、Farnell等。

2. PCB 设计社区和论坛:有许多专门讨论 PCB 设计的社区和论坛,例如 EEVblog、Electronics Stack Exchange、EEWeb 等。在这些社区中,可以向其他工程师和设计师提问,以获取关于特定材料的信息和建议。

3. 行业标准和规范:某些材料可能有行业标准和规范,其中包含了材料的详细说明和推荐。例如,IPC(Institute of Printed Circuits)制定了一些与 PCB 设计和制造相关的标准,可以查询相关资料了解更多关于材料的信息。

4. PCB 制造商和供应商:与 PCB 制造商和供应商联系,询问他们提供的材料选项和规格。他们通常会提供一份材料清单,涵盖了所提供的材料的特性和应用范围。

5. 学术研究文章和技术资料:学术研究文章和技术资料通常会提供关于特定材料的详细信息。可以通过学术数据库(如 IEEE Xplore、Google 学术搜索)和制造商的技术资料库来查找相关的论文和资料。

3

串扰分析除了应用 DDR 等并行相关领域,还有其他的应用场景吗?

答:1. 高速信号通信:在高速数字通信领域,如 PCIe、USB、Ethernet 等,串扰分析用于分析和评估通信线路中的信号串扰情况。在高速模拟信号传输系统中,如高频射频(RF)电路、模拟前端电路等,串扰分析用于评估信号间的相互干扰情况。串扰分析还可以用于评估时钟和同步信号传输线路中的相互干扰情况。通过对这些信号串扰进行仿真和分析,可以优化线路设计以提高数据传输质量,同时提高系统的灵敏度和可靠性。

2. 电源和地线布局:在电子系统中,电源和地线布局对于系统的稳定性和抗干扰性能有着重要影响。通过串扰分析,可以评估不同电源和地线布局方案对于系统中信号和电源的串扰情况,从而优化布局设计,提高系统的稳定性和抗干扰能力。

4

如何自制 IBIS 模型和 SPICE 模型?

答:

IBIS 模型自制:

收集芯片规格书和特性数据:包括输入/输出端口的电气特性、时序参数、电流/电压特性等。

数据预处理和格式转换:使用专业的仿真软件(如 Sigrity IBIS-AMI 模型创建工具)或脚本,将芯片的特性数据进行预处理和格式转换,生成符合 IBIS 模型标准的文本文件。

创建 IBIS 模型文件:使用 IBIS 模型编辑工具,将预处理的特性数据输入到相应的字段中,以创建 IBIS 模型文件。

模型验证和仿真:验证所创建的 IBIS 模型与芯片规格书中的数据是否一致,并使用仿真工具或 IBIS 模型验证工具进行仿真验证。

SPICE 模型自制:

获取芯片的物理特性:包括芯片的物理特性、电气参数、材料属性等信息。

提取模型参数:通过实验和测量(如 DC 测试、AC 测试和时间域测量),测量芯片的特性曲线并提取模型参数。这些参数可以是电流-电压关系、信号传输特性、电容、电感、阻抗等。

创建 SPICE 模型文件:使用 SPICE 模型编辑工具(如 PSpice 或 HSPICE)或文本编辑器,将提取的模型参数和特性输入到相应的 SPICE 模型代码中,以创建 SPICE模 型文件。

模型验证和仿真:验证所创建的 SPICE 模型与实际芯片的特性是否一致,并使用 SPICE 仿真工具进行电路仿真和验证。

5

除了系统模型,更改系统会影响原来的仿真结果吗?可否重新复制一份进行更改,原来的模型则继续保持?

答:在仿真中,IBIS 模型,及 SPCIE 模型更改系统的模型会影响原来的仿真结果。若更改系统模型并重新运行仿真,原来的模型将不再被使用,仿真将按照新的模型进行计算和分析。因此,更改系统模型可能会导致之前的仿真结果无效或不适用。

如果想保留原来的模型和仿真结果,并同时使用新的模型进行仿真,一种可能的方法是创建副本或多个仿真环境。可以将原始系统模型复制一份,并进行相应的更改,在复制的模型中使用新的参数或特性。然后,可以同时运行两个或多个仿真环境,分别基于原始模型和更改后的模型进行仿真比较。

请注意,需要确保在更改模型和创建复件时,修改的是独立的模型文件和仿真环境,以免影响到原始模型和仿真结果。此外,还应该对新模型的准确性和可靠性进行验证,并根据具体情况进行仿真结果的解读和比较。

6

直播中使用的 IBIS 模型是否大多需要自己编写?

答:IBIS 模型一般是由芯片制造商开发和提供的。在实际应用中,对于一些常见和常用的芯片,如处理器、存储器、接口芯片等,芯片制造商通常会提供与其产品配套的 IBIS 模型。这些模型包含了芯片的电气特性、时序参数等信息,且经过制造商的验证和测试,能够较为准确地反映芯片的行为,以便用户在系统级仿真中使用。

然而,对于一些特殊或新型的芯片,可能需要自己编写或修改 IBIS 模型来适应特定的仿真需求。编写或修改 IBIS 模型需要对 IBIS 标准及相关仿真方法和技术有一定的了解。如果缺乏相关经验或知识,建议咨询芯片制造商或第三方模型供应商,以获取合适的模型文件。当然,也可以通过公众号留言或发送邮件至 spb_china@cadence.com 联系李老师,李老师在编写 IBIS 方面有较多的经验。

7

串扰结果的大小的标准是什么,该如何判断是否合适?

答:信号串扰的大小通常通过指标来衡量,其中最常用的指标是峰-峰值(P-P值)和零-峰值(Z-P值)。峰-峰值指标是指信号串扰时信号的高点和低点之间的差值。这个指标用来评估串扰信号对目标信号的干扰程度。峰-峰值越大,表示串扰越强。

零-峰值指标是指串扰信号对目标信号的平均值和峰值之间的差值。这个指标用来评估串扰信号对目标信号平均值的偏移程度。零-峰值越大,表示串扰越严重。

判断信号串扰是否合适主要取决于具体的设计要求和应用场景。一般来说,工程师通常需要根据系统需求和设计目标来评估信号串扰的合适程度,如果信号串扰超过了系统设计规范或对目标信号的影响达到不可接受的程度,就需要采取相应的措施来降低串扰。

8

不同型号 DDR 的模型差异大吗?

答:不同型号的 DDR(双数据速率)模型在电气特性和时序参数上有很大的差异。DDR 模型的电气特性主要包括驱动和负载模型、恒压源模型、信号传输线模型等。时序参数是描述 DDR 芯片工作时序的重要指标,包括时钟频率、延迟时间、持续时间、信号传输延迟等。不同型号的 DDR 芯片具有不同的架构、芯片制造工艺和性能,因此其电气特性和时序参数也会有所不同。在使用 DDR 模型进行系统级仿真和设计时,应该选择适用于具体 DDR 芯片型号的模型,以确保仿真和设计的准确性和可靠性。

-

仿真

+关注

关注

50文章

4124浏览量

133916 -

信号

+关注

关注

11文章

2804浏览量

77046 -

网络拓扑

+关注

关注

0文章

104浏览量

11444

发布评论请先 登录

相关推荐

怎么样尽量降低ADC122s021两路之间的串扰问题?

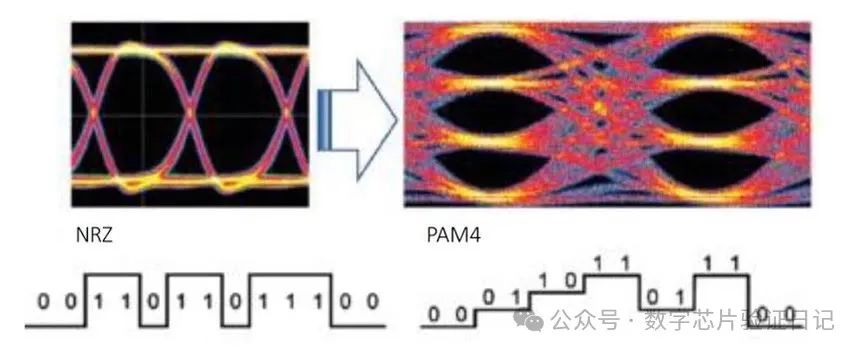

信号完整性分析中的眼图介绍

ADC电路的串扰怎么解决?

OptiSystem与OptiSPICE的联合使用:收发机电路的眼图分析

高频电路设计中的串扰问题

一般是需要在信号链路输入和输出作阻抗匹配,请问有没有必要像图上那样信号传输的每级都做阻抗匹配?

嵌入式开发中引起串扰的原因是什么?

信号阻抗、串扰、关键网络拓扑链路与眼图仿真分析实例技巧

信号阻抗、串扰、关键网络拓扑链路与眼图仿真分析实例技巧

评论