PG066中文文档简介

概述

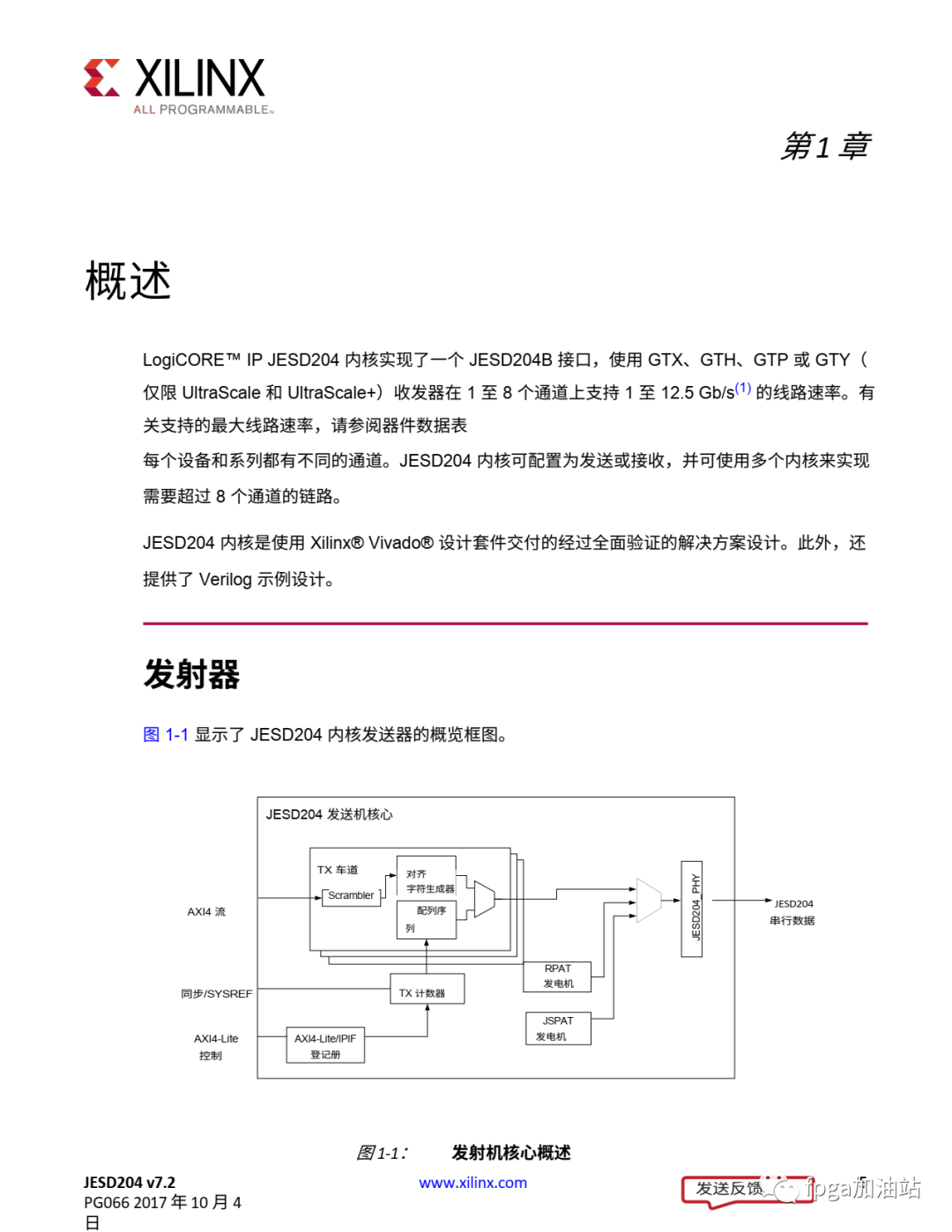

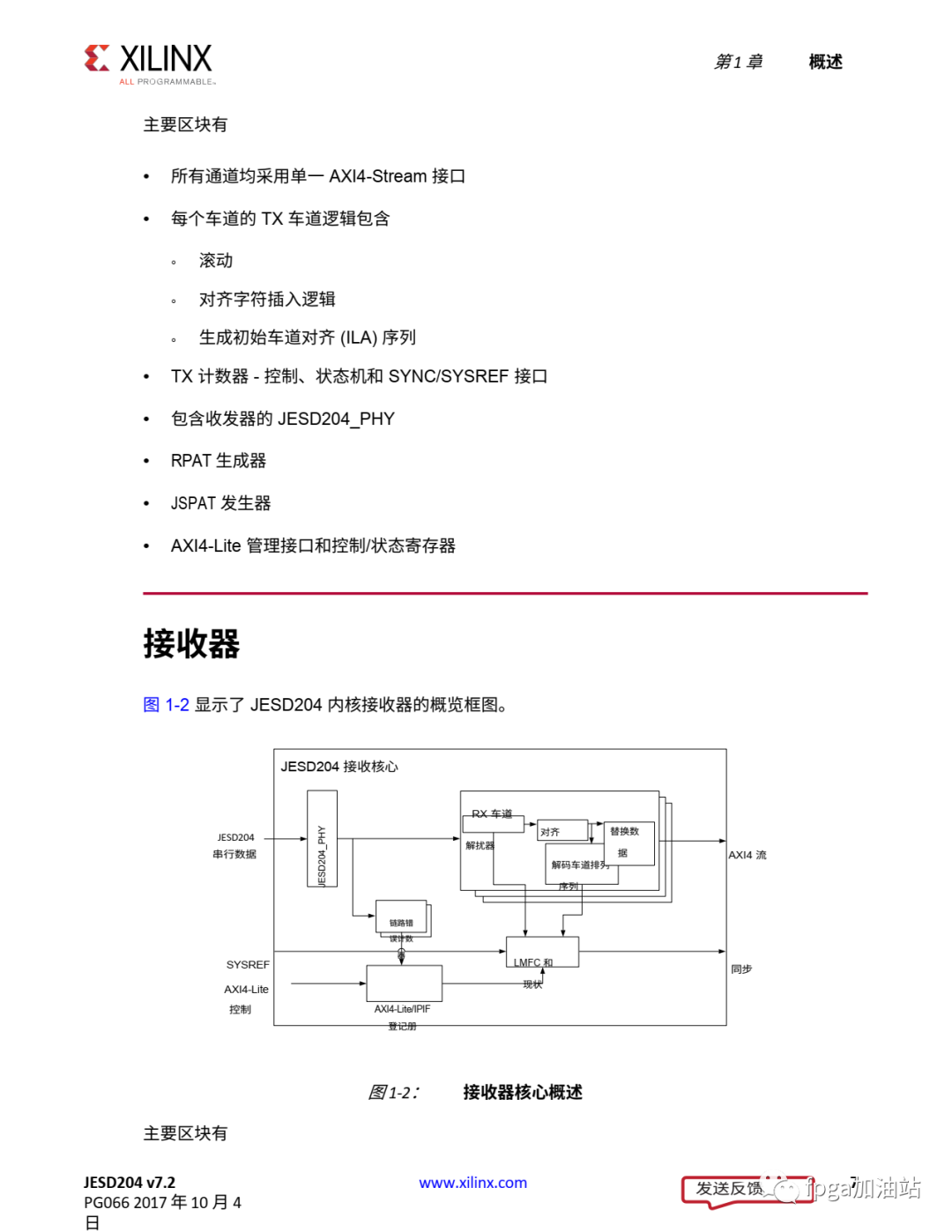

LogiCORE IP JESD204内核实现了一个JESD204B接口,使用GTX、GTH、GTP或GTY(仅限UltraScale和UltraScale+)收发器在1至8个通道上支持1至12.5 Gb/s(1)的线路速率。有关支持的最大线路速率,请参阅器件数据表。 每个设备和系列都有不同的通道。JESD204内核可配置为发送或接收,并可使用多个内核来实现需要超过8个通道的链路。JESD204内核是使用Xilinx Vivado设计套件交付的经过全面验证的解决方案设计。此外,还提供了Verilog示例设计。

导言

Xilinx LogiCORE IP JESD204内核实现了JESD204B接口,支持1 Gb/s至12.5 Gb/s(1)的线路速率。JESD204内核可配置为发射器或

接收器(2)。

特点

•按照JEDEC JESD204B[参考文献1]设计

•每个内核最多支持8条通道,使用多个内核最多支持32条通道

•支持最初的车道排列

•支持扰频

•每个帧支持1-256个字节(3)

•每个多帧支持1-32个帧(3)

•支持子类0、1和2

•提供物理层和数据链路层功能

•AXI4-Lite配置接口[参考文献2]

•AXI4流数据接口[参考文献3]

•使用JESD204_PHY内核,支持TX和RX内核之间共享收发器

PG066中文文档部分翻译预览

审核编辑:汤梓红

-

接收器

+关注

关注

14文章

2456浏览量

71789 -

内核

+关注

关注

3文章

1362浏览量

40215 -

接口

+关注

关注

33文章

8486浏览量

150803 -

Xilinx

+关注

关注

71文章

2163浏览量

120970

原文标题:中文文档PG066 | JESD204 v7.2

文章出处:【微信号:fpga加油站,微信公众号:fpga加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

请问AD9683的引脚如何与zynq 7015芯片中的 JESD204 ip核端口对应相连?

在Xilinx FPGA上快速实现JESD204B

JESD204 v5.2约束使用生成的dcp构建逻辑计时失败

无法在Vivado 2013.4中为JESD204B v5.1生成比特流

JESD204不允许生成比特流

JESD204接口简介

JESD204标准解析

JESD204评估许可证问题

为什么JESD204内核不使用GTX通道绑定功能来对齐通道?

JESD204C标准值得注意的新特性

AD9683的引脚如何与zynq 7015芯片中的JESD204 ip核端口对应相连?

ADI公司和Xilinx联手实现JEDEC JESD204B互操作性

采用JESD204标准的高速串行接口的应用

JESD204——它是什么?

LogiCORE IP JESD204内核概述

LogiCORE IP JESD204内核概述

评论