PG016中文文档简介

Xilinx LogiCORE IP视频定时控制器内核是一款通用视频定时生成器和检测器。该内核可通过完整的寄存器集进行高度编程,从而控制各种定时生成参数。这种可编程性与一组全面的中断位相结合,可轻松集成到处理器系统中,实现对模块的实时系统控制。视频定时控制器提供一个可选的AXI4-Lite兼容接口。

特点

•支持最大16,384 x 16,384的逐行或交错视频帧尺寸

•输出定时信号的直接再生,具有独立的定时和极性反转功能

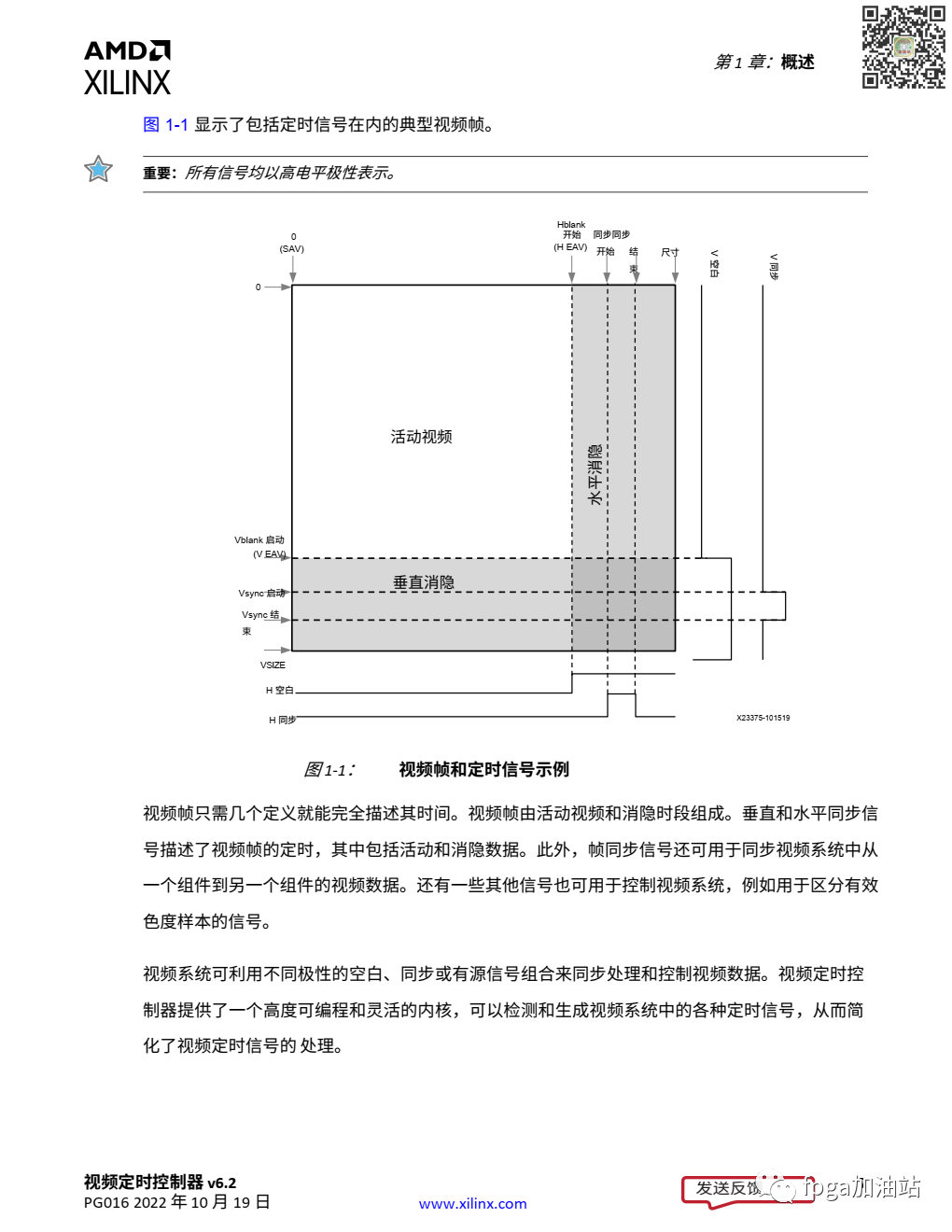

•自动检测并生成水平和垂直视频定时信号

•支持多种消隐或同步信号组合

•自动检测输入视频控制信号的极性

•支持检测和生成垂直空白/同步的水平延迟

•可编程输出视频信号极性

•生成多达16个额外的独立输出帧同步信号

•可选AXI4-Lite处理器接口

•中断和状态寄存器数量多,便于系统控制和集成

PG016中文文档部分翻译截图预览

审核编辑:汤梓红

-

控制器

+关注

关注

112文章

16346浏览量

177899 -

寄存器

+关注

关注

31文章

5342浏览量

120277 -

内核

+关注

关注

3文章

1372浏览量

40284 -

Xilinx

+关注

关注

71文章

2167浏览量

121343

原文标题:PG016| 视频定时控制器v6.2中文文档

文章出处:【微信号:fpga加油站,微信公众号:fpga加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx ISE中的DDR控制器是否有任何IP实现

Logicore IP CAN过滤问题

请问Xilinx区域的Opencore TDM控制器是否有相同的功能?

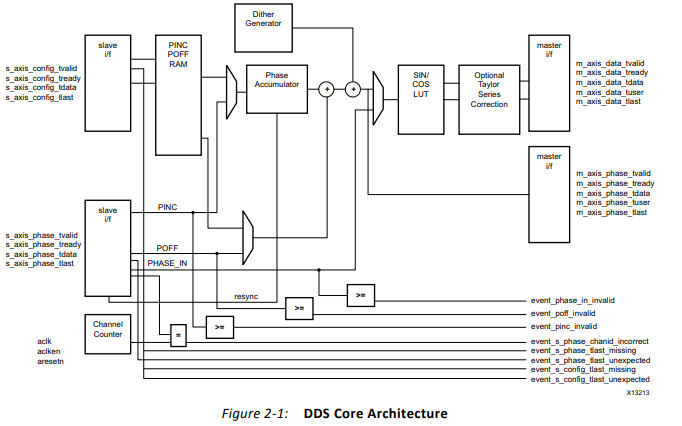

Xilinx Logicore IP直接数字合成器DDS的用户手册免费下载

Xilinx DDR控制器MIG IP核的例化及仿真

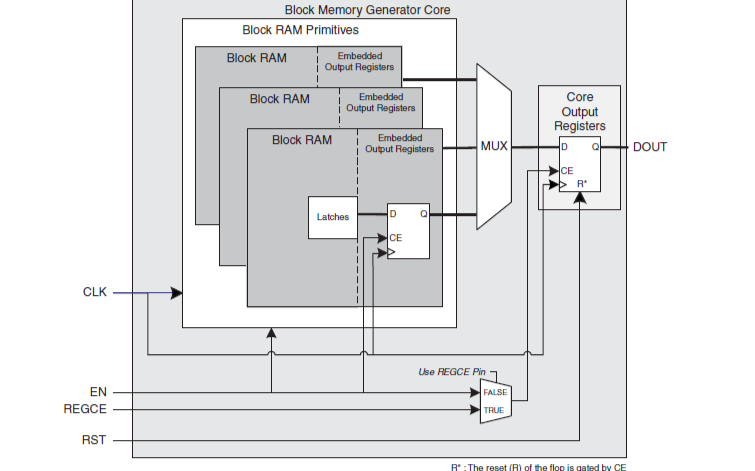

Xilinx LogiCORE IP块内存生成器的产品指南

LogiCORE™IP1G/2.5G以太网PCS/PMA文档简介

Versal ACAP收发器向导 LogiCORE IP产品指南

LogiCORE IP AXI4-Stream FIFO内核解决方案

LogiCORE IP JESD204内核概述

LogiCORE IP AXI UART 16550内核简介

Xilinx LogiCORE IP视频定时控制器内核简介

Xilinx LogiCORE IP视频定时控制器内核简介

评论