导语

在更小、更轻、更薄的消费产品趋势的推动下,越来越小的封装类型已经开发出来。事实上,封装已经成为在新设计中使用或放弃设备的关键决定因素。本文首先定义了“倒装芯片”和“芯片级封装”这两个术语,并阐述了晶圆级封装(WLP)技术的发展。接下来讨论了使用晶圆级封装器件的实际方面。讨论的主题包括:确定给定器件的倒装芯片/UCSP封装的可用性;通过其标记识别倒装芯片/UCSP;圆片级封装件的可靠性;寻找适用的可靠性信息。

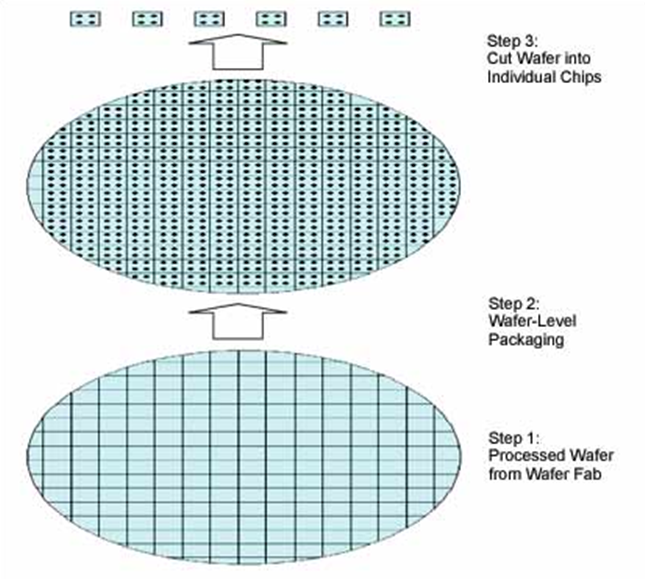

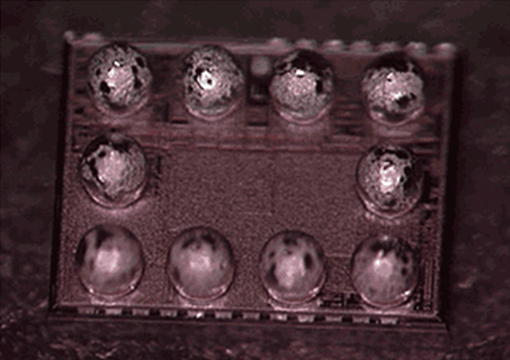

半导体技术的进步创造了具有晶体管数量和功能的芯片,这在几年前是不可想象的。如果没有IC封装同样令人兴奋的发展,我们今天所知道的便携式电子产品是不可能实现的。在更小、更轻、更薄的消费产品趋势的推动下,更小的封装类型已经被开发出来。最小的封装将永远是芯片本身的大小。图1说明了集成电路从晶圆到单个芯片的步骤。图2显示了一个实际的芯片级封装(CSP)。

芯片尺寸封装的概念在20世纪90年代发展起来。在1998年定义的CSP类别中,晶圆级CSP成为各种应用的经济选择,从低引脚数器件到ASIC和微处理器。CSP器件的制造过程称为晶圆级封装(WLP)。WLP的主要优点是所有封装制造和测试都是在晶圆上完成的。WLP的成本随着晶圆尺寸的增加和芯片的缩小而下降。

图1 晶圆级封装(简化)最终将单个芯片与加工过的晶圆分离

图2 一个12个凸起的芯片级封装,其中2个凸起位置未填充

#1命名的由来

Nomenclature

业界对WLP的命名仍然存在困惑。CSP的晶圆级方法是独特的,因为封装内部没有键合技术。进一步的困惑存在于如何称呼封装芯片。常用的描述性名称有:Flip Chip、CSP、芯片级封装、WLCSP、WL-CSP、Micro SMD、UCSP、凸模和Micro CSP。

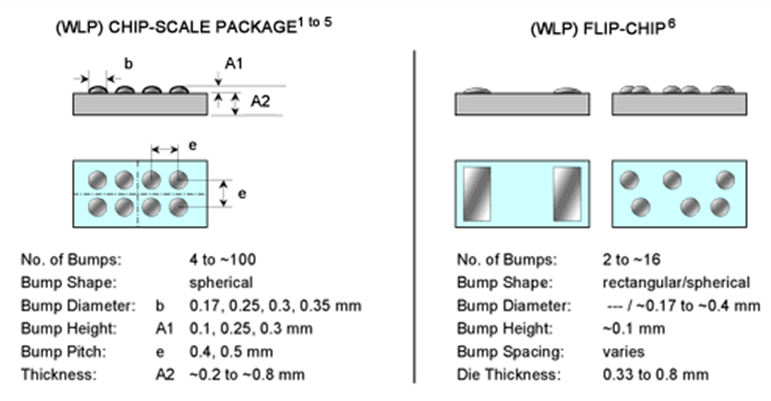

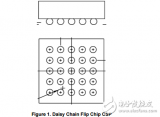

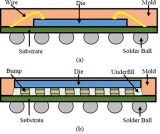

“倒装芯片”和“芯片级封装”最初是所有类型的晶圆级封装芯片的同义词。随着时间的推移,这二者之间的区别越来越明显。“倒装芯片”描述的是具有任何形状的凸点的晶圆级封装芯片,可以位于任何位置(与边缘有间隙)。而“芯片级封装”描述的是晶圆级封装芯片,其球形凸起位于具有预定义间距的网格上,图3说明了这些差异。

图3 显示芯片级封装和倒装芯片封装之间的典型尺寸和差异

#2晶圆级封装(WLP)技术

Wafer-Level Packaging (WLP) Technology

提供WLP零件的供应商要么有自己的WLP工厂,要么外包封装过程。因此,制造过程各不相同,用户必须满足的要求也各不相同,以确保最终产品的可靠性。

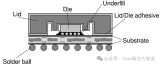

连接芯片到电路/配线板上的走线的凸起最初是由锡和铅的共晶合金(Sn63Pb37)制成的。减少电子产品中有害物质含量(RoHS)的举措迫使半导体行业采用替代品,例如无铅凸起(Sn96.5Ag3Cu0.5)或高铅凸起(Pb95Sn5)。每种合金都有自己的熔点,因此,在组件组装回流过程中需要特定的温度曲线(在特定温度下的持续时间)。

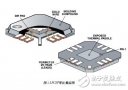

集成电路的设计是为了提供所需的所有电路功能,并适合一组特定的封装。芯片上的键合垫通过导线键合连接到传统封装的引脚上。传统封装的设计规则要求键合垫位于芯片的周长。为了避免同一芯片的两种设计(一种用于传统封装,另一种用于CSP),通常需要一个再分配层来连接凸起和键合垫。

#3设备标识

Device Identification

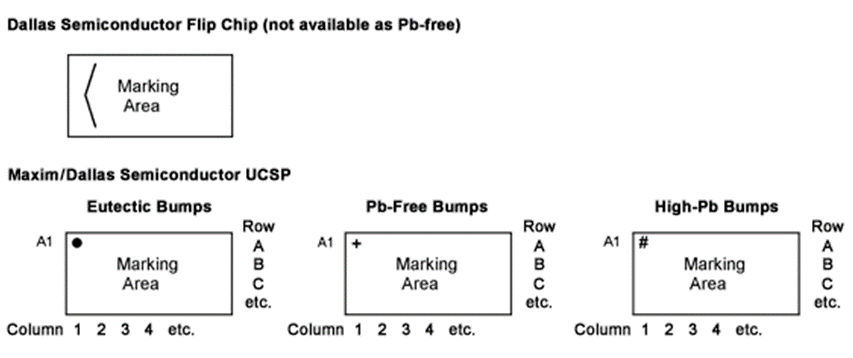

大多数倒装芯片和UCSP没有空间用于塑料封装常见的传统标记。最小的UCSP(4个凸起)有足够的空间来放置方向标记和分布在两行的6个字符的代码。方向标记还指示封装是“标准”(共晶凸起)、高铅(#)还是无铅(+),参见图4。

图4 倒装芯片和UCSP标记模板

一旦制造完成,TSV通常会留下轻微的锥度,其中结构底部的通孔更薄。较薄的区域由于其截面积较小,因此电流密度较大,因此电迁移更有可能首先发生在那里。结果会形成空洞,最终导致开路。一旦空洞开始形成,空洞也会成为应力集中的区域,并可能发生机械断裂。

#4晶圆级封装部件的可靠性

Reliability of Wafer-Level Packaged Parts

晶圆级封装(倒装芯片和UCSP)代表了一种独特的封装形式,通过传统的机械可靠性测试,其性能可能与封装产品不一样。封装的可靠性与用户的组装方法、电路板材料和使用环境密切相关。在考虑使用WLP零件时,应仔细审查这些问题。通过工作寿命测试和防潮性能保持不变,因为它主要由晶圆制造工艺决定。

机械应力性能是WLP更关注的问题。倒装芯片和UCSP通过直接焊接接触连接到用户的PC板上,因此放弃了封装产品引线框架的固有应力缓解。因此,必须考虑焊点接触完整性。

#5结论

Conclusion

如今,倒装芯片和CSP仍然是一种不断发展的新技术。正在进行的改进将应用背面层压涂层(BSL),保护模具的非活动面免受光和机械冲击,并提高在明光场照明下激光打标的可读性。随着BSL,应该期望减少模具厚度,以保持整体组装高度不变。此外,重要的是要知道凹凸模WLP的具体合金成分,特别是如果一个设备没有广告和标记为无铅。一些具有高铅凸起的器件(Pb95Sn5)已经用无铅电路板组装回流工艺进行了测试,发现其兼容性没有显著影响其可靠性。带有共晶SnPb凸起的器件需要类似的共晶SnPb焊膏,与无铅的组装环境并不兼容。 接下来,给各位推荐一个大型行业技术交流论坛。

8月17日第103届CEIA电子智造高峰论坛即将在南京隆重举办,聚焦集成电路、5G通讯模组、光电通信等领域,融合系统集成产业链,从微组装到先进封装,汇聚智造创新,洞察前沿新知,参会⑥重好礼,立即报名,抢占稀缺席位。

审核编辑:汤梓红

-

半导体

+关注

关注

339文章

31438浏览量

267423 -

封装

+关注

关注

128文章

9373浏览量

149173 -

晶体管

+关注

关注

78文章

10458浏览量

148865 -

倒装芯片

+关注

关注

1文章

124浏览量

16880

原文标题:什么是倒装芯片(Flip-Chip)和芯片级封装(Chip-Scale Package)?

文章出处:【微信号:CEIA电子智造,微信公众号:CEIA电子智造】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

倒装芯片CSP封装

倒装芯片和芯片级封装的由来

倒装芯片和芯片级封装的由来

评论