实验目的

实验任务

设计一个4位奇偶校验器电路。要求当输入的4位二进制码中有奇数个“1”时,输出为“1”,否则输出为“0”。

实验原理

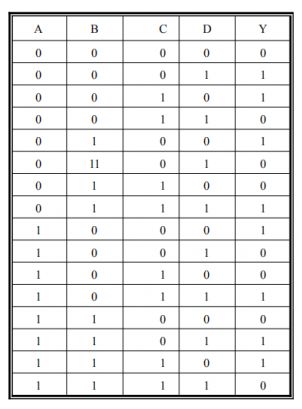

奇偶校验,即判断输入变量中1的个数。当输入变量中1的个数是奇数时,输出为1。当输入变量中1的个数是偶数时,输出为0。真值表及逻辑表达式如下所示:

Y=A’B’C’D+A’B’CD’+A’BC’D’+A’BCD+AB’C’D’+AB’CD+ABC’D+ABCD’

经过化简得到:Y=A⊕B⊕C⊕D

逻辑电路

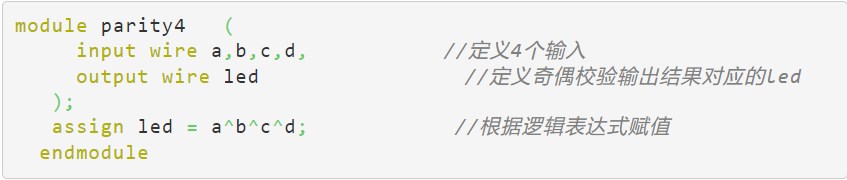

Verilog HDL建模描述

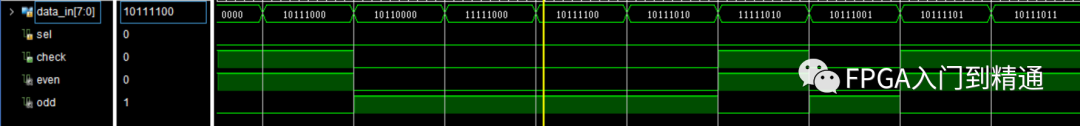

实验步骤

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

二进制

+关注

关注

2文章

794浏览量

41638 -

奇偶校验器

+关注

关注

0文章

7浏览量

7128 -

数字电路

+关注

关注

193文章

1605浏览量

80573 -

FPGA开发

+关注

关注

1文章

43浏览量

14909 -

HDL语言

+关注

关注

0文章

47浏览量

8913

发布评论请先 登录

相关推荐

UART中有奇偶校验位和无奇偶校验位的数据传输是怎样的?

例如,我使用 8 位数据传输类型。奇偶校验位共有 3 种类型无奇偶校验偶校验奇校验----------------------偶校验我假设

发表于 12-08 07:24

单片机串口分析起始位停止位奇偶校验位

串口解析串口配置1.波特率2.停止位3.数据位4.奇偶校验位比特率:通讯的频率停止位:可以选择1/1.5/2三个选择数据

发表于 11-20 10:36

•16次下载

增强FIFO模式下的奇偶校验

自昊芯推出专题讲解SCI串口通讯奇偶校验,分为两期讲解,上期主要讲解标准SCI模式下的奇偶校验,本期主要讲解增强FIFO模式下的奇偶校验。

FPGA奇偶校验的基本原理及实现方法

在数字电路中,数据的正确性非常重要。为了保证数据的正确性,在传输数据时需要添加一些冗余信息,以便在接收端进行校验。其中一种常用的校验方式是奇偶校验(Parity Check)。本文将介

什么是奇偶校验 奇偶校验的基本原理 奇偶校验电路什么意思

什么是奇偶校验 奇偶校验的基本原理 奇偶校验电路什么意思 奇偶校验是一种用于检测二进制数据中错误的方法。它的基本原理是在二进制数据的末尾添

什么是奇校验和偶校验?常见的奇偶校验方式有哪些?

什么是奇校验和偶校验?常见的奇偶校验方式有哪些? 1. 奇偶校验是指在数字通信中采用一种技术对传输的数据进行

奇偶校验和crc校验的区别 CRC校验和奇偶校验之间有什么关系?

方法都可以检测出特定类型的错误。 奇偶校验是一种简单的校验方法,适用于串行传输数据,主要用于检测传输中的单比特错误。其原理是通过添加一个校验位来使原始数据的奇偶性成为对称的,通过接收端

数字电路实验—4位奇偶校验器设计

数字电路实验—4位奇偶校验器设计

评论