本文主要介绍连接器金属外壳和金属外壳搭接不良对静电放电抗扰度测试的影响。

Part 1

现象描述

某产品在进行静电放电抗扰度测试时,当对产品中某PCB的DB连接器外壳(如下图所示)进行静电放电(-4KV 接触放电)时,出现系统复位的现象。

后来检查该DB连接器,发现该连接器的外壳没有和金属外壳形成良好的搭接,用导电胶将DB连接器与外壳良好搭接后,再进行测试(-6KV接触放电),工作正常,系统不再复位。

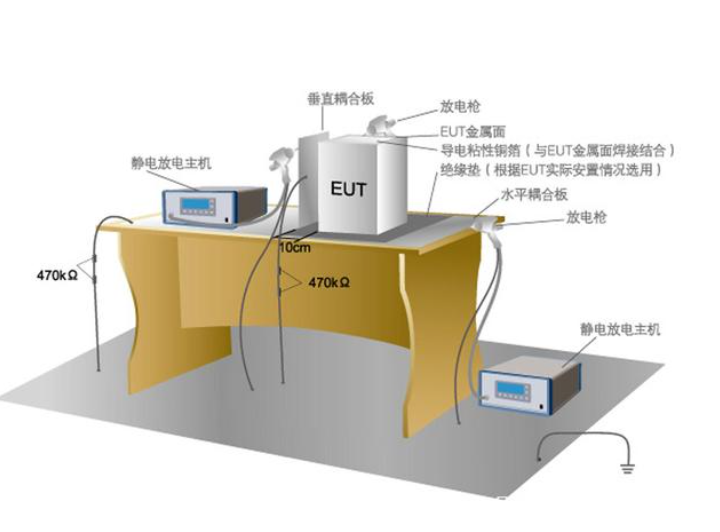

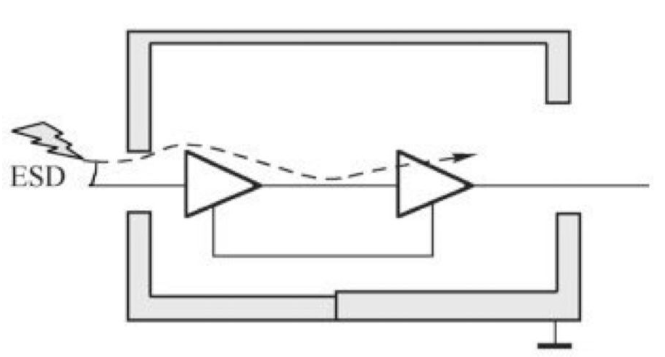

静电测试的示意图如下图所示,想要详细了解静电测试的实质的话可以参考我之前的文章《EMC 测试实质之ESD抗扰度》:

究竟是什么原因导致的呢?想要分析静电带来的问题时可以从下面几方面来考虑:

首先判断测试位置是连接器还是缝隙,连接器是金属的还是其它的材料的,产品外壳是金属还是其它材料。

如果是金属材料,分析产品是否接大地(也称为PE),如果是浮地系统,则看是否接了功能地。

查看金属连接器或者金属按键等是否和金属外壳搭接良好,金属外壳是否接大地。

总之,静电问题,一般都是接地不良或者金属搭接不良导致的。

Part 2

原因分析

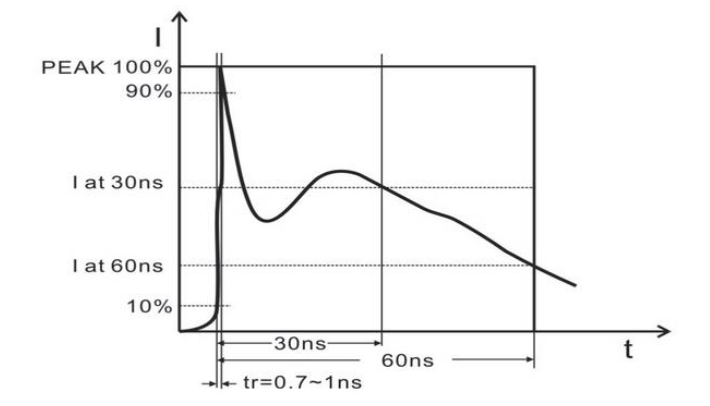

静电放电(如下图所示)是一种瞬态能量高,宽频谱的一种电磁骚扰 ,它主要通过以下两种途径来干扰EUT:

直接能量,瞬态的大电流导致内部电路损坏(如IC芯片的损坏,)或者电路出现错误(出现闩锁效应)。

空间耦合,由上图可知,ESD的前沿时间很短, 约 0.7-1ns, 其频谱范围可以达到数百MHz,所以稍微长一点的线缆,PCB中的微带线或带状线都可能形成有效的耦合。

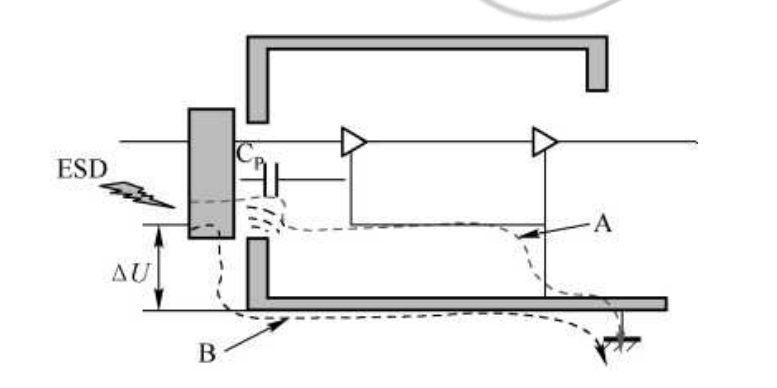

如前面所述,在测试中发现DB连接器的金属外壳和产品外壳之间有很明显的缝隙,从电路的角度来看,这个缝隙就等效为一个阻抗,在DB外壳上的静电放电电流(如图中虚线所示)的作用下,就会产生较高的压降ΔU

我们知道,在图中存在分布电容的地方有如下几个地方:

DB连接器外壳及机壳与内部电路的地平面

DB连接器外壳及机壳与信号线之间

其中DB连接器外壳及机壳与PCB中地平面之间的分布电容最大,如图中Cp所示,该分布电容在静电放电高频干扰的情况下影响也最大。

在 ΔU 存在的情况下,必然导致一部分静电放电电流经分布电容Cp流向地平面, 最后流向大地,如图中虚线 A 所示。

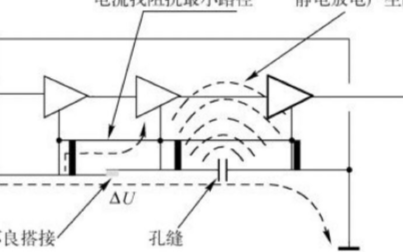

实际上,PCB中的地平面也并不是理想的地面,其并不完整(完整的地平面阻抗为3mΩ),存在一定的阻抗,因为一般地平面上一定有过孔,过孔的缝隙会导致阻抗不连续。

当干扰电流流经工作地平面时,由于阻抗的存在, 就会出现压降 ΔU1 , 而这个 ΔU1就是造成电路混乱的元凶。

另外,ΔU也是常常是引起辐射发射的超标的原因之一。

通过以上分析,我们可以认为,如果阻抗不连续,干扰信号就很难较快地泄放,这样就会通过分布电容耦合到内部电路,从而出现损坏或者内部电路混乱。

如果搭接良好,静电就会很快泄放到外壳上并导入到大地上(前提是外壳也接好大地)。

另外搭接良好,会使外壳具有更好的屏蔽效果,在静电泄放过程中产生的电磁场就会被屏蔽在外壳外部, 从而保证了内部电路的稳定。

Part 3

处理措施

为了保证DB连接器金属外壳与产品外壳良好搭接,可以将DB连接器通过螺钉固定在外壳上面,使 DB连接器与金属面板紧密连接。

从而保持了DB连接器外壳和金属外壳的电连续性。这样不仅能提高整机的屏蔽效能,还能使静电骚扰电流通过金属外壳很快地泄放掉, 问题得到了解决。

Part 4

思考和启示

经过上面的分析,我们可以得到如下启示:

防止静电干扰直接耦合进PCB的一个有效方法是将静电干扰信号通过导体直接接到大地上。

要保持静电放电点的阻抗连续。

-

pcb

+关注

关注

4317文章

22999浏览量

396204 -

连接器

+关注

关注

98文章

14306浏览量

136151 -

emc

+关注

关注

169文章

3872浏览量

182859

原文标题:EMC案例分析——连接器金属外壳搭接不良对静电放电抗扰度的影响

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

静电放电抗扰度测试方案-EMS测试系统

防水连接器金属与塑料连接器的区别

塑料外壳与金属外壳连接器对ESD的影响分析

分析塑料外壳连接器和金属外壳连接器对ESD测试的影响

EMC案例分析——连接器金属外壳搭接不良对静电放电抗扰度的影响

EMC案例分析——连接器金属外壳搭接不良对静电放电抗扰度的影响

评论