电子发烧友网报道(文/吴子鹏)近日,全球领先的商业RISC-V内核供应商SiFive宣布推出两款新产品,分别为SiFive Performance P870和 SiFive Intelligence X390,带来了更高的计算性能、能效水平和矢量计算能力,为生成式人工智能和机器学习领域带来差异化解决方案。

SiFive的两款新品

根据SiFive的介绍,Performance P870为该系列的最新且目前性能最高的产品。Performance系列的主要目标是面向主流的消费电子等市场,提供具有高计算能力和高数据吞吐能力的RISC-V内核,基本代表着目前商用RISC-V内核的最高性能水平。

Performance P870将RISC-V内核性能带到了一个更高的水平,成为消费类应用的理想选择。P870是6-wide乱序核心,与上一代SiFive Performance系列处理器相比,P870带来了50%的峰值单线程性能提升(specINT2k6),完全支持RVA22 RISC-V配置文件规范以及Vector 1.0和Vector Crypto,并提供共享集群缓存,支持最高 32 核集群。

Performance P870不仅对Linux操作系统有非常棒的支持,同时也支持安卓等其他丰富的操作系统。P870 完全兼容于谷歌对 RISC-V上安卓平台的要求。

P870还提供其他已经过验证的 SiFive 功能:

·128b VLEN 长度的 RISC-V 矢量(RVV)

·矢量加密和 Hypervisor 扩展

·IOMMU 和先进中断架构(AIA)

·非包含性(non-inclusive)三级缓存

·经过验证的 RISC-V WorldGuard 安全设计

另外,Performance P870A专为汽车应用而设计。

SiFive Intelligence X390基于Intelligence X280在移动、基础设施和汽车应用等领域的人工智能和机器学习应用的成功经验,带来了更加强大的智能化性能。Intelligence X390 采用单核配置、双倍矢量长度和双矢量 ALU,相比 X280 的矢量运算性能提高了4倍,持续数据带宽增加了4倍。

使用SiFive VCIX,用户可以轻松在Intelligence X280的基础上,添加自己的矢量指令和/或加速硬件,带来前所未有的灵活性,并允许他们通过自定义指令大幅提高性能。解决人工智能工作负载、数据流管理、对象检测、语音和智能推荐等方面的需求。

另外,Intelligence X280内核的特点还包括:

·1024位VLEN(单/双矢量ALU和VCIX)

·512位DLEN

·1024位矢量寄存器长度处理器

·高性能矢量存储器子系统

SiFive Performance P870和 SiFive Intelligence X390可以看作是一个人工智能解决方案的组合,通过将P870高性能通用计算SoC与由X390和客户AI硬件引擎组成的高性能NPU结合在一起,能够为产品设计师提供了一个高度灵活、低功耗和可编程的解决方案,为复杂的工作负载提供了卓越的计算密度。

SiFive董事长、总裁兼首席执行官Patrick Little表示:“SiFive正在引领行业进入高性能RISC-V创新的新时代,并以我们无与伦比的产品组合缩小与其他指令集架构的差距,而最近的流片正在展示SiFive RISC-V解决方案的巨大优势。”

商用RISC-V内核进入高性能爆发期

确实如Patrick Little所言,RISC-V架构正在缩小和其他架构之间的性能差距,高性能RISC-V内核接下来将会呈现出一种井喷状态,预计所有商业RISC-V内核公司在未来的一年左右时间内都将在这个领域大展拳脚。

在国内的RISC-V商业内核公司方面,2022年赛昉科技已经正式交付其高性能RISC-V内核系列产品——昉·天枢。其中,昉·天枢-90 是可交付性能最高的商业级国产RISC-V CPU Core IP,频率为2GHz@TSMC 12nm,采用 11+ 级流水线、五发射、超标量、深度乱序执行等设计,支持标准 RISC-V RV64GCBH 扩展,同时还针对性能和频率做了深度的优化,SPECint2006 可达 9.4/GHz。赛昉科技董事长兼CEO徐滔表示,“昉·天枢-90与昉·天枢-80的推出将进一步扩展RISC-V处理器的应用边界,协同促进RISC-V在端、边、云场景的应用落地。”

阿里平头哥也在布局高性能RISC-V。8月23日,平头哥在2023 RISC-V中国峰会上发布首个自研RISC-V AI平台,通过软硬件深度协同,较经典方案提升超八成性能,支持运行170余个主流AI模型,推动RISC-V进入高性能AI应用时代。另外玄铁C920也公布了性能信息,玄铁C920采用12级多发乱序流水线,典型工作频率>2.5GHz,标配单精度浮点单元,并可进一步选配高性能乱序矢量运算单元。同时具备出色的访存能力,支持高性能数据预取技术。资料显示,C920执行GEMM(矩阵的矩阵乘法)计算较Vector方案可提速15倍。

除了高性能RISC-V内核和芯片平台之外,高性能RISC-V芯片也已经陆续面世,将RISC-V内核带到更广阔的应用场景中,当然其中支持人工智能和机器学习应用是最主要的方向。

小结

随着SiFive Performance P870和 SiFive Intelligence X390的发布,RISC-V架构给ARM架构带来了更大的压力,P870预计将直接对标ARM的Cortex-X系列。同时,随着应用范围逐渐拓展,x86架构也并不能一直高枕无忧。

-

RISC-V

+关注

关注

45文章

2271浏览量

46134

发布评论请先 登录

相关推荐

RISC-V架构及MRS开发环境回顾

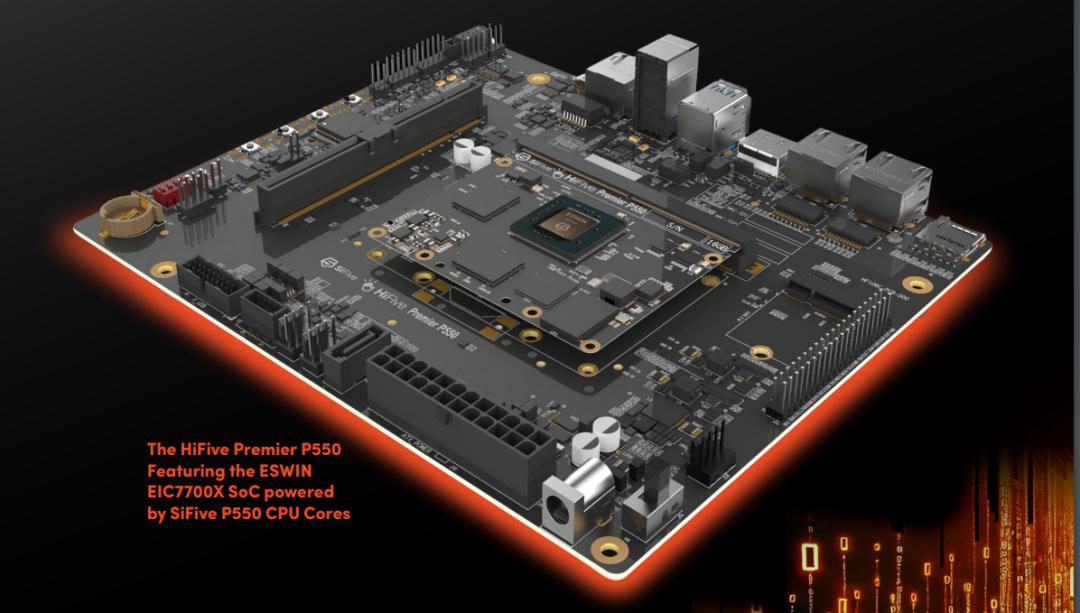

SiFive 推出高性能 Risc-V CPU 开发板 HiFive Premier P550

基于risc-v架构的芯片与linux系统兼容性讨论

《RISC-V能否复制Linux 的成功?》

什么是RISC-V?以及RISC-V和ARM、X86的区别

名单公布!【书籍评测活动NO.45】RISC-V体系结构编程与实践(第二版)

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

risc-v的发展历史

为什么要有RISC-V

SiFive 加入甲辰计划,共创 RISC-V 生态繁荣

SiFive发布P870和X390,RISC-V架构内核性能暴涨

SiFive发布P870和X390,RISC-V架构内核性能暴涨

评论