低功耗FSMs

低功耗设计是当下的需要!这篇文章:低功耗设计方法论的必要性让我们深入了解了现代设计的意图和对功耗感知的需求。在低功耗方法标签下的时钟门控和电源门控的后续文章中,讨论了一些SoC低功耗设计的方法。在这篇文章中,我们将考虑一个这样的低功耗设计的FSM,可以推广到任何低功耗时序电路的设计。

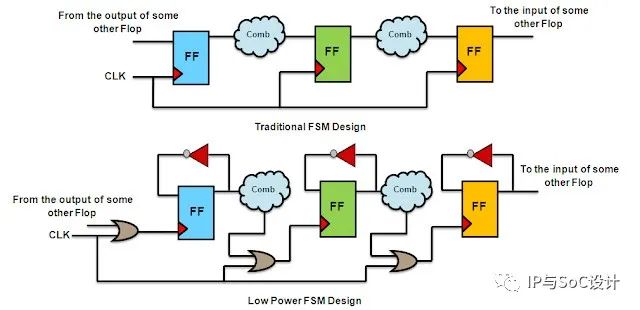

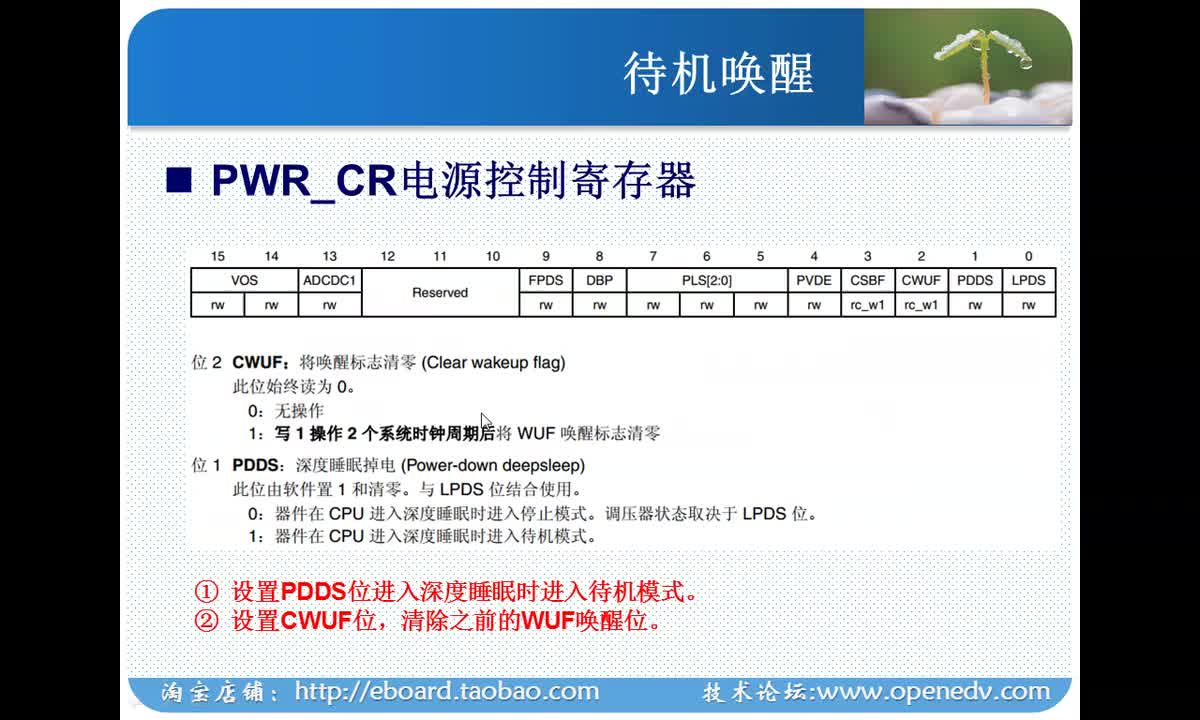

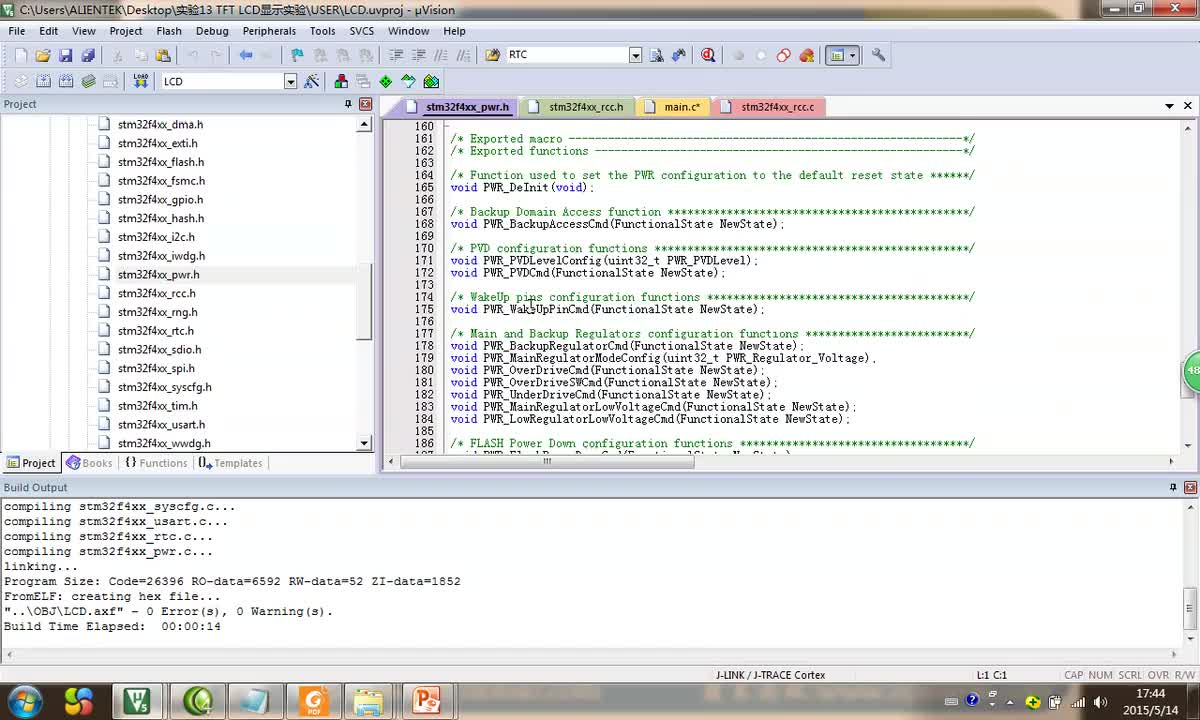

考虑以下传统和低功耗FSM的通用设计:

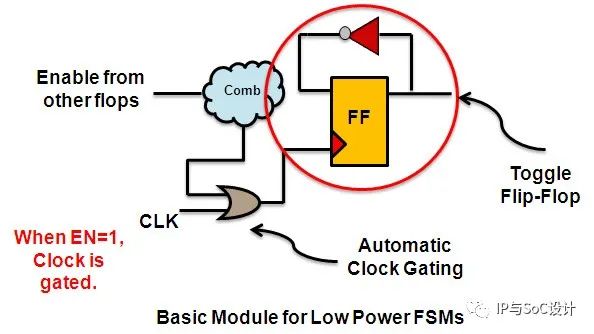

让我们来讨论一下我们在这里使用过的基本构建块。"或"门作为触发器的时钟门。我们使用的触发器是一个触发器。当 enable = 0 时,触发器接收时钟,并切换其状态。所以,每当我们需要改变翻牌的状态时,我们可以给出一个时钟脉冲。

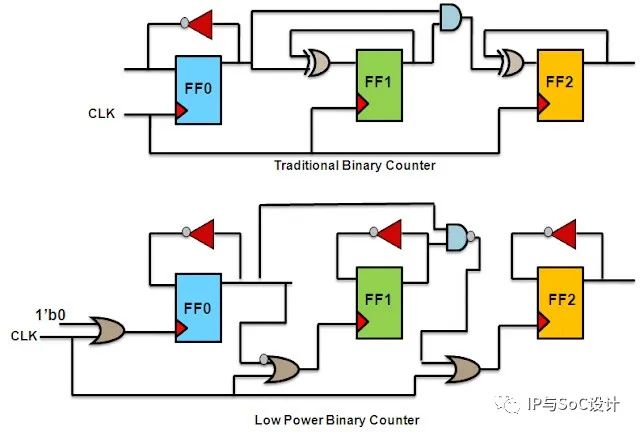

说得够多了!现在我们来讨论一个基本同步计数器的真实例子。以及如何利用上述方法设计一个低功耗同步计数器。

在任何二进制计数器中:

·最低阶位在每个时钟周期后切换。

·只有当所有低阶位都在逻辑1时,任何高阶位才进行切换。

记住这一点,我们现在可以建立低功耗计数器!!

审核编辑:汤梓红

-

soc

+关注

关注

38文章

4115浏览量

217896 -

时序电路

+关注

关注

1文章

114浏览量

21679 -

触发器

+关注

关注

14文章

1995浏览量

61043 -

低功耗设计

+关注

关注

0文章

80浏览量

16143

原文标题:博文速递:Low Power FSMs

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【专题】低功耗电路设计__低功耗设计技巧

低功耗蓝牙怎么低功耗?如何界定

AD,低功耗

低功耗电路设计_低功耗设计方法

什么是低功耗,对FPGA低功耗设计的介绍

还在了解什么是低功耗?FPGA低功耗设计详解

如何使用Freeze技术实现低功耗设计

低功耗设计

FSMs低功耗设计

FSMs低功耗设计

评论