时序逻辑电路与组合逻辑电路的区别在于,时序逻辑电路的输出并不仅仅由输入条件决定,还由输出的前一个状态有关。也就是说,当输入改变时,不能唯一确定输出是什么,还要看输入改变前输出是什么状态,一起决定后面的输出状态。简而言之,这是一个有反馈的电路。

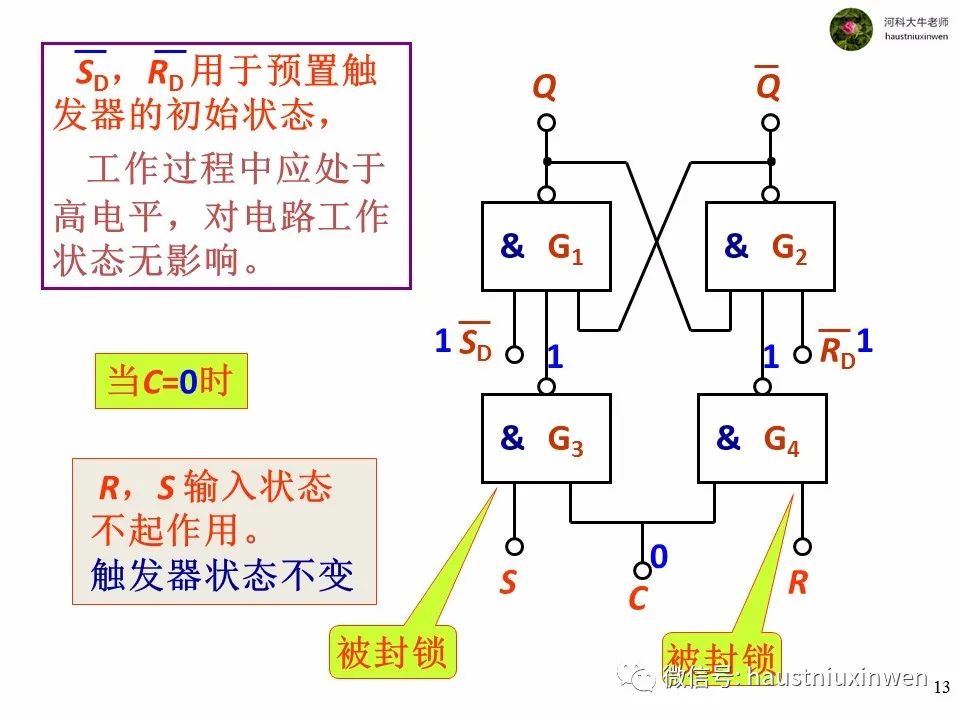

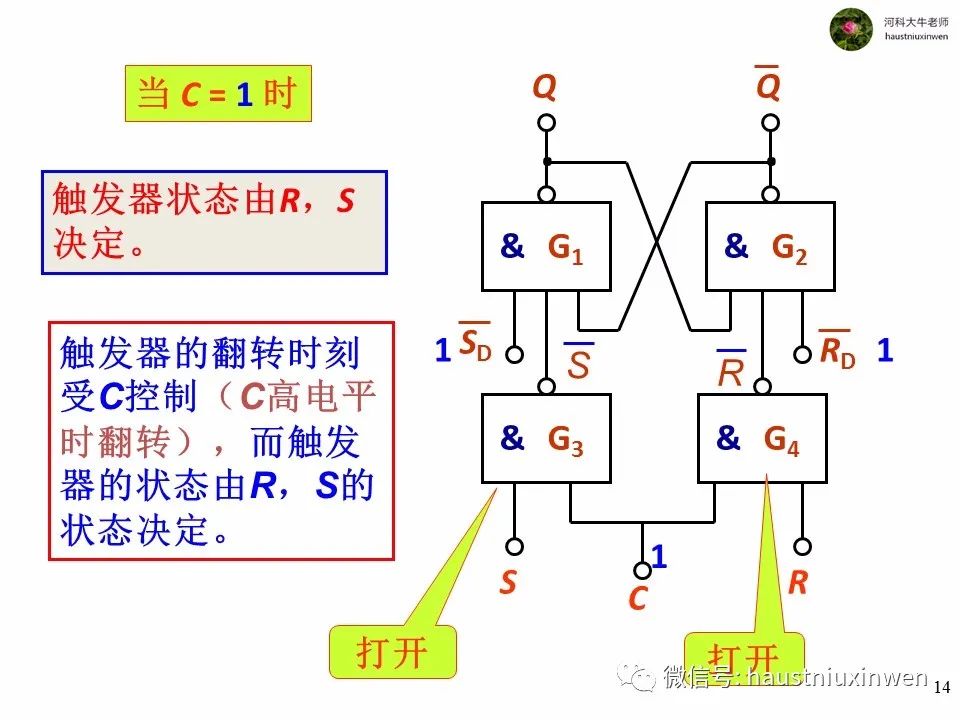

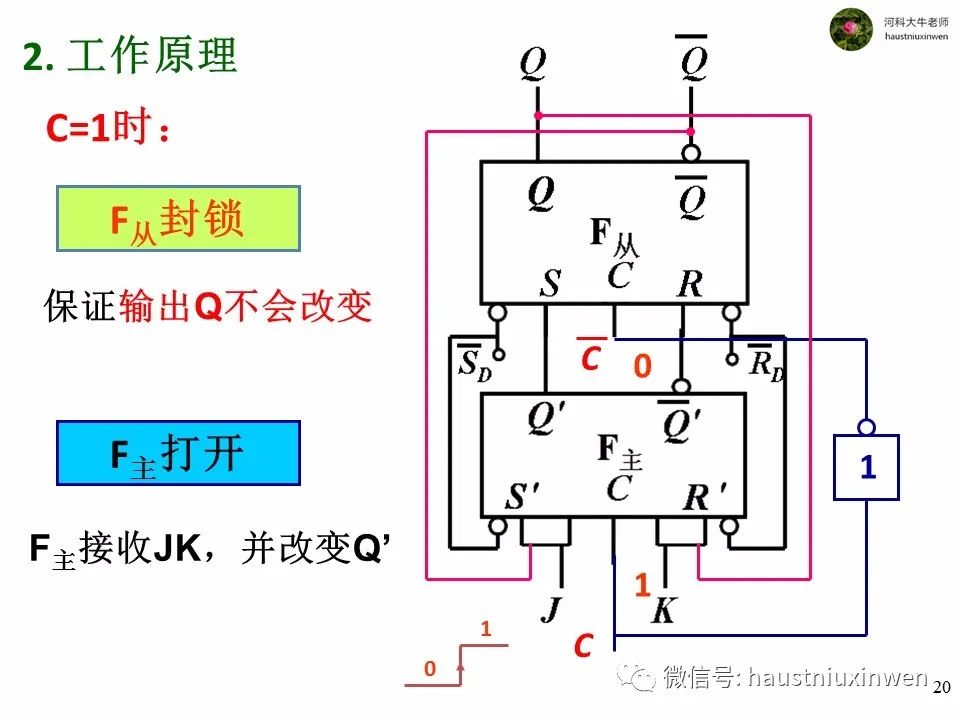

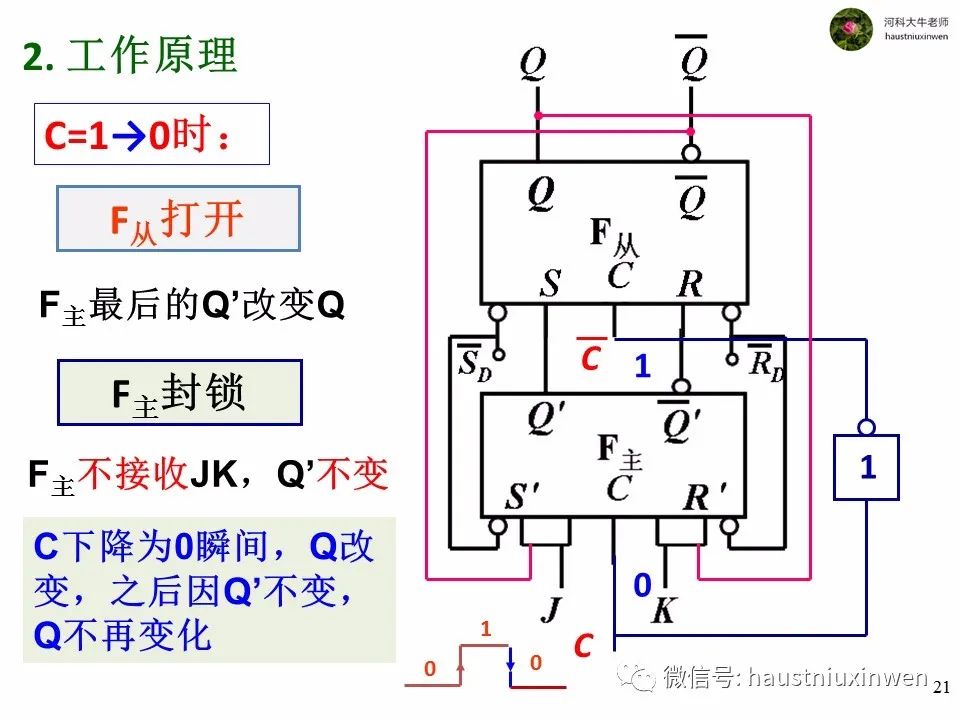

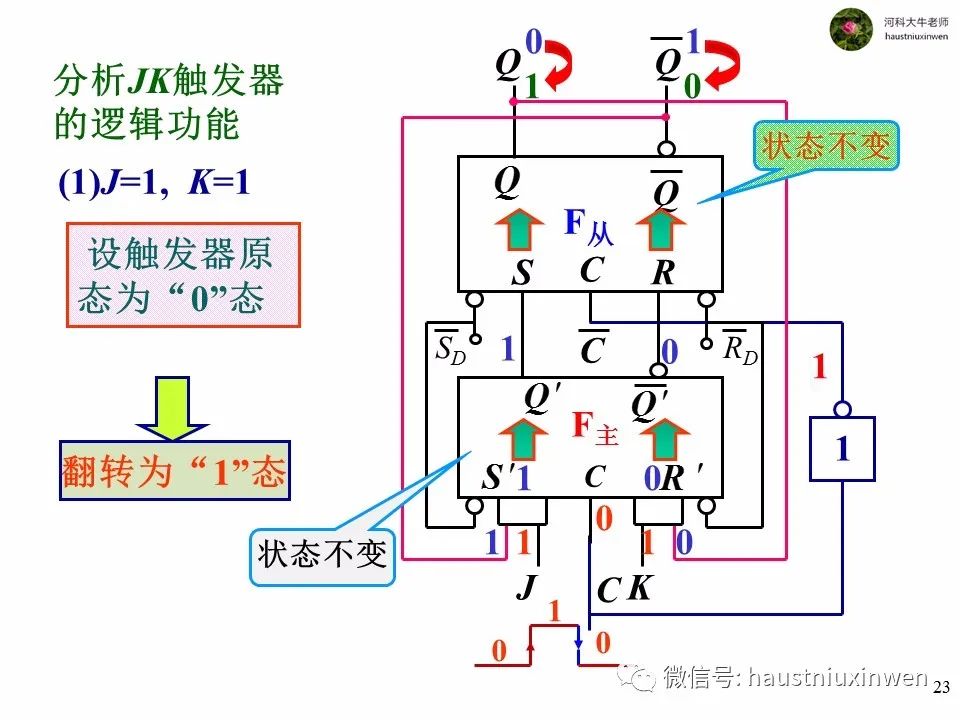

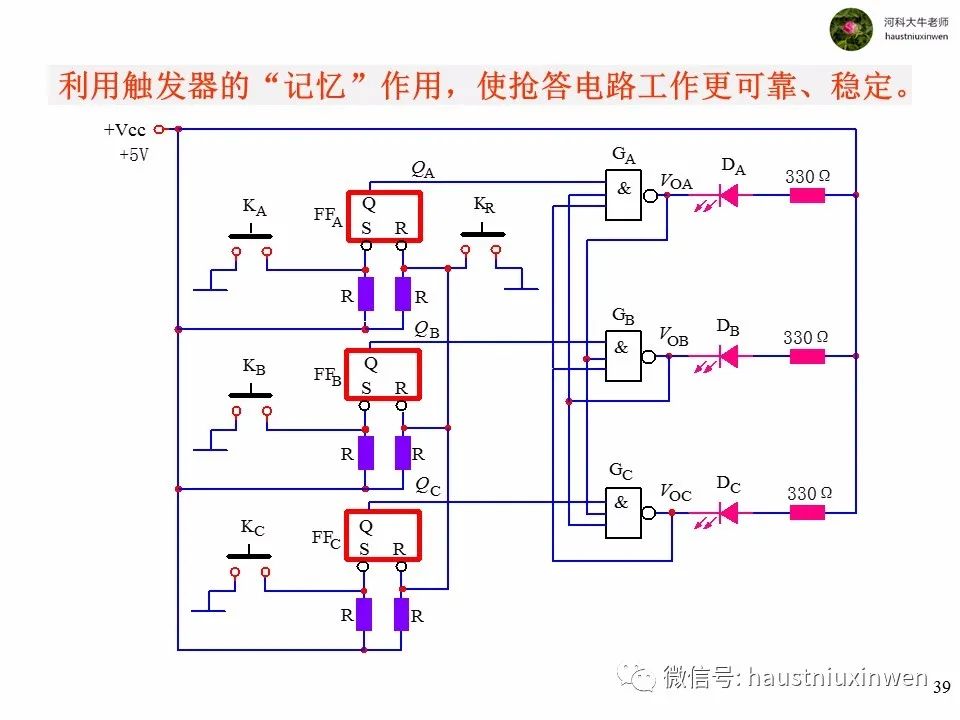

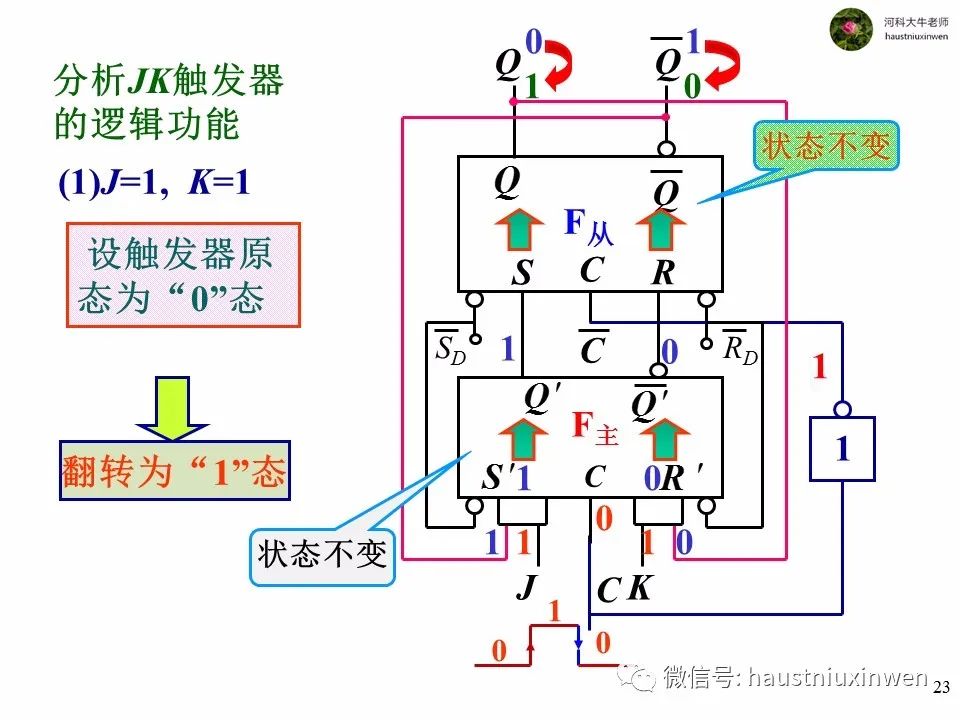

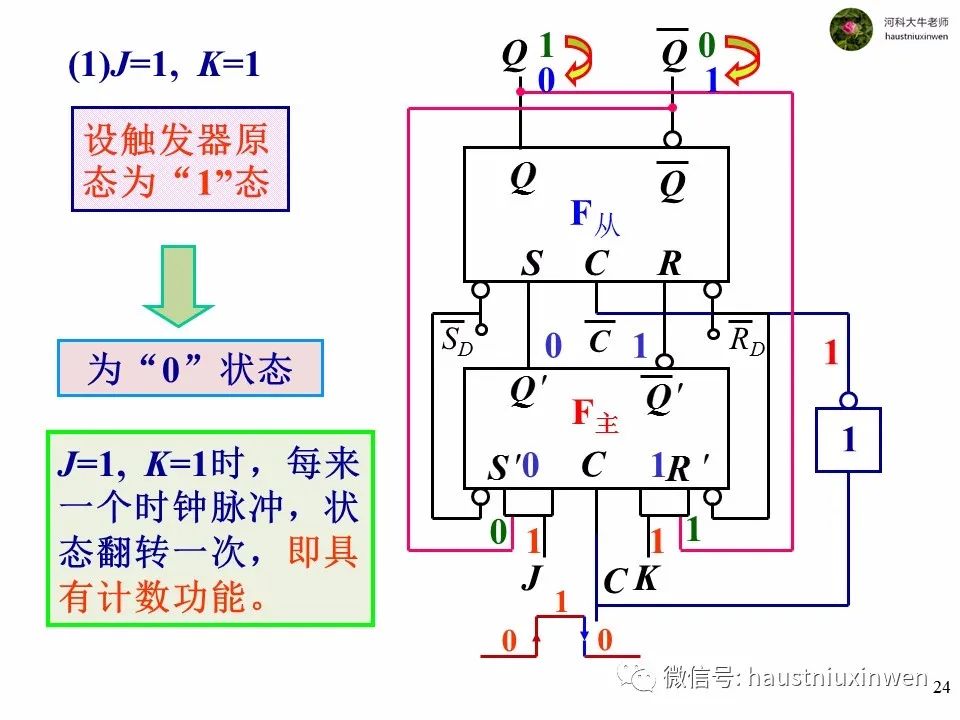

与模拟电路中的反馈不同的是,反馈不是随时随地进行的,而是有节奏的,当有效触发信号来临,才能进行控制输出的作用。触发信号不来,输入信号即便有变化,也不能改变输出。这种动作机制可以保证逻辑电路的多个输入信号动作完成后才去实现逻辑功能,即减少误动作,增加可靠性。

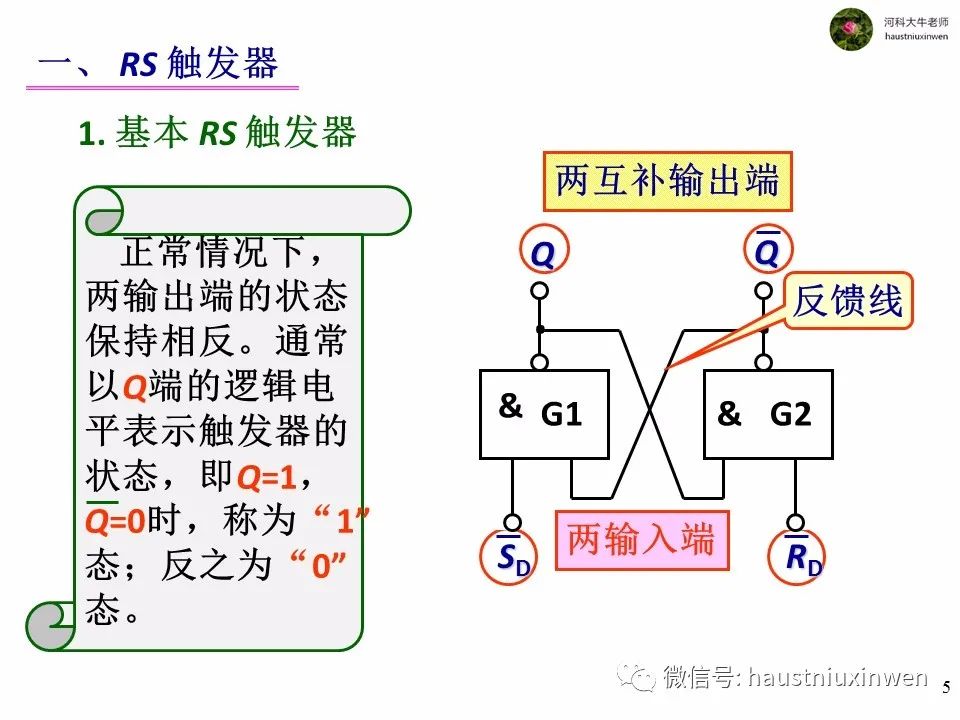

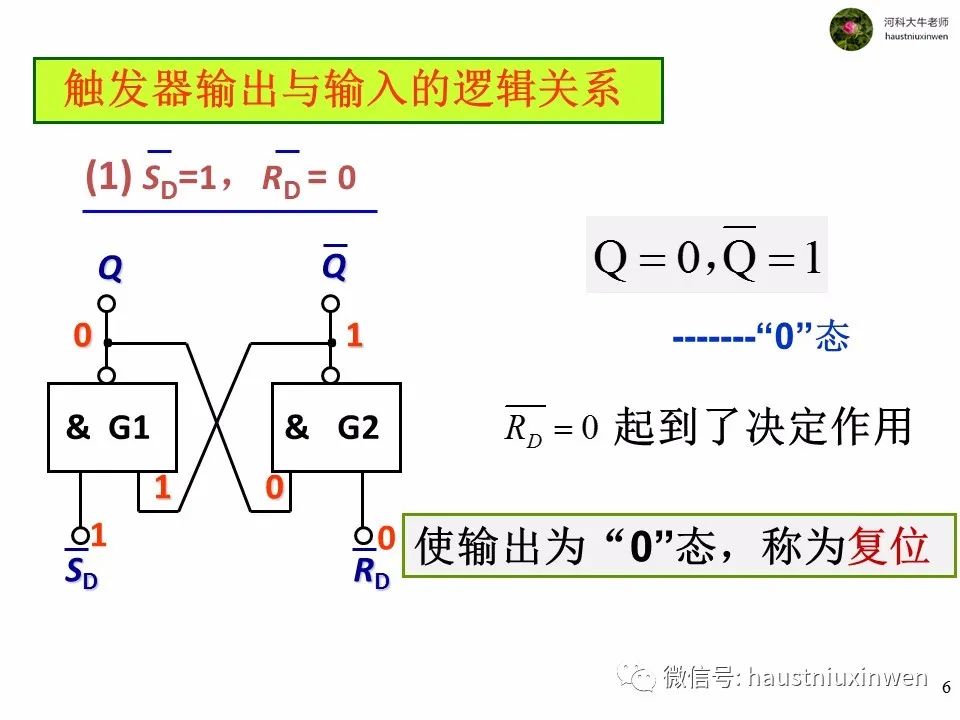

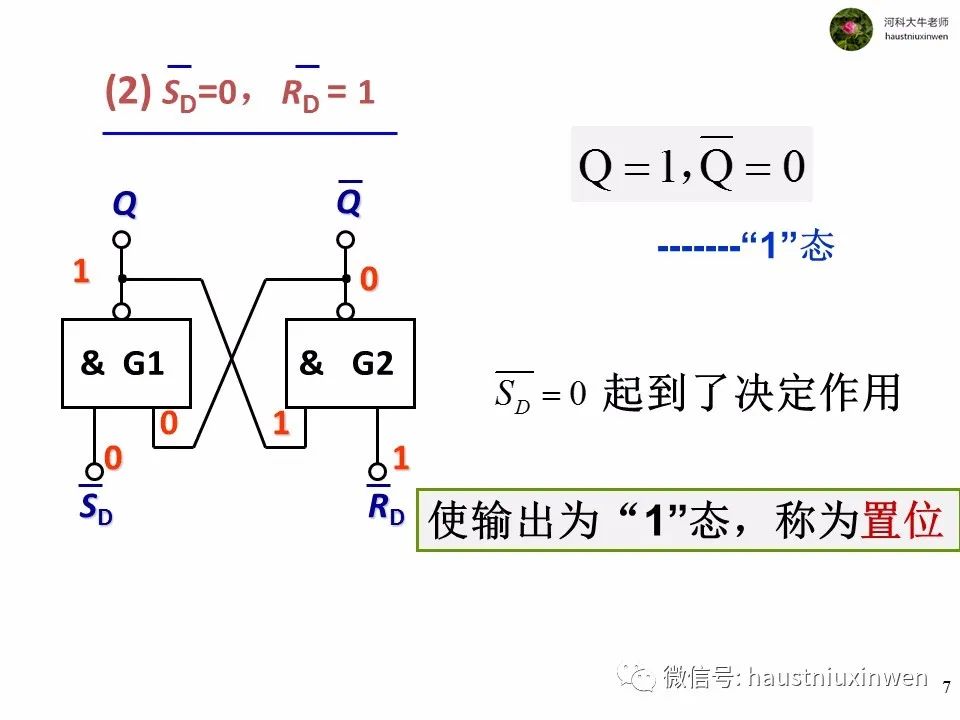

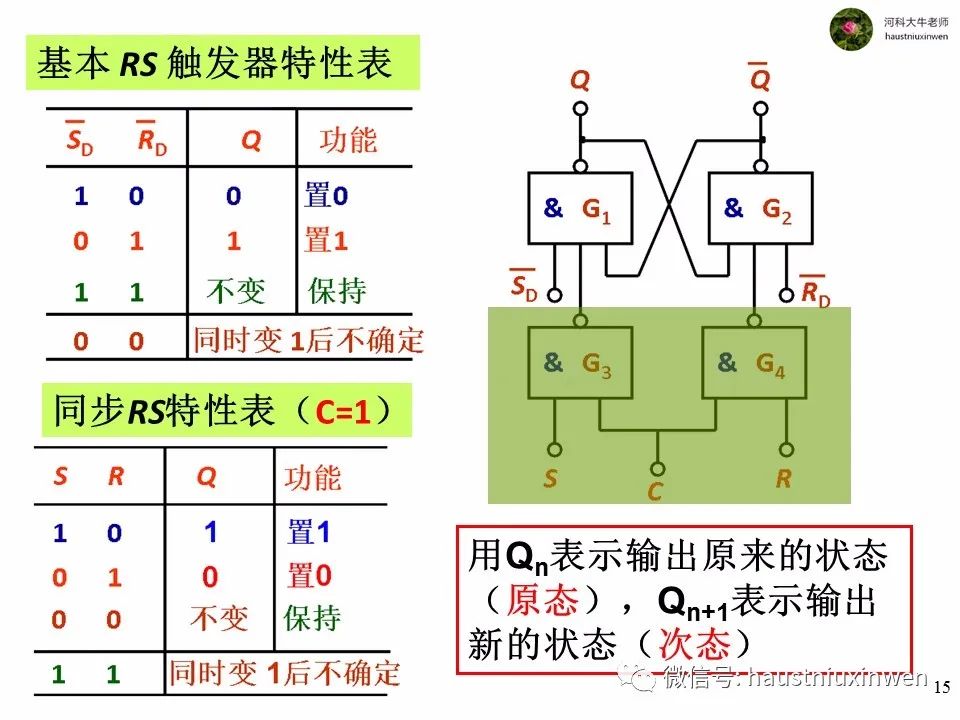

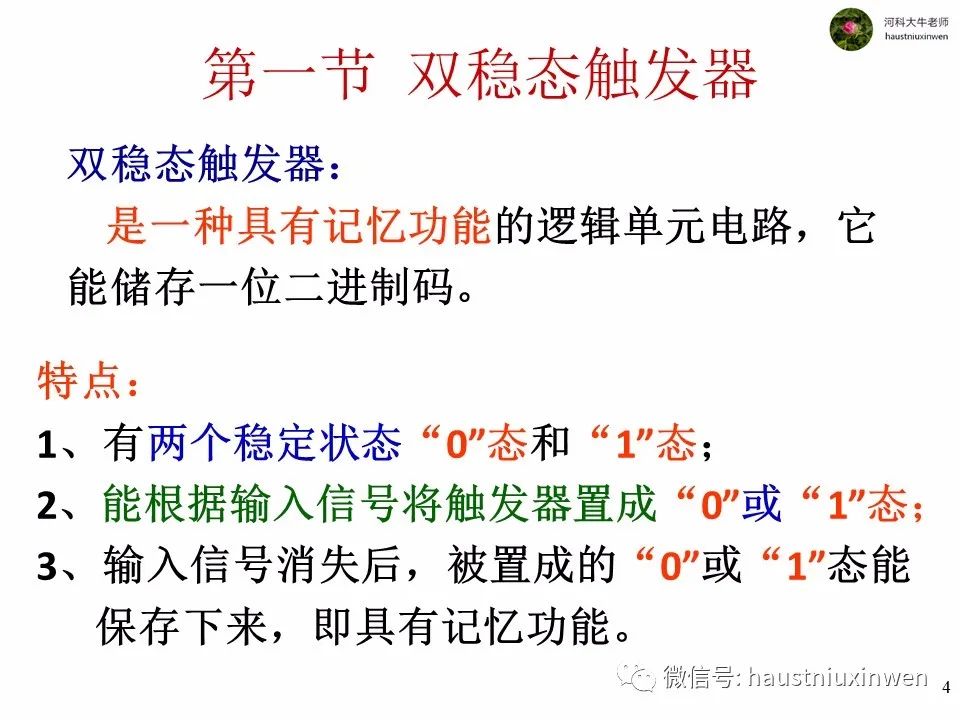

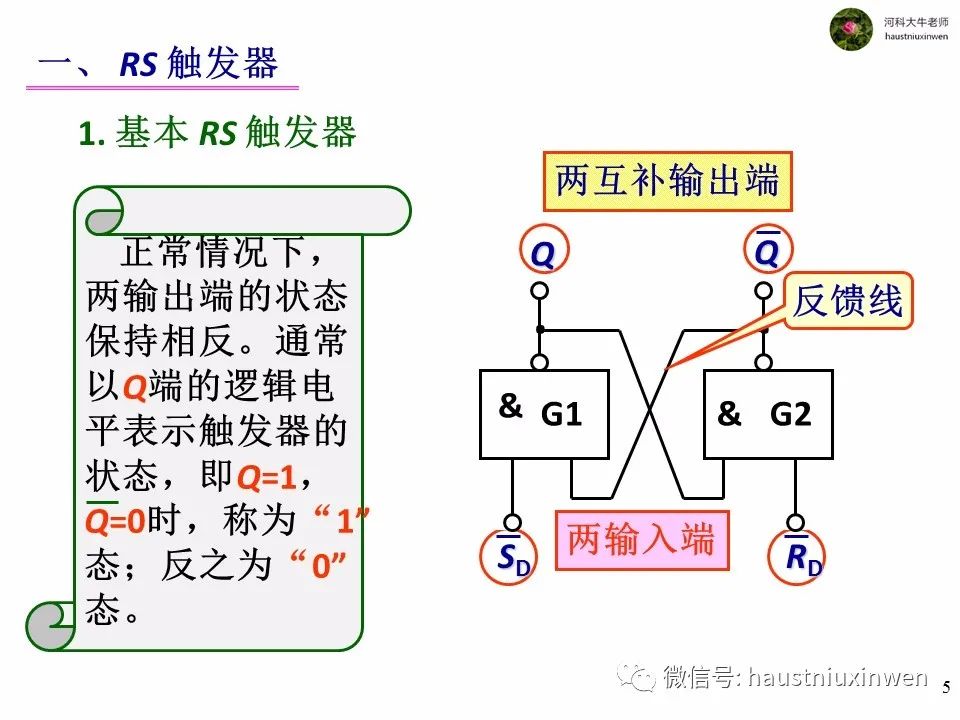

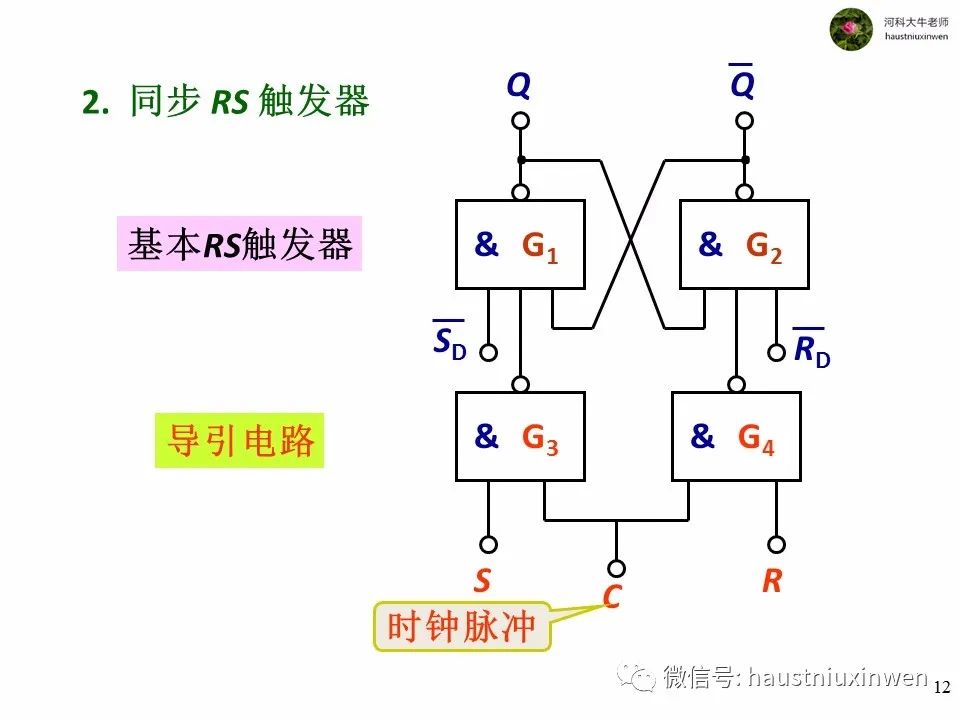

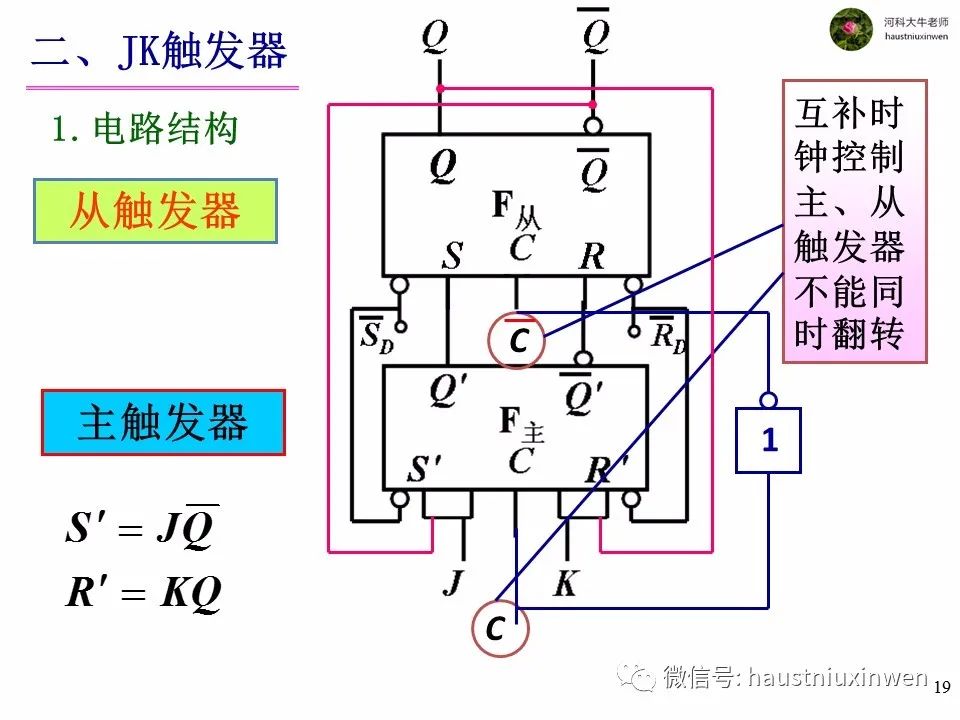

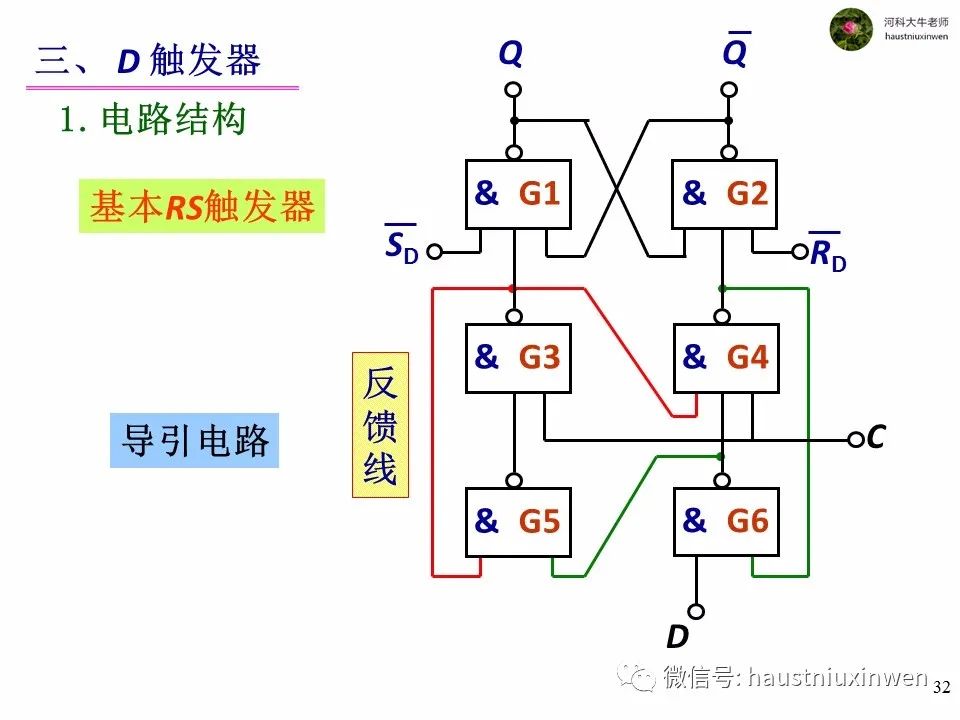

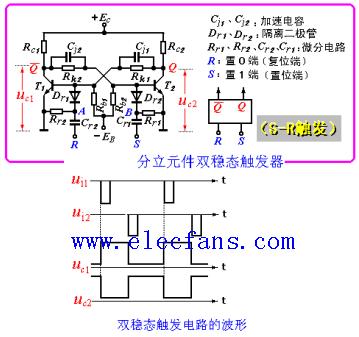

组合逻辑电路的基本单元是门电路,而时序逻辑电路的基础单元是双稳态触发器。

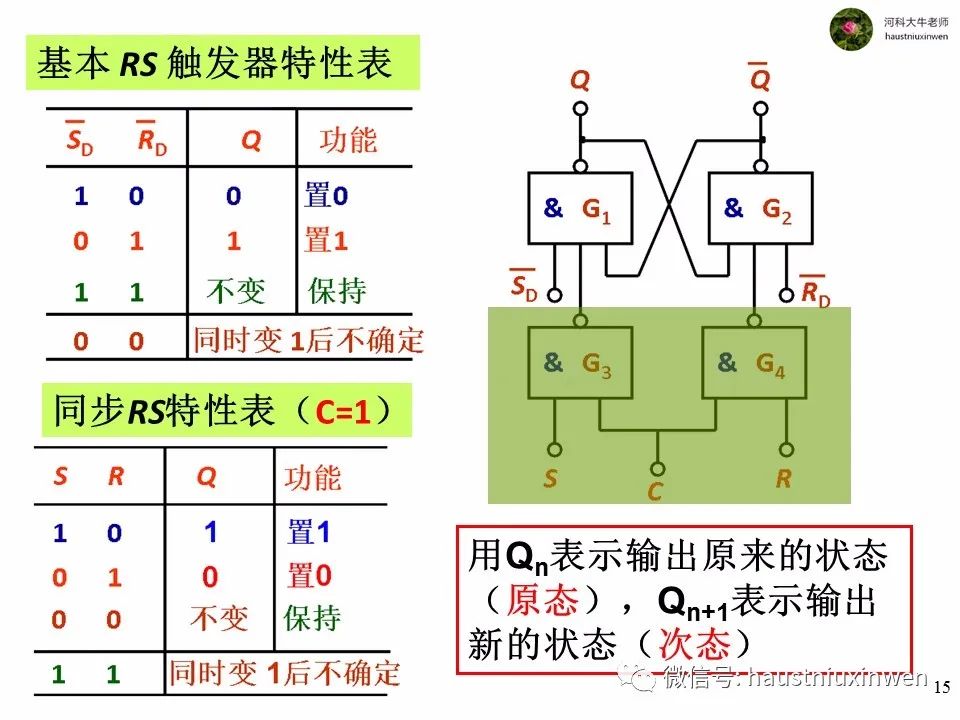

稳态是指在没有有效触发信号时,输出端的状态始终保持不变。

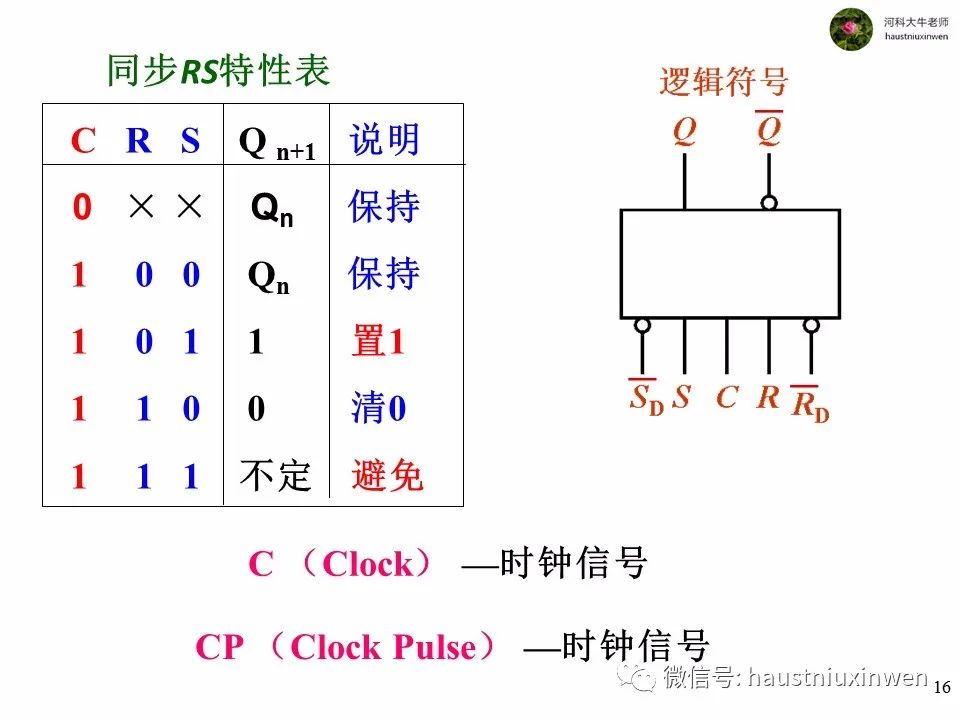

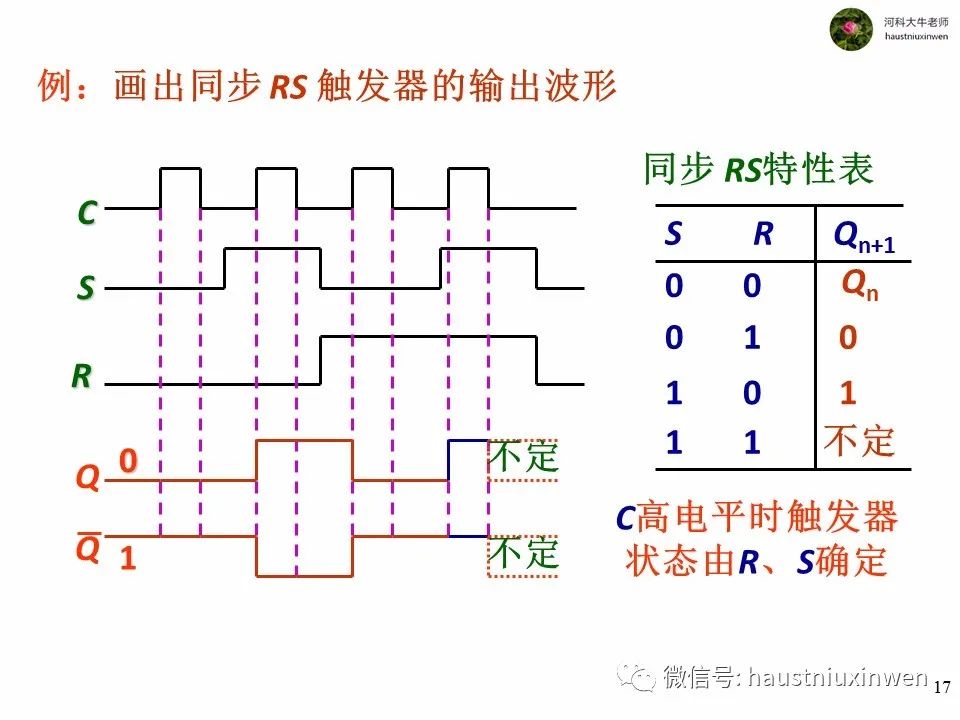

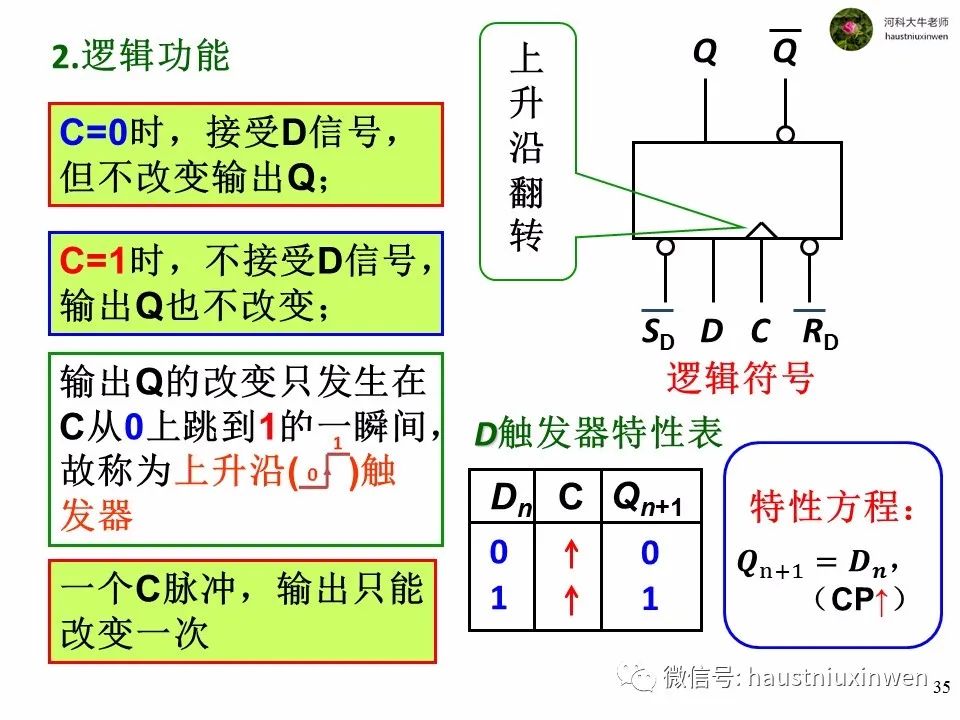

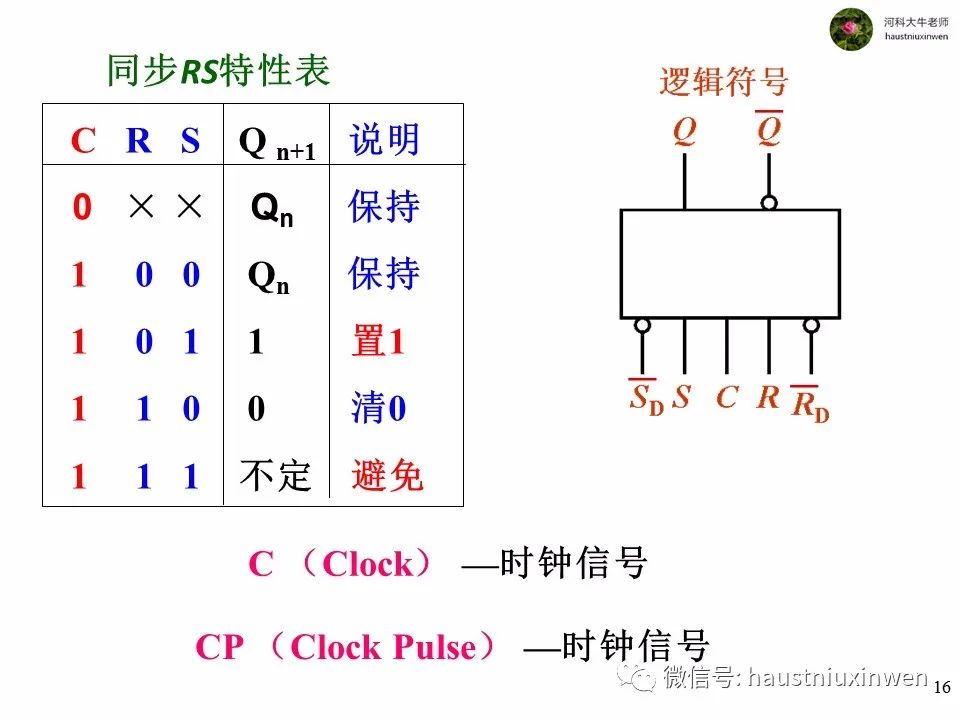

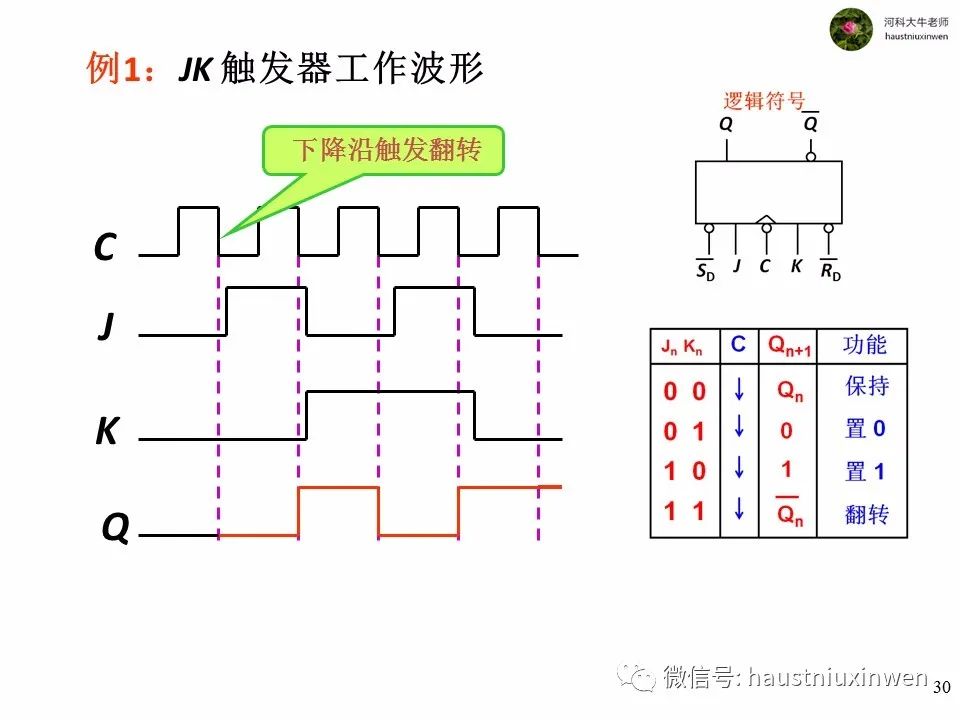

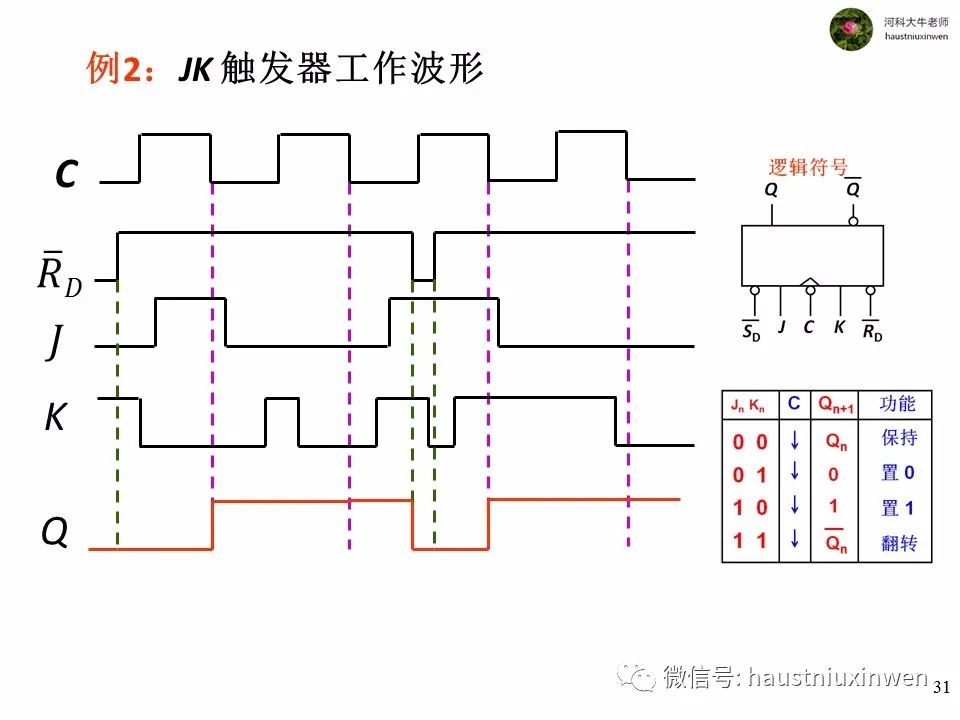

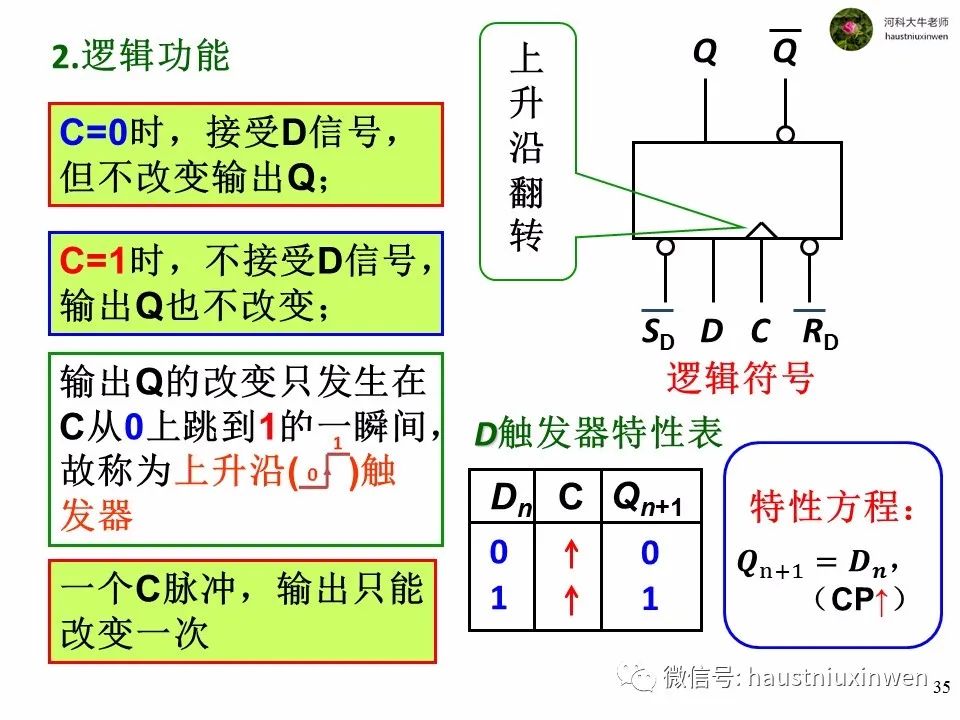

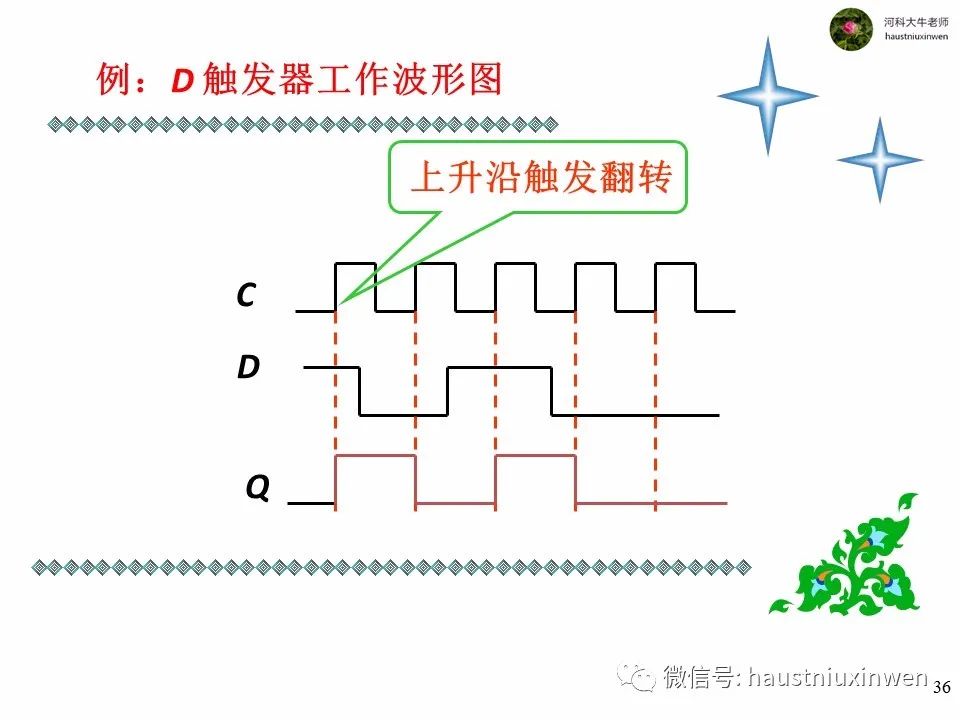

而触发信号有电平触发和边沿触发两种。

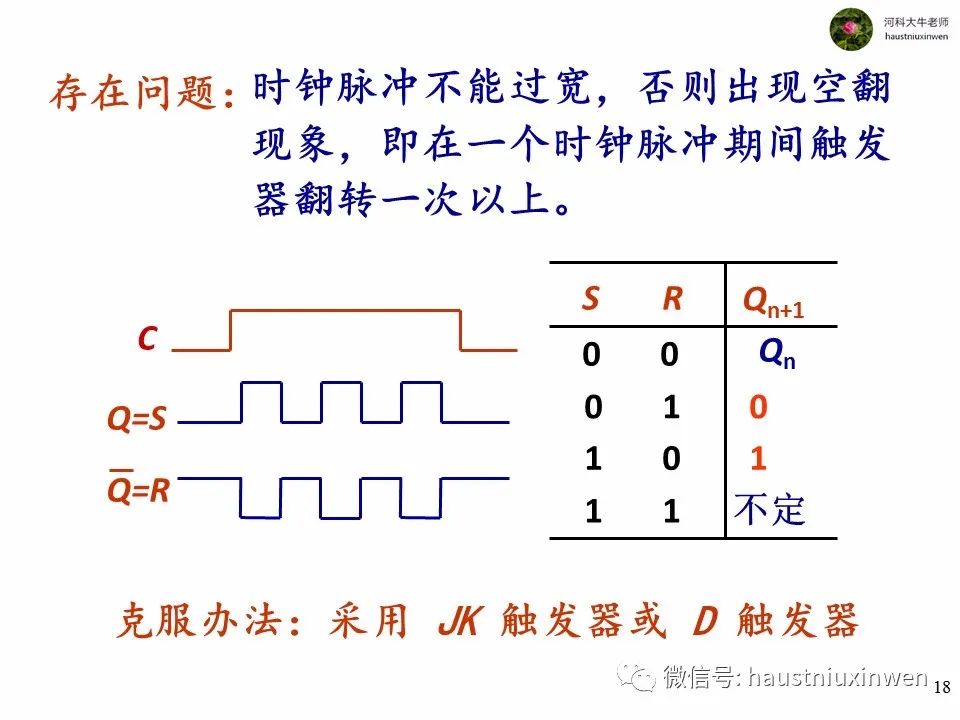

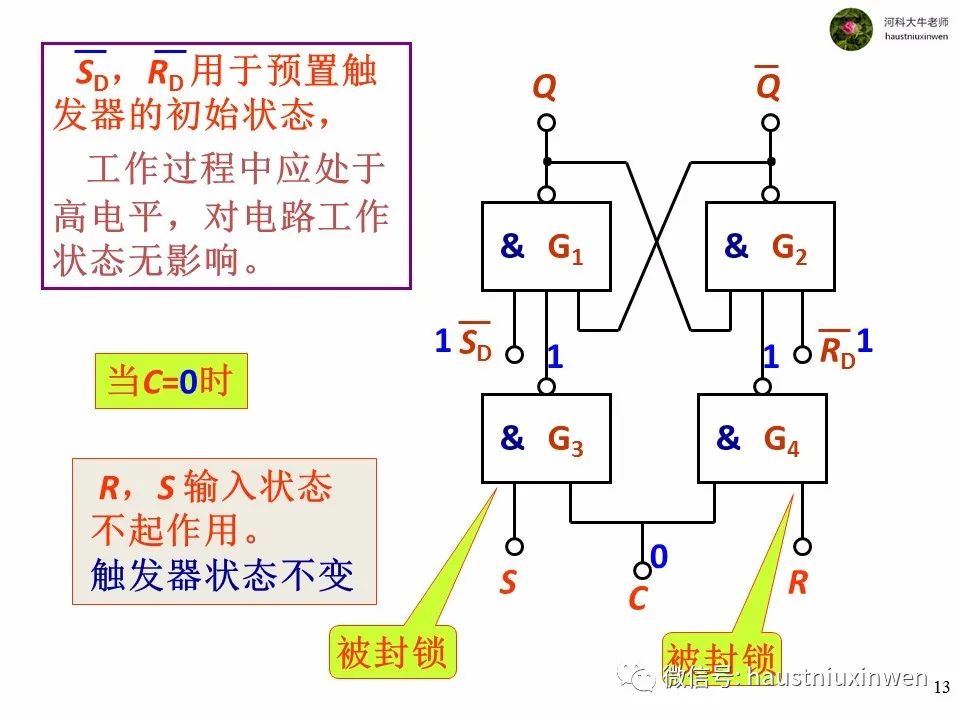

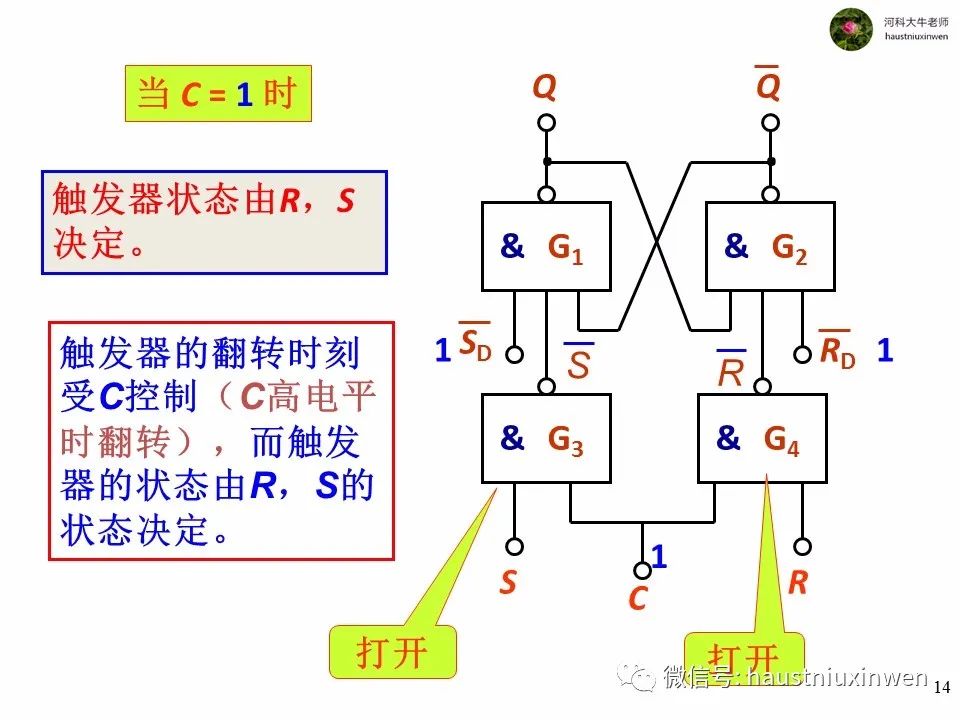

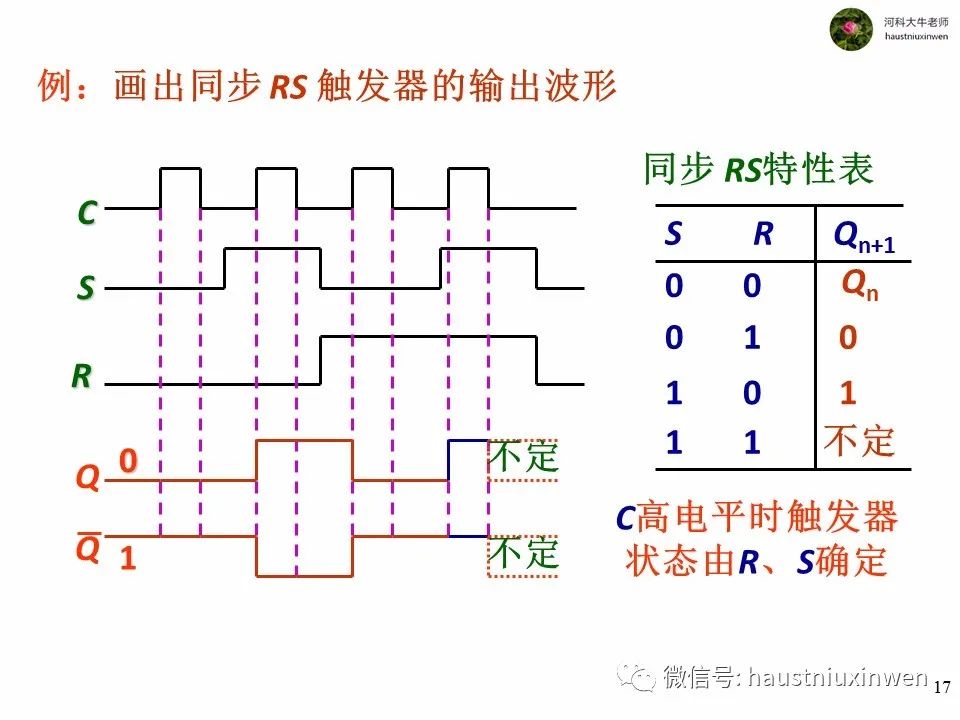

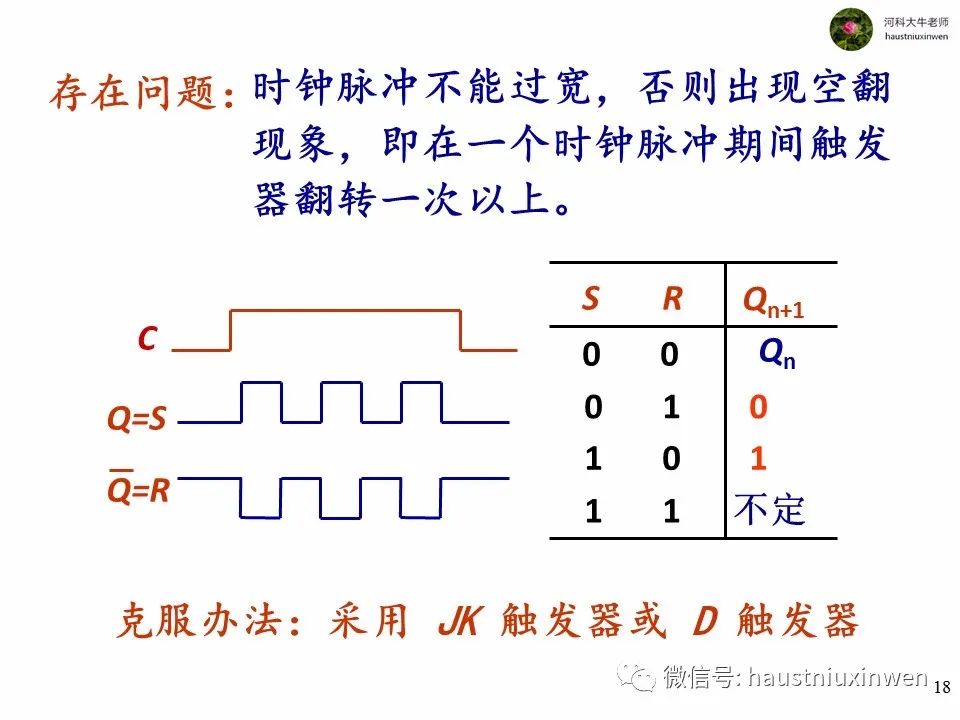

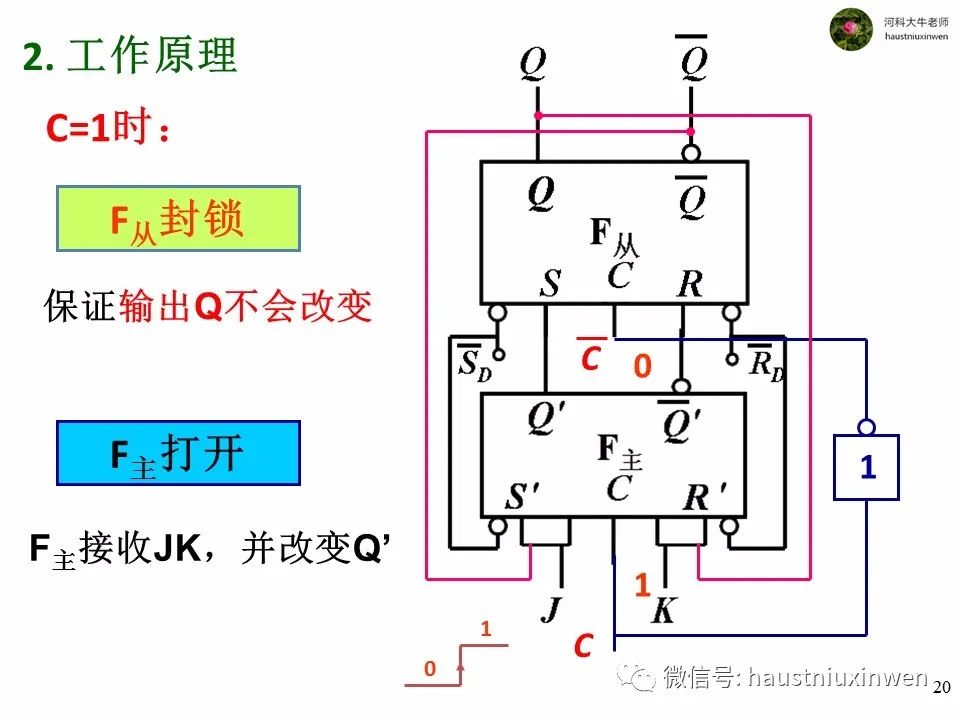

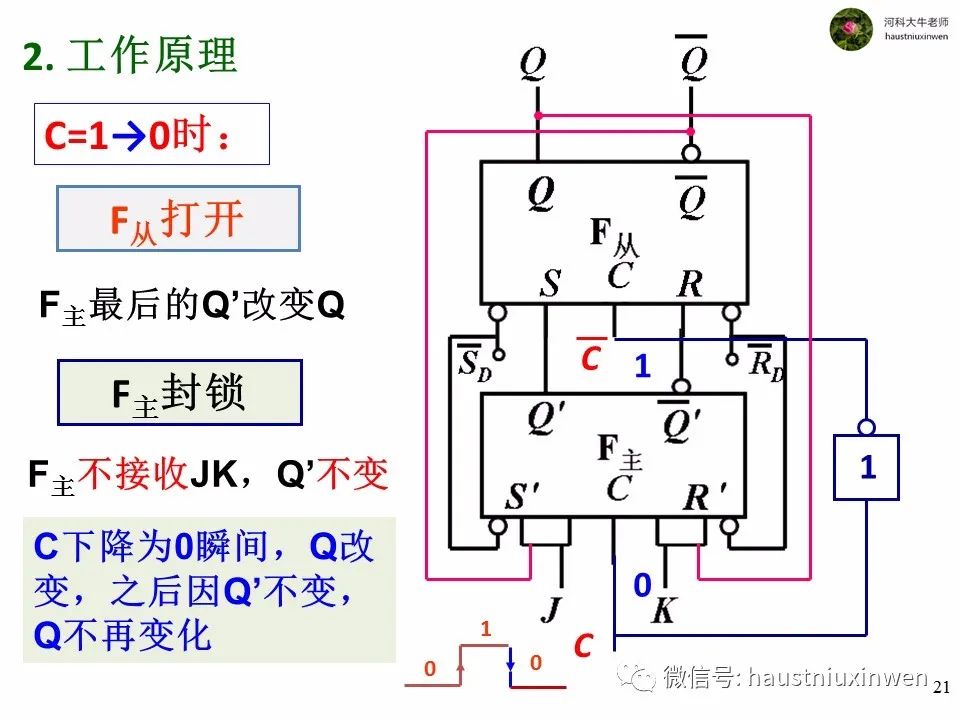

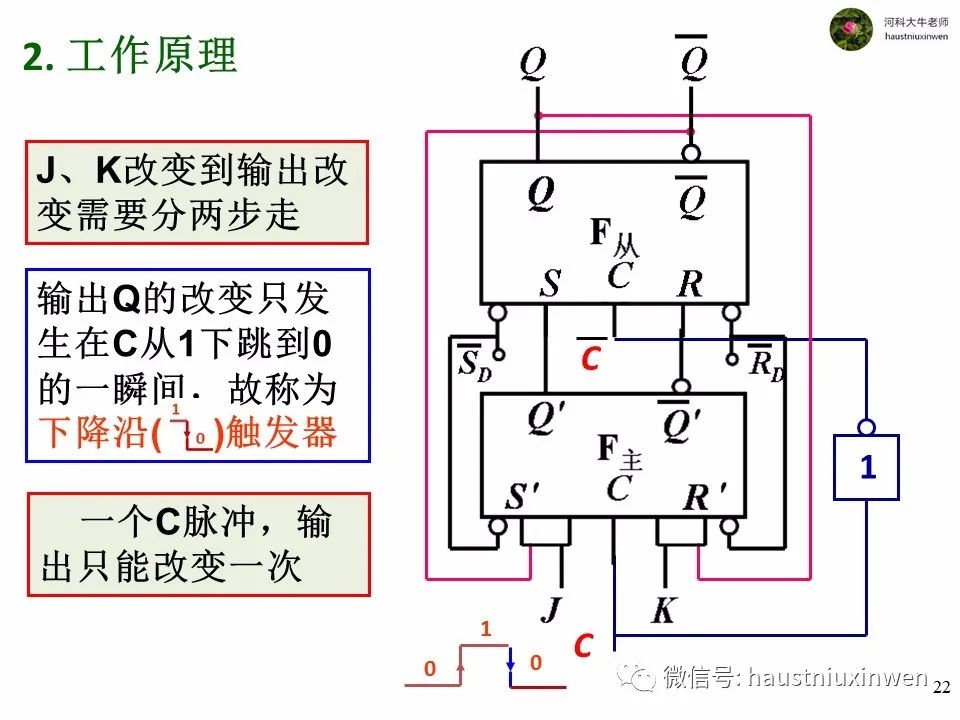

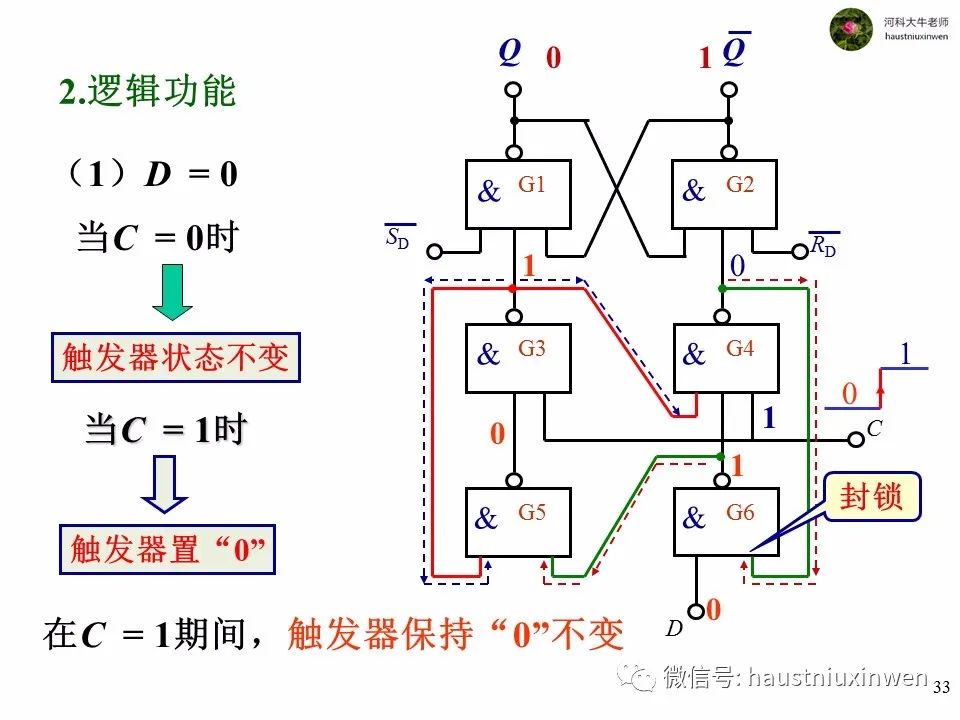

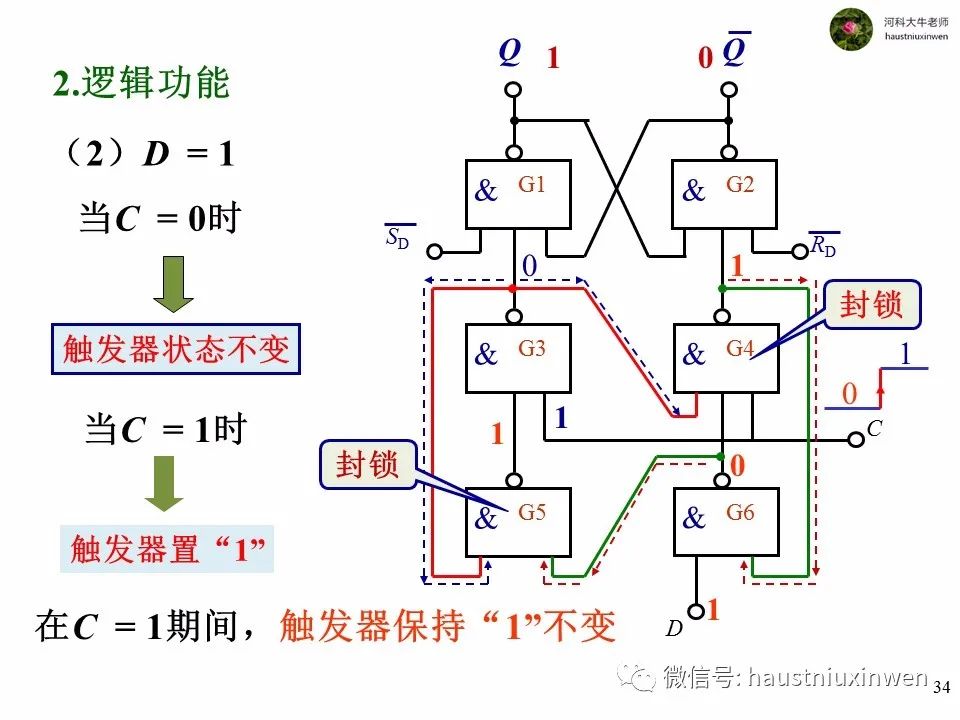

电平触发是指当时钟信号为高电平时,允许输出根据输入和原状态改变。边沿触发是指当时钟信号由0变1或者由1变0时,输出才能根据输入和原状态改变。

电平触发在需要多个信号都满足时才执行功能的情况下经常使用,以避免因多路信号反应时间不一致造成的误操作。

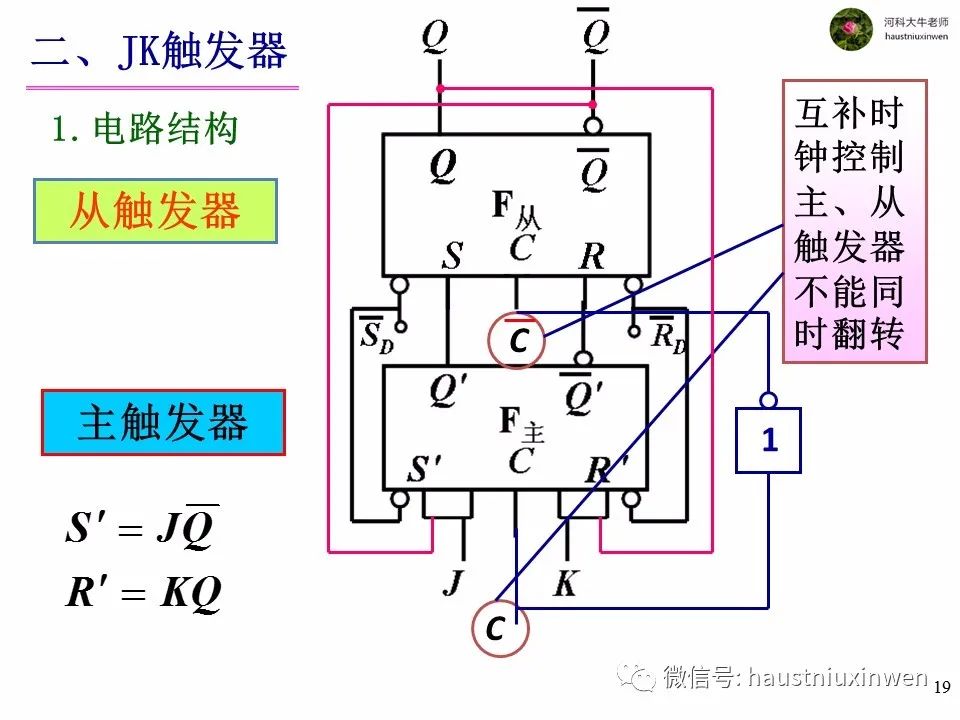

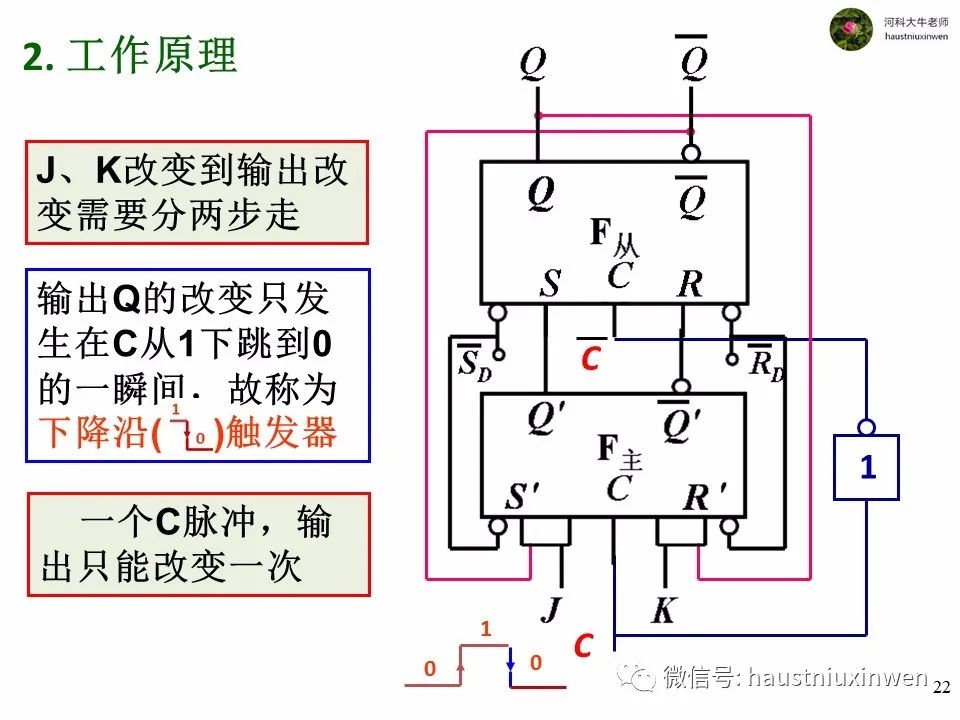

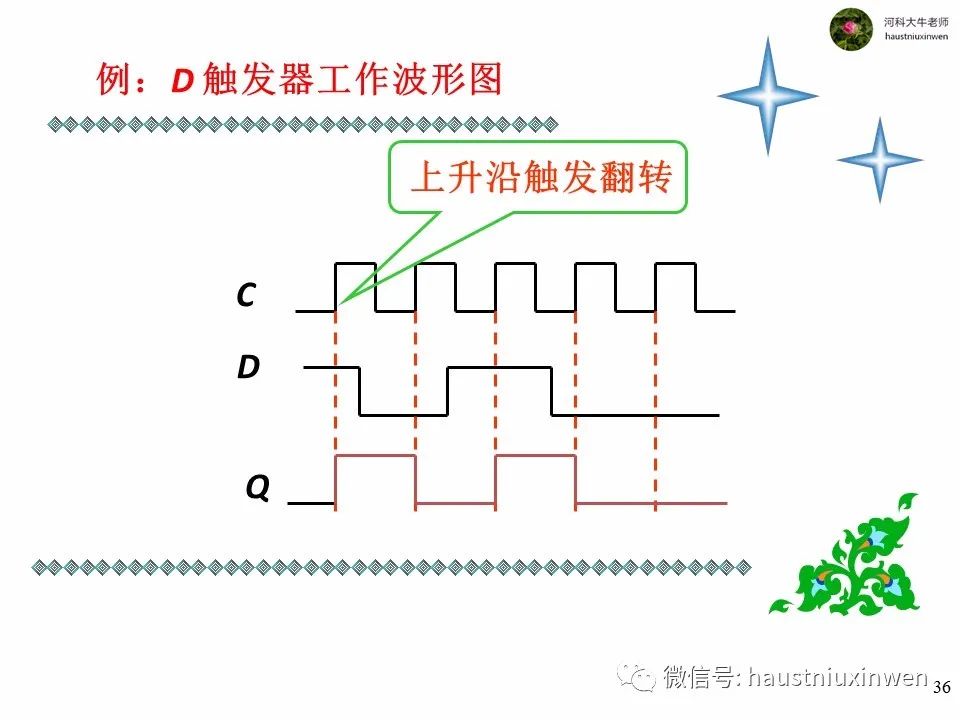

边沿触发可以实现一个触发脉冲信号触发器只动作一次的功能,避免空翻失控。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

数字电路--触发器双稳态触发器

发表于 02-05 14:16

什么是双稳态触发器?

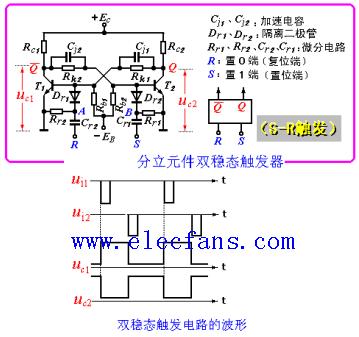

双稳态触发电路实际上也是RS触发器,其ui1端相当于R端,ui2端相当于S端。因此,用门电路组成的

发表于 05-26 13:31

•1w次阅读

数字电路--触发器双稳态触发器

发表于 12-20 17:32

•0次下载

本文主要介绍了双稳态触发器的工作原理详解。双稳态触发器是脉冲和数字电路中常用的基本触发器之一。双稳态

发表于 04-04 10:58

•10.1w次阅读

双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的数字逻辑电路,广泛应用于数字系统中的存储、计数、时序控制等领域。 一、双稳态触发器的基本特征

![的头像]() 发表于

发表于 08-11 09:56

•617次阅读

双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的逻辑电路,广泛应用于数字电路设计中。 双稳态触发器的基本概念 双稳态

![的头像]() 发表于

发表于 08-11 09:59

•906次阅读

双稳态触发器(Bistable Trigger or Flip-Flop)是一种具有两个稳定状态的数字电路元件,广泛应用于数字逻辑电路、存储器和时序电路中。 一、双稳态

![的头像]() 发表于

发表于 08-11 10:00

•2811次阅读

双稳态触发器的两个稳定状态通常被称为“0”状态和“1”状态,这两个状态可以分别用来表示二进制数码的0和1。具体来说: 0状态 :在此状态下,双稳态触发器的输出Q为0,而其非输出(通常表

![的头像]() 发表于

发表于 08-11 10:05

•1042次阅读

双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的逻辑电路,广泛应用于数字电路设计中。它具有两个基本性质:记忆性和切换性。 一、双稳态触发器的基本概念 1.1

![的头像]() 发表于

发表于 08-11 10:08

•735次阅读

双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的触发器,广泛应用于数字电路和电子系统中。 一、双稳态触发器的特点 稳

![的头像]() 发表于

发表于 08-11 10:10

•683次阅读

双稳态触发器是一种具有两个稳定状态的数字逻辑电路,它可以在两个状态之间切换,并且能够在没有外部输入信号的情况下保持当前状态。双稳态触发器广泛应用于数字电子系统中,如存储

![的头像]() 发表于

发表于 08-11 10:15

•817次阅读

双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的电路,通常用于存储一位二进制信息。在数字电路中,双稳态触发器是一种非常重要的基本组件,广泛应用于寄存

![的头像]() 发表于

发表于 08-11 10:18

•1710次阅读

双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的电子电路,广泛应用于数字电路设计中。 双稳态触发器的工作原理 双稳态

![的头像]() 发表于

发表于 08-11 10:21

•833次阅读

双稳态触发器的使用方法主要包括以下几个方面: 一、安装与连接 安装 :双稳态触发器通常是以集成电路的形式存在,可以通过焊接或插入到电路板上。在安装过程中,需要注意正确的引脚连接和电路布

![的头像]() 发表于

发表于 08-11 10:23

•590次阅读

双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的数字电路,常用于存储一位二进制信息。它在数字电路设计中具有重要应用,如存储器、计数器、寄存

![的头像]() 发表于

发表于 08-22 10:12

•668次阅读

双稳态触发器设计

双稳态触发器设计

评论