基于芯动神州ADSD1299设计的可穿戴式脑电采集前端,具有采集精度高、体积小、功耗低、抗干扰性强等特点。采用ADSD1299内部集成的可编程放大器(PGA)实现微弱信号的放大。为了消除干扰,使用限幅滤波预处理电路和ADSD1299内部集成的偏置驱动放大器。实验测试表明,该脑电采集前端设计能较好地把微弱的脑电信号提取出来,并且具有较好的抗干扰能力和实用价值。

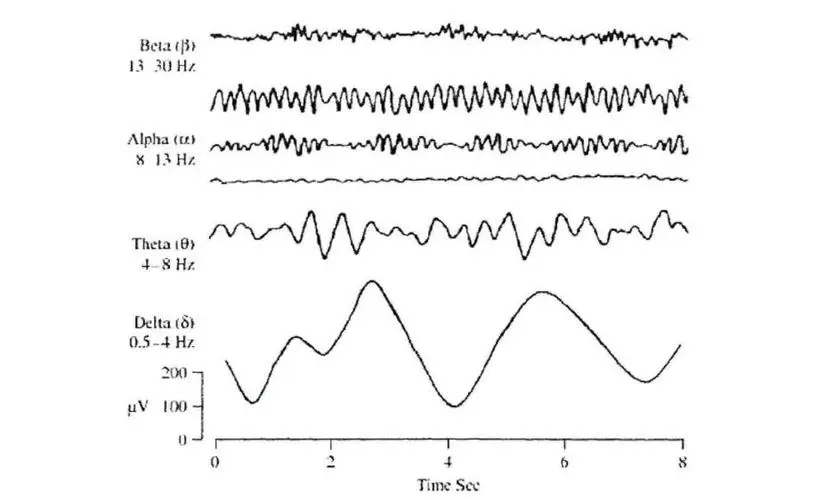

脑电图(EEG)是由大脑神经元活动产生的电位合成,它包含了丰富的大脑活动信息。脑电图在脑部疾病的医学诊断、功能恢复、疲劳驾驶的脑电活动监测、脑-机接口(BCI)以及其他脑科学研究中都有广泛应用。对于脑电信号的研究离不开脑电信号的采集,而脑电信号的采集则依赖于脑电采集系统。传统的脑电采集系统虽然能够在采集精度上满足医疗和研究的需求,但其体积大、操作复杂、功耗高等缺点限制了其应用范围。因此,设计出一种体积小、功耗低、操作方便的脑电信号采集系统具有重大的实际意义和应用价值。由于脑电信号极其微弱,加上人体阻抗的特性、外部和内部的干扰等因素,传统的脑电采集系统需要通过复杂的放大滤波电路设计来满足脑电信号采集的需求。然而,这样的设计会导致电路板体积过大、功耗高,不利于实现采集系统的便携化。

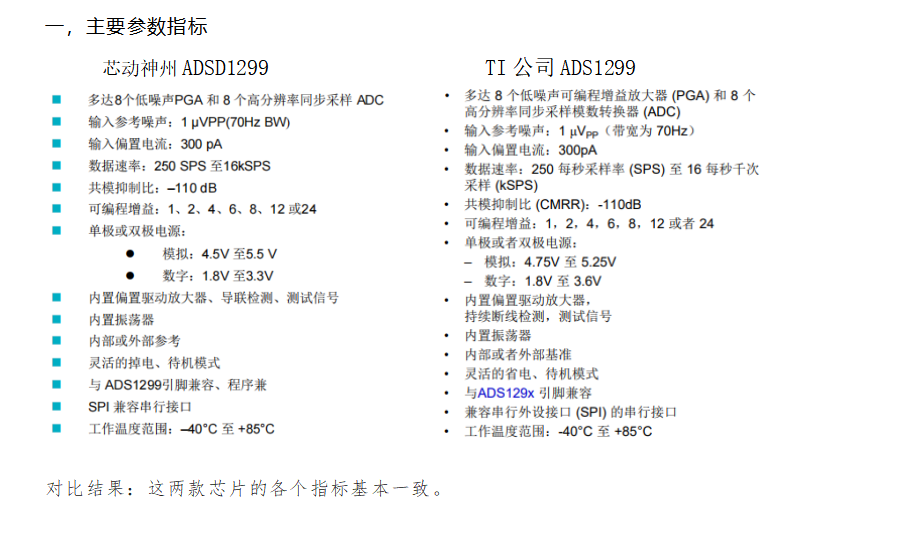

芯动神州推出的专门用于脑电信号采集的模数转换芯片ADSD1299,以高精度、便携式、低功耗的脑电采集系统研制为背景,采用该款芯片作为核心器件设计出可穿戴式脑电信号采集系统前端。

可穿戴式脑电采集系统设计方案

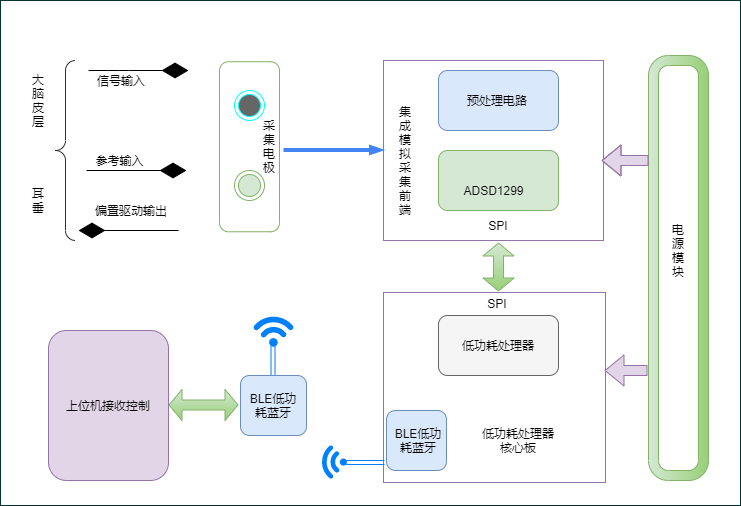

图1 穿戴式脑电采集系统框图

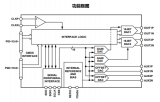

可穿戴式脑电信号采集设备由若干部分组成,包括脑电导联接口、ADSD1299集成模拟采集前端、核心板控制模块、BLE蓝牙模块、电源模块和上位机部分组成,如图1所示。

该系统是一个低功耗的嵌入式处理系统,核心板控制模块通过低功耗蓝牙BLE模块与上位机进行通信,根据上位机的指令控制ADSD1299进行脑电信号的模数转换,并将转换后的脑电信号数据通过蓝牙发送到上位机。该系统解决了传统脑电采集系统在时间和空间上的局限性,满足了脑电采集所需要的便携式、可移动、低功耗以及实时性等特点。该系统中模拟前端部分是保障系统整体性能的关键,芯动神州的ADSD1299为核心器件,其具有如下突出的特性:

具有8个低噪声可编程放大器(PGA,放大倍数1~24倍可调)与8个同步采样模/数转换器(ADC),模/数转换速率介于250 S/s~16 kS/s之间,不超过8 kS/s时其精度为24 bit。

每个通道的功耗仅有5 mW,共模抑制比(CMRR)高达-110 dB,直流输入阻抗高达1 000 MΩ。

内置偏置驱动放大器和持续断电检测(LEAD-OFFDetection)功能。

这些特性保证了加入很少的元器件即可搭建脑电信号模拟采集前端。

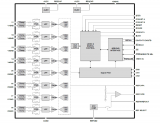

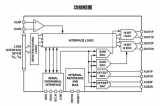

ADSD1299内部结构描述

ADSD1299的输入端采用差分方式输入,每个输入端都集成有EMI滤波器,能有效地抑制外部射频干扰。此外,它具有灵活的路由交换器(MUX),可以将任何输入连接到放大器(PGA)的输入端。同时,它还集成有持续断电检测(Lead Off)电路,可以随时监测电极是否断开。内部集成了8路并行的PGA和ADC,可以提供很高的采集转换精度。内部还集成有偏置驱动放大器,可以有效抑制共模干扰噪声。采用SPI串行通信方式设置内部控制用寄存器并输出数字信号,当芯片完成一次采集时,芯片会拉低引脚来通知处理器可以通过SPI读取数据。

集成模拟前端脑电检测电路设计

脑电检测电路基于芯动神州公司推出的集成模拟前端芯片ADSD1299进行设计。ADSD1299内部器件噪声低于1uV,并且具备脑电采集所需的全部常用功能。并且以通道正常运行时消耗 5 mW 的低功耗特性和高集成度特点,能够大幅度缩小板级空间,显著降低整体成本,构建可扩展的脑电采集系统。针对脑电信号微弱(0.5 uV~100 uV)的特性,传统的采集前端通常由模拟抗混滤波器、多级放大电路和陷波电路等来提高信号的信噪比,这也是导致其体积大,不利于实现便携式设计的主要原因。

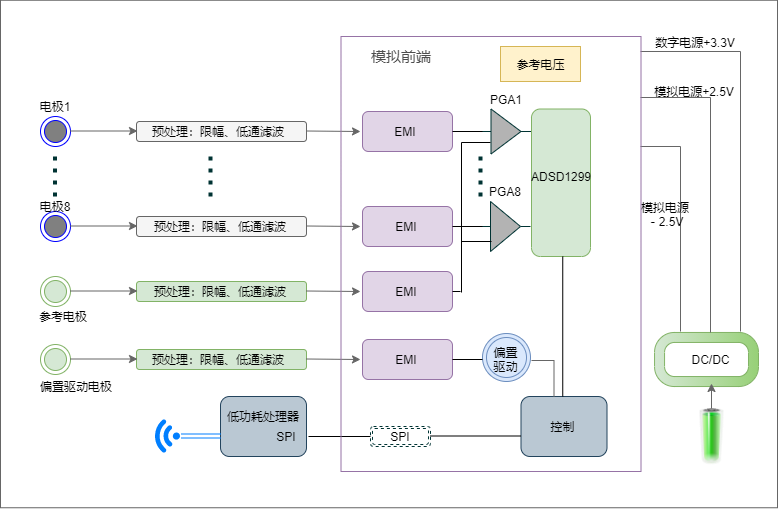

图2前端电路设计结构框图

由于ADSD1299在采样频率不超过8 kHz时模数转换精度达到24位,再结合其集成的具有高共模抑制比的差分输入可编程增益放大器(PGA),在前端设计的模拟侧只保留了抗混滤波电路。而基线漂移、陷波等处理根据应用需要在数字侧实现,而且基于过采样技术采用二阶无源RC滤波电路实现抗混滤波,大大简化前端电路设计。其设计结构框图如图2所示。

ADSD1299为差分输入,其共模抑制比(CMRR)高达-110 dB,且其直流输入阻抗高达1 000 MΩ,再配合闭环偏置驱动电路设计,能够很好地保证系统的抗干扰要求;ADSD1299内部含有8个低噪声的可编程增益放大器(PGA)和8个同步采样模/数转换器(ADC),A/D转换精度高达24 bit,当VREF=4.5 V时其信号电压的分辨率为:

VLSB=VREF /(223-1)=0.536uV

如果再将PGA可编程增益控制考虑进去则其信号电压分辨率可以达到0.053 6 uV。

预处理电路设计

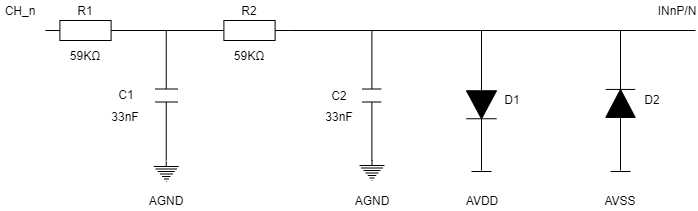

图3信号预处理电路

由于脑电信号频率只有0.5~100 Hz,实验分析的有效范围一般在0.5~30 Hz,在模数转换前必须经过低通抗混滤波的预处理。我们针对每个通道设计了预处理电路,如图3所示, 该电路由二阶无源RC低通滤波和限幅电路组成。

基准电压电路

对于ADC的基准电压选择,既可以选择内部基准电压,也可以选择外部基准电压。为了减小电路规模,使用ADSD1299内部基准电压VREF=4.5V,详细资料请查看数据手册。基准电压是将VREFN与AVSS连接起来并加上限频电容由AVSS产生的,限频电容的作用是使基准电压的输入噪声不会对系统产生干扰,使得频率带宽至少限制在10 Hz以内。

偏置驱动电路

A=2*ZF/RCM

其中,ZF为:

ZF=RF/(1+s*RF-CF)

通过右腿驱动电路设计可以进一步抑制脑电信号的共模噪声。利用ADSD1299内置的偏置驱动放大器加上很少的元器件就可以设计出偏置驱动电路,详细电路请参考数据手册。这个电路是由ADSD1299内置偏置驱动放大器以及外围的REXT、CEXT组成。REXT为反馈电阻。反馈电容CEXT的作用是进行相位补偿,用来防止自激。选择BIAS AMP运放的正参考端BIASREF为(AVDD+AVSS)/2即系统地AGND,能够形成一个闭环回路结构。该闭环回路电路实际上就是一个对消驱动电路,共模信号通过该反馈电路可以在人体上产生一个极性相反的共模信号,将共模干扰噪声限制在一个很窄的范围内,该范围大小取决于该环路的增益A:

系统软件设计

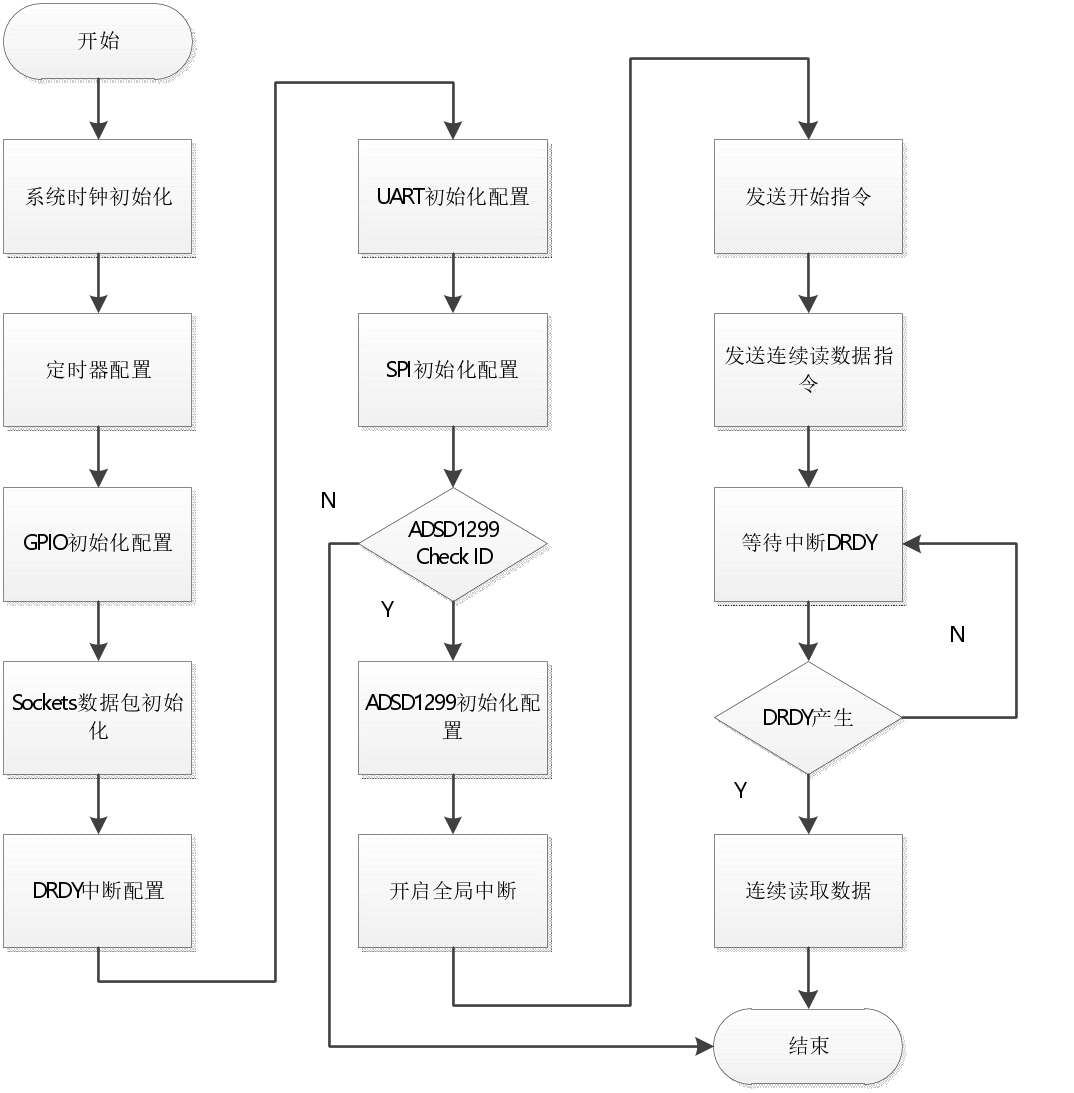

图4系统软件流程图

该系统主要通过低功耗MCU控制器编程实现,图4为系统的软件程序流程图,设备上电以后,主程序对系统时钟、外设模块所需的GPIO端口、UART、SPI接口进行初始化设置,设置脑电数据包格式,并对数据包进行初始化。初始化完成后开始校验ADSD1299是否工作正常,ID正确后对ADSD1299进行初始化配置,包括ADSD1299的内部功能寄存器和时钟源配置等;以上配置完成后则开启全局中断,发送开始连续读数据操作指令;中断产生则通过SPI连续读取8通道脑电数据;通过串口将数据发送给蓝牙模块,蓝牙模块进行无线数据传输发送给 PC 端上位机进行接收。

ADSD1299芯片设计优势

EEG信号采集是一种强噪声背景下的微弱信号的采集,这对于EEG信号的采集前端电路设计提出了很高的技术要求。利用芯动神州的ADSD1299芯片内部集成的各种特有EEG功能可以大幅简化采集前端设计的电路规模。为设计出新一代的便携式、低功耗、高性能的实时穿戴式脑电采集系统提供了有力的技术支持。

-

芯片

+关注

关注

453文章

50360浏览量

421648 -

电路板

+关注

关注

140文章

4902浏览量

97359 -

穿戴式

+关注

关注

0文章

24浏览量

10065

原文标题:芯动神州发布ADSD1299助攻穿戴式脑电采集系统

文章出处:【微信号:ickey360,微信公众号:芯三板】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

使用两片ADS1299搭建电路,为什么采集不到脑电信号?

用ADS1299的6通道芯片进行脑电采集,通道的N极不连接,拟通过SRB1连接到通道N极,怎么配置寄存器?

ADS1299采集脑电信号有尖峰,不光滑是什么原因导致的?如何解决?

使用16片ADS1299做128路脑电采集, 脑电帽上有128个电极+1参考电极, 电极如何接入到ADS1299呢?

【蓝牙4.1申请】基于蓝牙的头戴式脑电采集模块

应用于穿戴脑机接口的专用脑电EEG传感芯片KS1092

TI ADS1299的国产替代方案-ADSD1299芯片

芯动神州发布ADSD1299助攻穿戴式脑电采集系统

芯动神州发布ADSD1299助攻穿戴式脑电采集系统

评论