FPGA中的晶振大小多少比较合适?为什么会用到两个晶振

FPGA (Field-Programmable Gate Array) 是一种可编程逻辑芯片,它可以根据用户的需要重编程实现不同的功能。FPGA 的性能和功能主要由内部的晶振频率决定。因此,在 FPGA 设计中,选择合适的晶振非常重要。

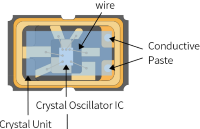

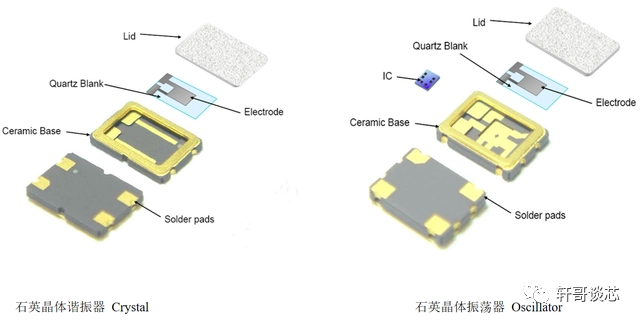

晶振的作用是为 FPGA 提供一个稳定的时钟信号。FPGA 的内部逻辑由时钟信号驱动,如果时钟信号不稳定,就会导致 FPGA 内部逻辑错误,从而影响其性能和正确性。因此,选择合适的晶振频率至关重要。

晶振的大小与其频率有关。一般来说,FPGA 需要的晶振频率越高,晶振就越小,这是由于晶体振荡器的电容和电感与频率成反比例关系。比较常用的晶振频率是 50MHz、100MHz、125MHz、150MHz、200MHz 等。选择哪个频率的晶振取决于应用程序的需求和 FPGA 的性能。

对于一些简单应用场景,50MHz 的晶振已经足够满足要求。而对于一些高性能应用,需要使用更高频率的晶振,比如 200MHz。对于一些需要精确计时的应用,需要选择更精准的晶振,并使用 PLL (Phase-Locked Loop) 进行校准。

在某些情况下,可能需要使用两个晶振。一个晶振用于 FPGA 的时钟,另一个晶振用于与 FPGA 进行通信的接口芯片的时钟。这是因为,接口芯片的时钟可能与 FPGA 不同步,如果共用一个晶振可能会导致通信错误。

总之,选择合适的晶振频率和数量,是 FPGA 设计中非常重要的一环。需要综合考虑应用场景、性能要求、计时精度等因素。

-

FPGA

+关注

关注

1628文章

21728浏览量

602948 -

晶振

+关注

关注

34文章

2859浏览量

68000

发布评论请先 登录

相关推荐

FPGA中的晶振大小多少比较合适?为什么会用到两个晶振?

FPGA中的晶振大小多少比较合适?为什么会用到两个晶振?

评论