请问异步FIFO的溢出操作时怎么样判断的?

异步FIFO是数据传输的一种常用方式,在一些储存器和计算机系统中,常常会用到异步FIFO。作为一种FIFO,异步FIFO经常面临两种情况:溢出和空槽位。

当异步FIFO溢出时,通常是指FIFO写满了数据,但是接下来还有新的数据要写入,此时就需要进行溢出操作了。判断异步FIFO的溢出操作一般有三种方式:

1. 基于阈值的判断方式

基于阈值的判断方式指的是在FIFO中设置一个阈值,当FIFO中的数据量超过设定的阈值时,就认为FIFO已经溢出。这种方式的优点是简单易懂,缺点是需要对设定的阈值进行调整,才能保证判断的准确性。如果阈值过大,就会浪费空间,如果阈值过小,FIFO容易被误判为溢出。

2. 基于信号的判断方式

基于信号的判断方式指的是添加控制信号,当FIFO写满时向控制信号发送一个信号,然后再读取该信号来确定FIFO是否溢出。这种方式的优点是比较灵活,FIFO溢出的判断可以通过控制信号与读取数据信号来实现。缺点是需要额外添加控制信号,增加了实现的复杂度。

3. 基于计数器的判断方式

基于计数器的判断方式指的是通过计数器来记录FIFO中元素的个数,当计数器的数值达到FIFO的最大容量时,就可以判断FIFO溢出了。这种方式的优点是比较简单,通过计数器的方式可以精确计算FIFO中的元素个数,保证判断的准确性。缺点是需要将计数值与FIFO最大容量值相匹配,这需要预先知道FIFO的最大容量。

总的来说,三种判断方式各有优劣,需要根据实际情况进行选取。可以通过FIFO的容量、控制信号和计数器等属性来决定如何进行溢出操作的判断,以保证FIFO的正常运行。

-

fifo

+关注

关注

3文章

407浏览量

45911 -

计数器

+关注

关注

32文章

2321浏览量

98580

发布评论请先 登录

飞凌嵌入式ElfBoard-文件I/O的深入学习之异步I/O

从底层解读labview的TDMS高级异步写入的工作原理

【RK3568+PG2L50H开发板实验例程】FPGA部分 | ROM、RAM、FIFO 的使用

stm32H743定时器溢出的原因?怎么解决?

cy7c68013a异步slave fifo模式,外部mcu无法读写fifo怎么解决?

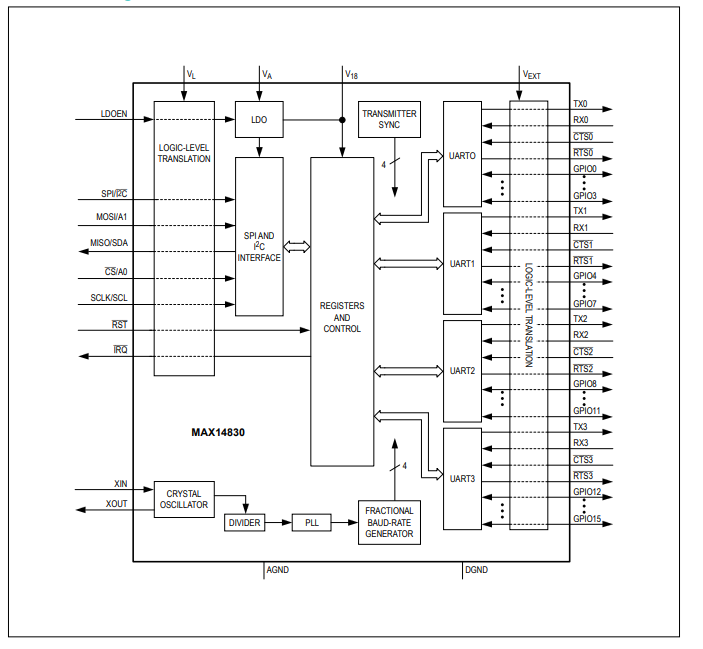

MAX14830四通道串行UART,具有128字FIFO技术手册

MAX3109双通道串行UART,带有128字FIFO技术手册

请问异步FIFO的溢出操作时怎么样判断的?

请问异步FIFO的溢出操作时怎么样判断的?

评论