摘要:

芯片粘接质量是电路封装质量的一个关键方面,它直接影响电路的质量和寿命。文章从芯片粘接强度的失效模式出发,分析了芯片粘接失效的几种类型,并从失效原因出发对如何在芯片粘接过程中提高其粘接强度提出了四种解决途径和方法,对提高芯片粘接强度和粘接可靠性具有参考价值。文章还指出了芯片粘接强度测试过程中的一些不当或注意点及其影响,并对不当的测试方法给出了改进方法,能有效地避免测试方法不当带来的误判。

1 引言

在集成电路芯片装片或封装后的筛选中,以及电路考核鉴定验收时,常需要确定芯片粘接质量是否符合要求。最有效的方法之一就是在同一批封装(或装片)的电路中,随机抽取一定数量的电路,并对这些电路进行抗剪或抗拉强度测试,根据测量结果和分离界面的形貌来判断芯片粘接质量,并分析芯片粘接情况,特别是粘接脱开的相关因素,从而对芯片粘接材料、装片工艺等加以控制和优化来提高芯片粘接强度,满足芯片粘接可靠性的要求。

2 芯片粘接失效模式

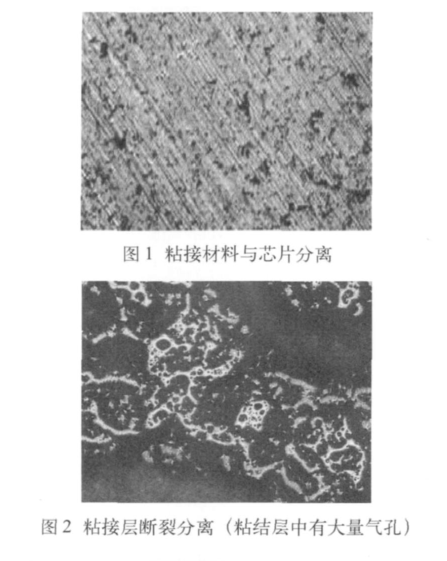

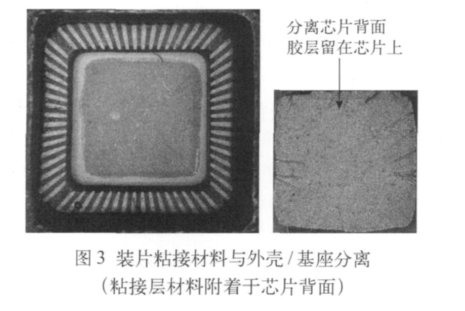

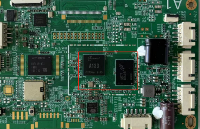

聚合物类材料装片影响芯片粘接强度的因素教较多,涉及粘接材料、工艺条件、外壳衬底 / 基座的质量和芯片背面的粗糙度、洁净度等。芯片粘接的失效模式主要有:(1)从芯片硅表面与装片粘接材料分离;(2)装片粘接材料层断裂;(3)装片粘接材料与外壳衬底 / 基座分离。参见图 1、图 2、图 3。

根据芯片失效的脱落界面及形貌分析脱落的原因和可能性,再针对引起失效的原因在生产中加以控制和解决。

3 芯片粘接强度提高途径

增强芯片粘接强度可通过对装片粘接材料的优选、粘接工艺方面的优化和控制来提高粘接质量,保证高可靠的粘接强度。

3.1 芯片背面洁净度、粗糙度的控制

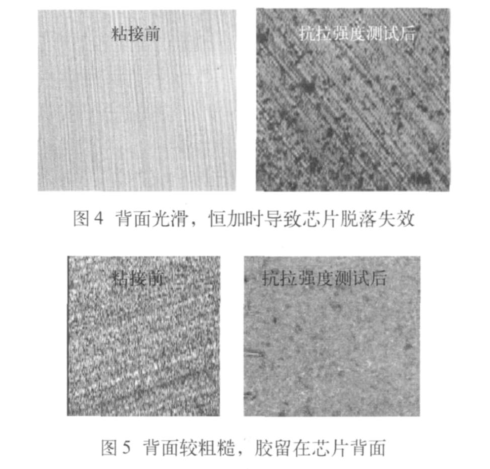

为降低封装热阻、厚度以及封装划片等工艺的要求,前道工艺制造的圆片较厚,均需进行减薄。在圆片背部磨削减薄时,芯片背面即芯片的粘接面会有微细的硅粉尘存在,微细的硅粉尘使芯片本体材料不能完全与粘接材料接触,芯片装片后必然会对粘接强度造成影响。减薄后的清洗对提高芯片粘接强度是非常重要的步骤,具备条件的同时还应借助化学方法对硅屑进行充分彻底地清除。减薄时若芯片背面太光,像镜面一样光滑,不利于增大粘接材料与芯片的接触面积,也不利于芯片与胶的鳌合,因此增加芯片粗糙度,可提高芯片的粘接性强度。

图 4 是芯片背面光滑,恒加时导致芯片脱落失效,失效样品芯片背面只有少许导电胶存在;图5样品增加了芯片背面粗糙度,芯片粘接强度得到显著提高,试验后导电胶完全留在芯片背面。

3.2 外壳等在装片前烘烤,增强粘接强度

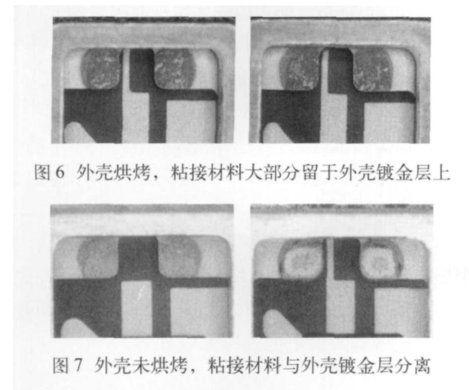

外壳生产过程中如清洗不干净,表面会有沾污或清洗残留物;另外,外壳在贮存过程中,表面会吸附空气中的水汽等,在装片前对外壳进行烘烤等处理,可去除部分外壳生产过程中的残留物及表面吸附的水汽,以提高粘接面的粘接性能。

图 6 是外壳经烘烤后,装片的样品做芯片粘接强度测试的界面,粘接材料大部分留于外壳镀金层上,说明装片粘接材料与镀金基座拥有较好的粘接强度。而未进行烘烤的外壳,装片后强度测试粘接材料与外壳镀金层发生了完全分离的现象,这说明了粘接材料与镀金层之间的接触不良,造成两者之间强度较弱,参见图 7。

3.3 优选芯片粘接材料以提高粘接强度

在气密封装中,粘接剂需具备:高的粘附强度、热分解温度及高稳定性、少量甚至不含溶剂、低的水汽含量。

为了提高电路芯片的粘接强度,对芯片粘接材料需进行优选,选择较高的温度 T g 、与芯片及基板匹配的低 CTE 膨胀系数且弹性模量低的粘接材料,使粘接后的粘接层的内应力较低;同时,选择在固化过程中和固化后重量损失率低的粘接材料,材料结构致密且固化后孔隙率较低,从而提高芯片的粘接强度,保证芯片粘接的可靠性。

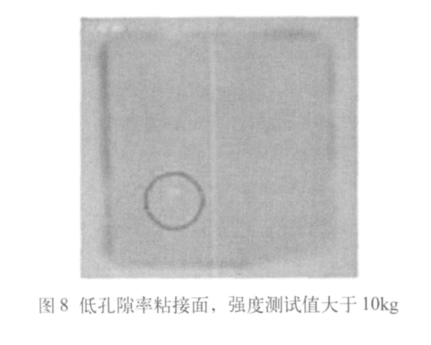

图 8 使用的高温导电胶装片粘接材料热失重百分比低、固化后的组织结构致密,从 X 射线图片中可看到,芯片粘接层中只有个别的小孔隙,芯片有效粘接面积在98%以上,5.0mm×5.0mm的样品抗剪、抗拉强度测试值都大于10kg,满足了芯片粘接可靠性要求。

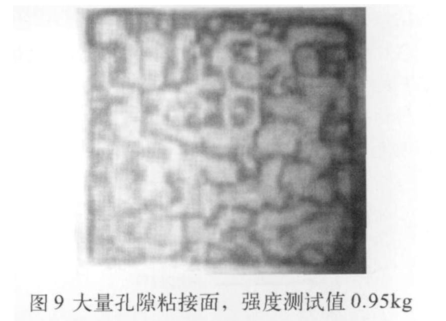

图 9 使用的绝缘玻璃粘接材料,固化后粘接材料中存在大量气孔,粘接层强度低,分离基本在粘接层中,大部分样品抗剪、抗拉强度测试参数小于2.0kg,不能满足芯片粘接可靠性要求,此种材料完全不能应用于有强度要求的粘接。

3.4 控制粘接剂固化后的余留厚度,提高粘接可靠性

装片操作中如将粘接层设置过薄,必将影响芯片的粘接强度,合适的粘接层厚度在芯片 - 粘接层受到外界的各种应力时可起到应力缓冲的作用,从而提高粘接的可靠性。

粘接层厚度需根据芯片的尺寸和粘接材料固化后的收缩特性来设置粘接剂的厚度。一般情况下,芯片面积与粘接剂的厚度近似成正比,芯片面积大粘接层厚度可适当厚一些。粘接材料在固化过程中会有部分溶剂或低分子挥发物挥发掉,固化后的厚度会比分配时的厚度要薄一些,因此在设置时需根据粘接剂固化前、后的参数变化值,确定粘接层厚度,从而提高芯片粘接的强度要求。

3.5 优化固化工艺曲线,降低粘接材料中孔隙率

固化是装片工艺的关键所在,粘接层中的孔隙率若偏高,使芯片有效粘接面积降低,从而影响芯片的粘接强度;另外大量孔隙的存在使芯片的导热性能下降,使器件的可靠性受影响,因此对粘接层中的孔隙率要加强控制。

粘接材料在固化期间,溶剂或水汽会释放出来,若气体聚集则会产生空隙,固化后孔隙将残留在粘接层中,从而影响芯片的粘接强度。针对这种情况,需优化固化工艺曲线,使粘接材料中的挥发性气体均匀逸出,从而不会因升温过快使胶体表面先“结壳”,加剧产生孔隙而影响结合强度。固化后通过 X 射线仪来检查和分析粘结层以及粘接界面是否存在孔隙等,来确定固化曲线设置的优劣。

4 芯片粘接强度的测量方法及影响

4.1 芯片粘接强度的测量方法

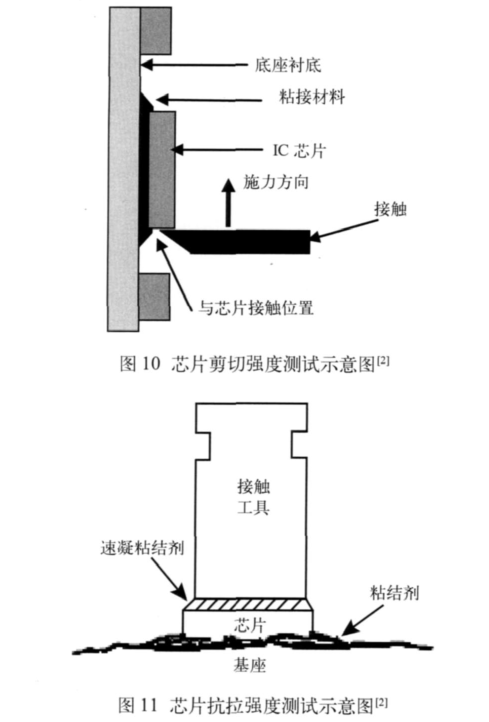

控制芯片粘接强度,必须对芯片粘接进行正确、有效地测量。芯片粘接强度的测量方法有两

种 [2] :剪切强度测试、抗拉强度测试。芯片剪切强度测试如图 10 所示。施加平行于芯片的长边的力,将芯片剪切下来的力的大小直接反映出芯片与粘接层、粘接层、粘接层与外壳 / 基座间的粘接强度。

芯片抗拉强度测试如图11 所示。在芯片上施加垂直于表面的作用力,以检测粘接面积大于5mm 2 的芯片与粘接层、粘接层、粘接层与外壳 / 基座间的附着强度。

4.2 测量中需要注意的几个问题

为了能够正确地测量出芯片的剪切强度,测量时需要注意以下几个问题:

(1)接触工具的移动不要过快(负载加载速率)。否则芯片容易被剪碎或造成测量失败,也更易使测量值比实际值大。

(2)测试接触工具与芯片接触位置至少要大于芯片厚度的1/2,如果测试接触工具与芯片接触的位置小于芯片厚度的1/2,芯片容易被剪碎;但也不能接触粘接层,更不能与外壳 / 基座接触。否则,测试值不能真实反应芯片实际粘接强度。

(3)施加的力的方向始终保持与外壳 / 基座上的芯片平行。如果施力的方向不平行,芯片边缘容易被剪碎,且测试值会偏离芯片实际的剪切强度。

(4)芯片或芯片连同粘接层已从外壳/基座上分离时,测量的接触工具要及时停止,以防止其继续移动碰到外壳/基座或其他物体,避免继续施力使测量值大于实际抗剪强度。

(5) 芯片较薄(如180μm等)、芯片面积过大(如5.0mm×5.0mm)则不适合使用抗剪强度测试来检测芯片的粘接质量,因测试接触面相对较小,硅芯片在分离前已经碎了,无法测量出剪切强度。

芯片抗拉强度测量还需注意:

(1)接触工具与芯片的接触面积应≥60% 的芯片面积,否则不能真实反映粘接强度,为不可信数据,其远小于真实值。

(2) 快速凝固粘结剂不允许流出芯片表面,否则快速凝固粘结剂会将芯片与装片粘接材料、外壳/基座粘接,测试施加的力会大于芯片本身实际的抗拉强度,此测试数据也应作无效处理。

5 结论

根据芯片的强度测试,对芯片施加力的大小、及在该力作用下产生的失效类型(如出现失效)以及残留的芯片附着材料和外壳 / 基座各粘接界面的形貌,进行正确的分类并分析引发失效或强度弱的相关因素,找出相关原因,针对性地从粘接材料、封装工艺实施改进,从而提高芯片粘接的可靠性。

审核编辑:汤梓红

-

芯片

+关注

关注

458文章

51526浏览量

429491 -

半导体

+关注

关注

335文章

27970浏览量

225146 -

失效模式

+关注

关注

0文章

22浏览量

10228

原文标题:芯片粘接失效模式及粘接强度提高途径

文章出处:【微信号:半导体封装工程师之家,微信公众号:半导体封装工程师之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

弹性粘接技术在客车上的应用

UV胶水粘接亚克力制品的粘接方法都有哪几种

使用UV胶时如何提高粘度和粘接剥离的强度

如何选择合适的塑料粘接UV胶水

快干胶的粘接影响因素有哪些呢

半导体芯片封装胶水的粘接原理

芯片粘接失效模式和芯片粘接强度提高途径

芯片粘接失效模式和芯片粘接强度提高途径

评论