谈到SystemVerilog,很多工程师都认为SystemVerilog仅仅是一门验证语言,事实上不只如此。传统的Verilog和VHDL被称为HDL(Hardware Description Language,硬件描述语言),而SystemVerilog则是HDVL(Hardware Design and Verification Language,硬件设计与验证语言)。由此可见,SystemVerilog也是可以用于硬件设计的,也是有可综合部分的。SystemVerilog本身由3部分构成:

SV-HDL:用于硬件设计,可综合,是可综合Verilog的加强版;

SV-Assertion:断言;

SV-HVL:用于硬件验证,UVM就是利用此发展而来的验证方法学。

下图显示了SystemVerilog与Verilog可综合的部分。

至此我们已经澄清了一个事实:SystemVerilog是可以用于硬件设计的。那么相比于Verilog,SystemVerilog在硬件设计部分有哪些优势呢?

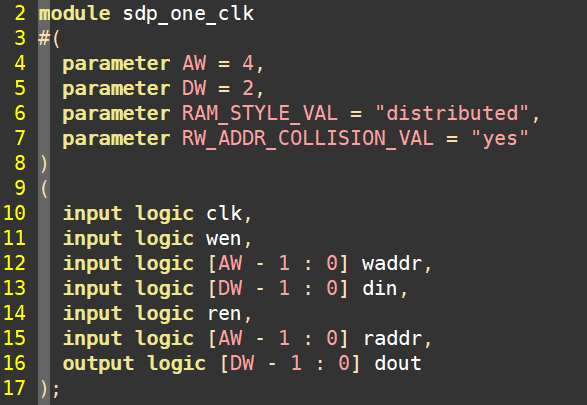

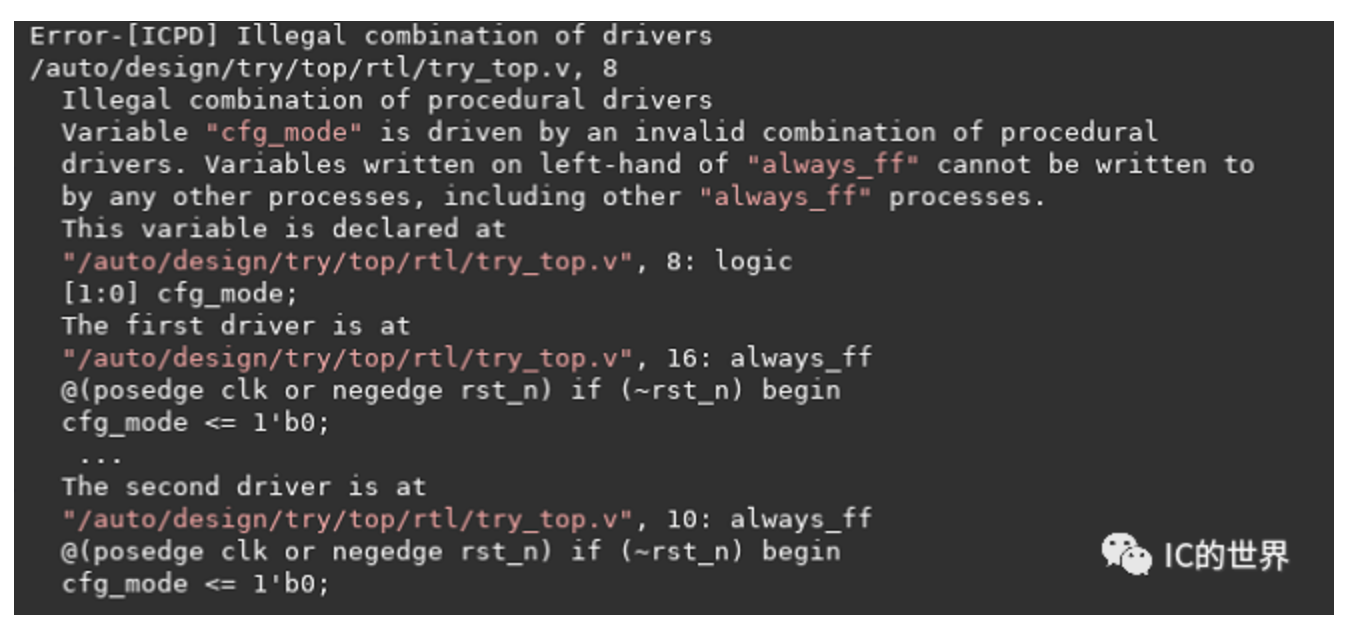

从数据类型的角度看,SystemVerilog引入了4值类型logic,这与VHDL的std_logic是相同的。尽管Verilog中的reg也是4值类型,但在端口声明时,有的需要声明为reg,有的需要声明为wire,内部变量定义亦是如此。同时,reg会让很多初学者误以为该变量对应一个寄存器(register),而事实上,只要是always进程或initial中用到的输出变量都要定义为reg类型。使用logic则避免了这种歧义。如下图所示代码片段,输入/输出都定义为logic类型。

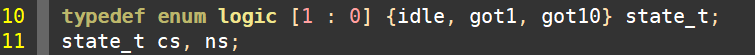

SystemVerilog引入了枚举类型,通过enum定义,也支持用户定义的枚举类型,这使得在描述状态机时更为方便,如下图所示代码片段。同时,SystemVerilog还允许对枚举变量赋值,这样就可以根据场景需要明确指定状态机的编码方式。

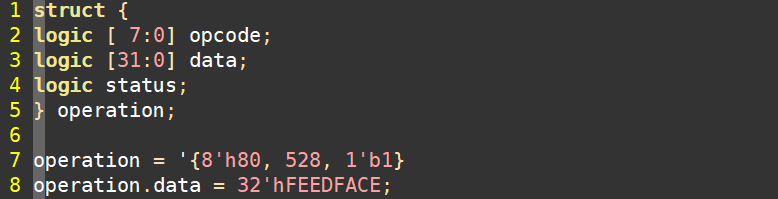

SystemVerilog支持结构体,带来的好处是可以把相关变量绑定在一起,这样使用起来更为直观方便,如下图所示代码片段。可以对整个结构体赋值,如代码第7行所示,也可以对结构体内某个指定变量赋值。struct允许绑定不同类型的数据,而数组则要求数据类型一致,这是两者的关键区别。

同样地,SystemVerilog也支持用户定义的结构体,这便于代码复用。从代码风格角度看,最好将用户定义的结构体在package中进行声明,避免因编译顺序而导致的错误。

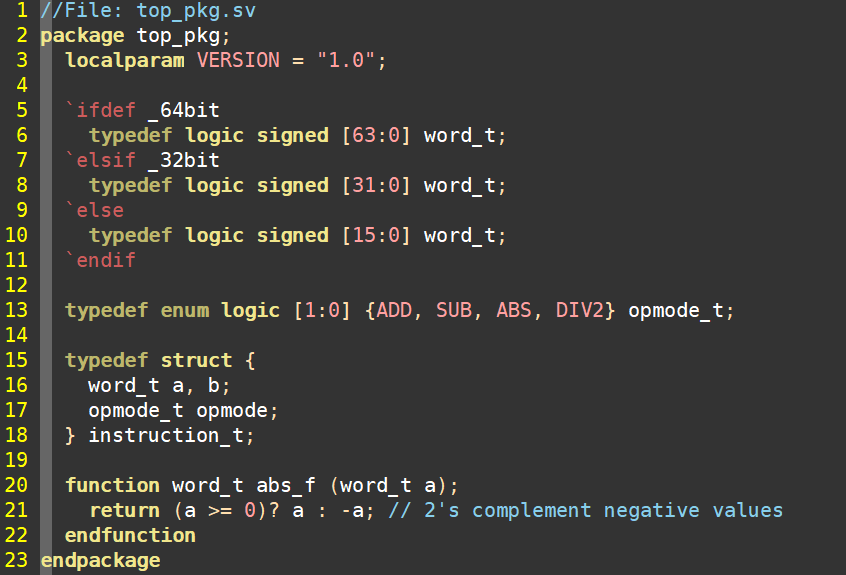

SystemVerilog引入了package,这样同一个声明可以被不同模块使用,避免了重复定义,如下图所示代码片段。可以在package中声明参数、结构体、函数等。具体案例可阅读这篇文章。

说说SystemVerilog的Package

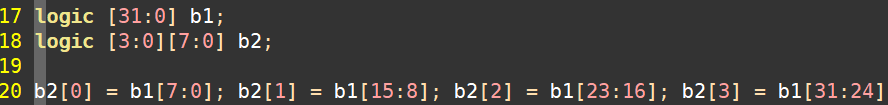

SystemVerilog支持packed array,本质上是对vector的增强。如下图所示代码片段。b1是位宽为32的向量,b2本质上也是位宽为32的向量,只是将b2按位域进行分割,如代码第20行所示。这样在引用时更为方便,比如获取b2[1]其实就是获取b1[15:8]。

对于常规数组,也就是unpacked array,SystemVerilog支持类似于C语言的声明方式,如下图所示代码片段。这两行代码是等效的,显然后者声明更为简洁。

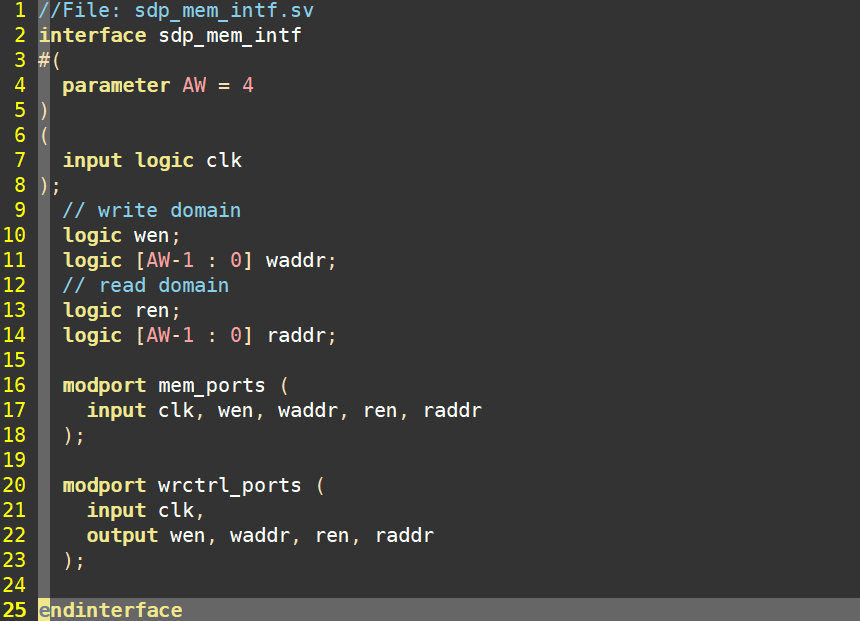

另外,SystemVerilog还引入了interface,这对于描述互连较多的模块时更为友好方便,具体案例可阅读这篇文章。

说说SystemVerilog的Interface

审核编辑:汤梓红

-

Verilog

+关注

关注

28文章

1351浏览量

110074 -

System

+关注

关注

0文章

165浏览量

36928 -

HDL

+关注

关注

8文章

327浏览量

47376 -

硬件设计

+关注

关注

18文章

396浏览量

44563 -

验证语言

+关注

关注

0文章

3浏览量

6620

原文标题:SystemVerilog不只是用于验证(1)

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

做FPGA工程师需要掌握SystemVerilog吗?

SystemC 和SystemVerilog的比较

SystemVerilog设计语言

SystemVerilog的正式验证和混合验证

SystemVerilog语言介绍汇总

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计

FPGA学习-SystemVerilog语言简介

systemverilog:logic比reg更有优势?

systemverilog:logic比reg更有优势

SystemVerilog相比于Verilog的优势

SystemVerilog在硬件设计部分有哪些优势

SystemVerilog在硬件设计部分有哪些优势

评论