一:Boundary Scan的基本概念及应用

-> 什么是Boundary SCAN?

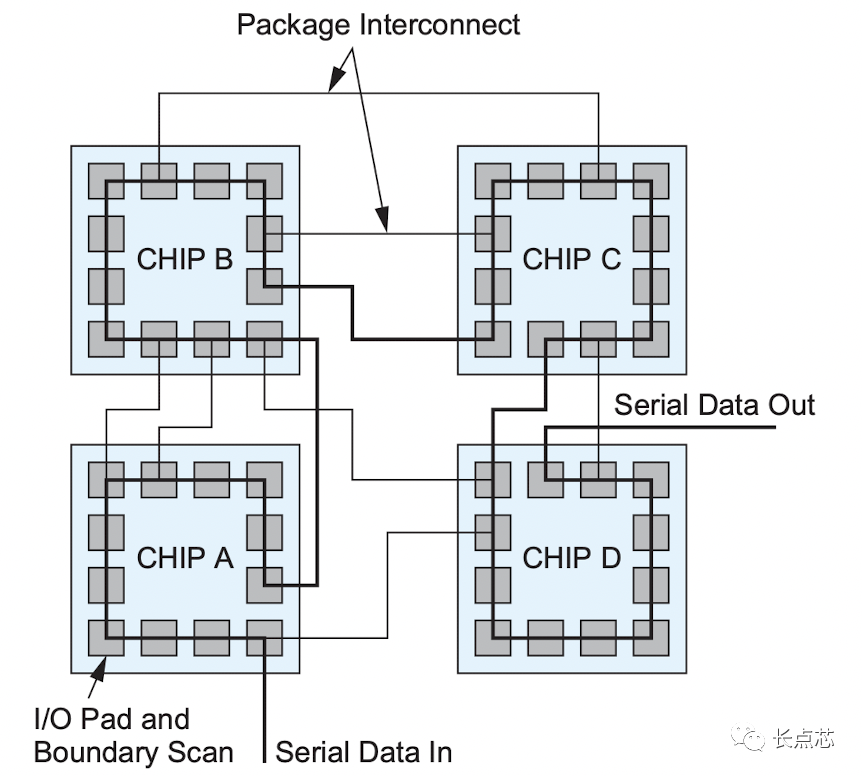

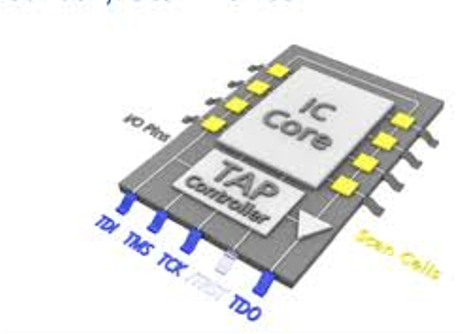

首先我们都知道BSCAN是一种用于测试和验证集成电路的技术。在集成电路中,有许多引脚***(pins)*** 用于与其他器件进行通信和连接。BSCAN 通过在芯片引脚之间添加可控的扫描链***(Scan Chain)*** ,使得我们能够在测试和调试时以串行方式访问每个芯片引脚。如下图

-> BSCAN诞生的契机是什么呢?

电路板的日益复杂和 surface mount technologies (表面贴装技术)等技术的转变导致系统设计师们达成一致,采用了一种统一的基于扫描的方法,称为边界扫描***(boundary scan)*** ,用于在电路板(任何系统)级别上测试芯片。

-> BSCAN为芯片验证带来了什么?

1. 连通性测试:

假设你在设计一个SoC,其中涉及许多引脚用于连接不同的子系统。使用边界扫描,你可以测试这些引脚之间的连通性。例如,你可以加载一个测试模式,通过观察TDO信号,检查引脚是否按预期连接,是否存在开路或短路问题。

2.故障定位:

在芯片制造过程中,可能会出现一些未预料的故障,例如焊接问题或晶体管故障。通过加载适当的测试模式,你可以观察故障信号在扫描链上的传播路径,从而精确定位故障的位置,加速故障排除过程。

3.逻辑验证:

在芯片设计的早期阶段,你可以使用边界扫描来验证芯片的基本逻辑功能。通过加载测试模式,观察输出是否与预期相符,以验证芯片的功能性。

4.硬件调试:

假设你遇到了一些奇怪的硬件问题,如时序问题或逻辑错误。通过在扫描链上加载特定的测试模式,你可以观察信号在芯片内部的传播路径,有助于理解信号的行为,从而更有效地进行硬件调试。

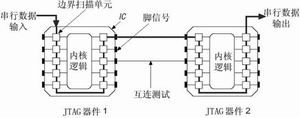

5.芯片级联测试:

在多芯片系统中,边界扫描可以用于测试不同芯片之间的连接性。通过将多个芯片的边界扫描链连接在一起,你可以检测引脚和信号在整个系统中的传输情况。

总之,边界扫描在SoC设计验证中是一项强大的工具,可以帮助芯片验证工程师在不同阶段进行测试、调试和验证,从而提高芯片的质量和可靠性。

二:Boundary Scan的硬件实现

边界扫描的核心思想是在SoC芯片的引脚周围添加一个可控的扫描链,将芯片内部的逻辑电路与扫描链相连。这个扫描链由一系列的Scan Cells (扫描单元)组成,每个扫描单元可以存储一个比特的数据。通过操控TAP(Test Access Port) 控制器,我们可以在扫描链上加载测试模式,然后观察测试模式在芯片内部的传播路径,从而实现测试、调试和验证。

没错,下面就要详细介绍一下我们的主角TAP了!

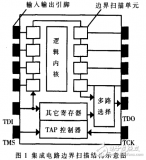

TAP控制器是边界扫描的核心,它负责管理扫描链的操作。TAP控制器通过四个或个基本信号进行操作测试访问端口。

- TCK(Test Clock):用于控制扫描链的时钟信号。

- TMS(Test Mode Select):用于控制TAP控制器状态机的状态切换。

- TDI(Test Data Input):用于将数据加载到扫描链中。

- TDO(Test Data Output):用于从扫描链读取数据。

- TRST(Test Reset):用于异步复位TAP控制器,如果芯片没有自动生成上电复位信号的话。

不过一般我们用到前面四个就够了,下面是一个基本的TAP架构图。

下面我们就按照这张图剖析一下TAP的组成部分。

1. TAP控制器(TAP Controller):

TAP控制器是TAP的核心,负责控制扫描操作的状态转换和时序。它通过TCK(Test Clock)、TMS(Test Mode Select)、TDI(Test Data Input)和TDO(Test Data Output) 等信号,实现从一个状态到另一个状态的转换,以便执行不同的操作,如扫描测试数据或读取测试结果。TAP控制器按照JTAG(Joint Test Action Group) 标准定义了一组状态,如Test-Logic-Reset状态、Run-Test/Idle状态等。

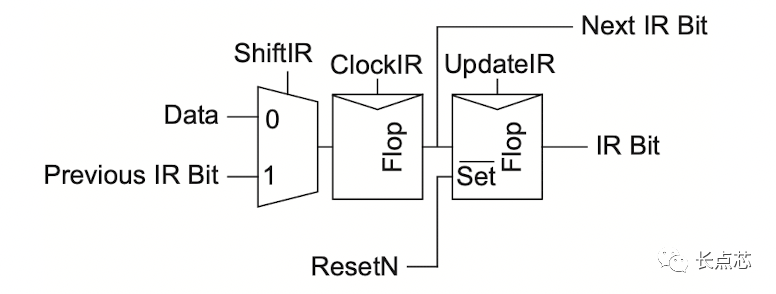

2.指令寄存器(Instruction Register):

指令寄存器用于存储和加载TAP控制器的指令。在测试和调试过程中,可以通过加载不同的指令来控制芯片的操作。指令寄存器的位数决定了可以定义的不同指令数量,从而支持多种测试模式和操作。

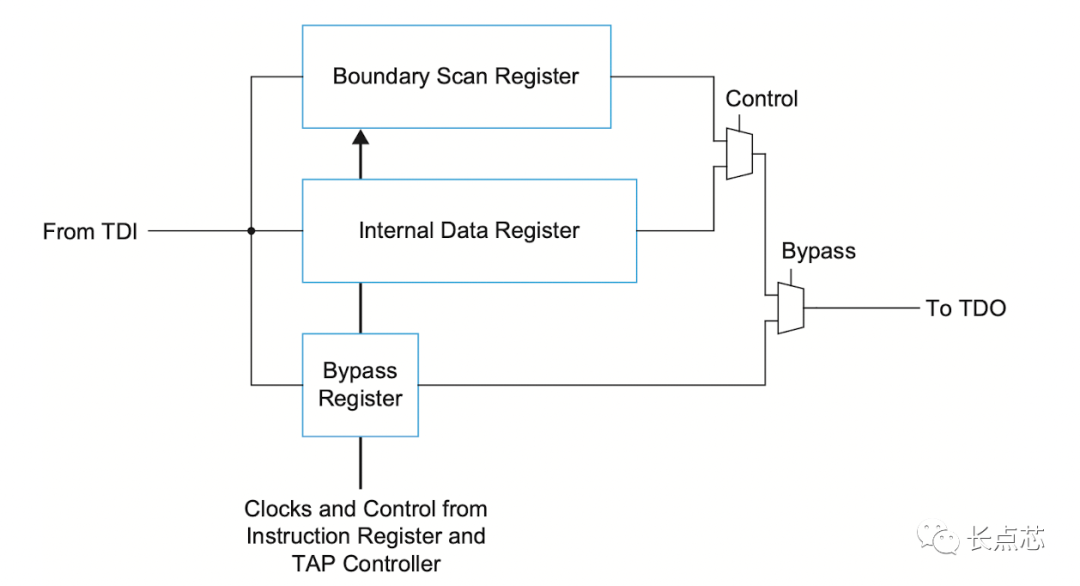

3. 测试数据寄存器(Test Data Register):

测试数据寄存器用于存储测试模式数据,它是扫描链(Scan Chain)的一部分。测试数据可以被输入到芯片进行测试,也可以从芯片中读取出来作为测试结果。测试数据寄存器又分为不同的子寄存器,包括边界扫描寄存器、旁路寄存器和TDO驱动器。

3.1. 边界扫描寄存器(Boundary Scan Register):

边界扫描寄存器是边界扫描技术的关键,用于在芯片的引脚之间插入可控的测试逻辑。它允许在芯片的输入和输出之间插入额外的逻辑电路,以便执行连通性测试、故障定位等操作。边界扫描寄存器存储了扫描链上的测试模式数据,可以通过TAP控制器进行加载和读取。

3.2. 旁路寄存器(Bypass Register):

旁路寄存器用于绕过边界扫描逻辑,将芯片的输入直接连接到输出。当不需要执行边界扫描时,可以通过加载指令将旁路寄存器中的数据传递给TDO输出,从而绕过边界扫描逻辑。

3.3. TDO驱动器(TDO Driver):

TDO驱动器用于控制TDO输出信号的驱动。在扫描链操作期间,TDO驱动器负责将测试模式数据从边界扫描寄存器或旁路寄存器传递到TDO输出。TDO驱动器还可以根据TAP控制器的状态控制TDO输出信号的开关。

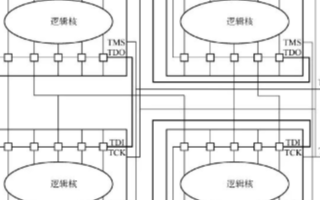

这些组成部分共同构成了TAP结构,使得边界扫描技术成为一种强大的芯片测试和验证工具,为集成电路设计和制造过程提供了可靠的测试手段。下图展示一个完整的Boundary SCAN。

结语

Boundary SCAN作为现代芯片设计验证领域的重要工具,为芯片工程师提供了强大的测试和调试手段。它通过TAP控制器、扫描链和测试模式生成器的协同工作,实现了对芯片内部功能和连通性的全面测试。

-

集成电路

+关注

关注

5381文章

11381浏览量

360847 -

晶体管

+关注

关注

77文章

9633浏览量

137836 -

芯片制造

+关注

关注

9文章

610浏览量

28771 -

边界扫描

+关注

关注

1文章

32浏览量

15015 -

Scan

+关注

关注

0文章

12浏览量

3526

发布评论请先 登录

相关推荐

FX3支持IEEE1149的边界扫描测试吗?

如何为第三方设置Zynq 7000系列进行边界扫描?

边界扫描技术及其在VLSI芯片互连电路测试中的应用

基于边界扫描技术的板级测试分析

边界扫描测试技术在带DSP芯片数字电路板测试中的应用解析

TMS320VC5510 GGW BSDL Model边界扫描DSP模型的详细资料概述

JTAG(四) 边界扫描测试技术

边界扫描-Boundary Scan技术及其在芯片测试中的应用

边界扫描-Boundary Scan技术及其在芯片测试中的应用

评论