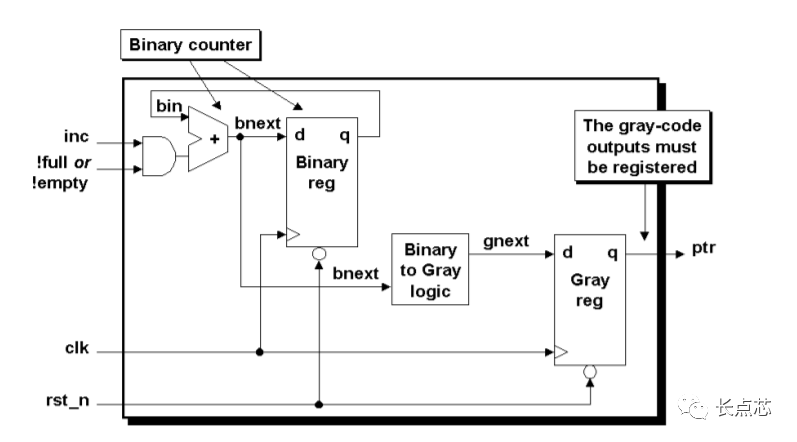

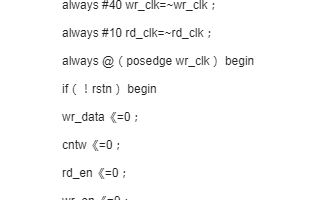

设计者为了提升FIFO的速度使用了将二进制计数器和格雷码计数器结合在一起的方法,从最开始用一组寄存器来进行格雷码到二进制码的转换,二进制码的递增和二进制码到格雷码的转换,到后来的style#2(如图)。

在本篇当中,作者进一步对此设计进行了说明,使用这种格雷码计数器的目的是利用了二进制数进位的机制简化了格雷码到二进制码的转换电路来减少组合逻辑电路,这样整个计数器的工作频率上限就会有所提升。

Dual n-bit Gray Code counter style#2

但是,可以看到这里的设计需要使用两组寄存器,这里可能会体现到PPA trade-off的思想了(因为我也没有实验过这种替换方式会不会带来更大的面积损耗)。不过,对FPGA来讲,FPGA包含着许多寄存器资源,所以使用FPGA来实现这种设计方法就不需要考虑面积上的损耗,更能凸显出速度提升上的优势!

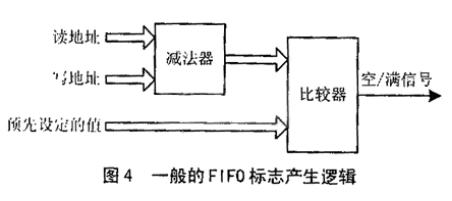

上文说到,设计FIFO中最重要的部分也是最难的部分之一就是如何产生空满标志信号。一种方法就是上一篇提到的使用发送到对面时钟域的同步后的格雷码指针来进行比较,从而判断空满信号的产生。而另外一种方法就是本篇文章所提到的,指针的比较不再是同步的了,而是通过“异步”比较,并判断空满信号。

上篇文章提到的判断空满信号的方法是比较指针是否一样,并通过多增加一个bit位来讨论指针被套圈的问题。不同于上个设计,本篇文章提出了一个更有创意的思路来判断空满信号的产生。

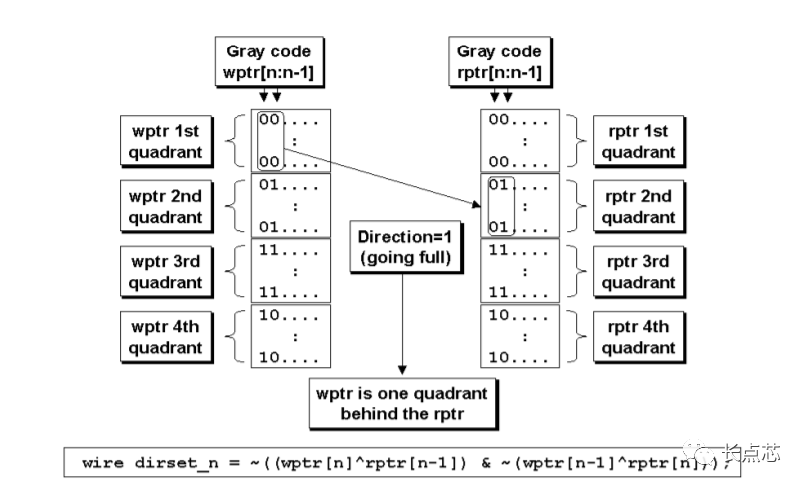

作者将FIFO的地址分成了四个区间并通过编码两个指针计数器最高的两位来比较判断FIFO将要空满的 趋势 。举个栗子,如果写指针落在读指针后面一个区间则表示FIFO将要满,然后当指针重合时则将direction寄存器置位,如下图。

FIFO is going full because the wptr trails the rptr by one quadrant

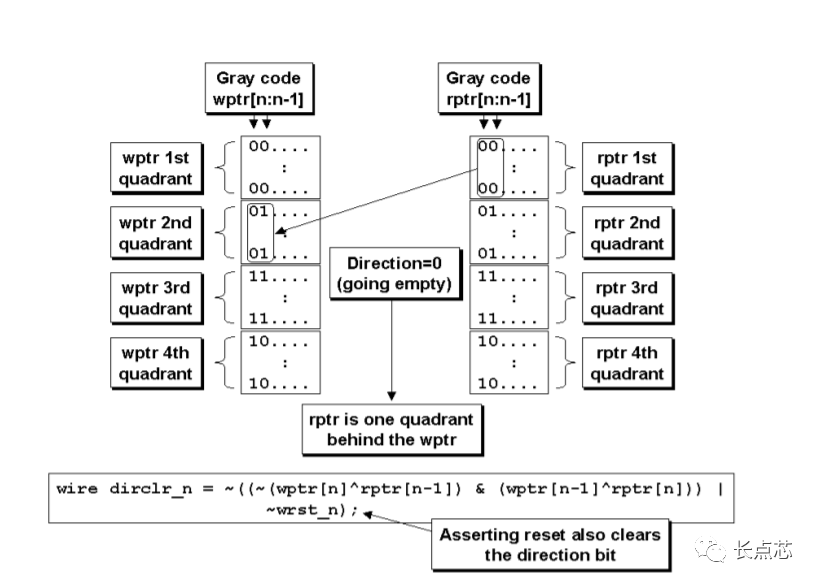

而如果写指针落在读指针前面一个区间则代表FIFO将要空,然后当指针重合的时候则将direction寄存器复位。

FIFO is going empty because the rptr trails the wptr by one quadrant

结语:

这篇文章理解起来可能要比前一篇更难理解一点,给我的感觉就是看起来很晕。没有把握给大家阐明清楚,所以就不再做更深入的探讨了。还是推荐大家如果对这个设计方法感兴趣的话可以读一下原文。

-

编码器

+关注

关注

45文章

3724浏览量

136071 -

寄存器

+关注

关注

31文章

5394浏览量

122199 -

二进制

+关注

关注

2文章

803浏览量

41942 -

FIFO存储

+关注

关注

0文章

103浏览量

6093 -

组合逻辑电路

+关注

关注

6文章

71浏览量

14780

发布评论请先 登录

相关推荐

用FPGA芯片实现高速异步FIFO的一种方法

异步FIFO结构及FPGA设计

一种异步FIFO的设计方法

异步FIFO结构及FPGA设计

基于FPGA的异步FIFO设计方法详解

基于异步FIFO结构原理

关于一种面向异步FIFO的低开销容错机制研究

一种基于FPGA内部存储器的适合音频解嵌的高效异步FIFO设计

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用

同步FIFO和异步FIFO区别介绍

关于另外一种设计异步FIFO的简介

关于另外一种设计异步FIFO的简介

评论