前面的文章中讲到了SOI衬底,见之前文章:

什么是SOI衬底?

但是,在刻蚀SOI衬底时,通常会发生一种凹槽效应,导致刻蚀的形貌与预想的有很大出入。那么什么是凹槽效应?什么原因引起的?怎么抑制这种异常效应呢?

什么是凹槽效应?

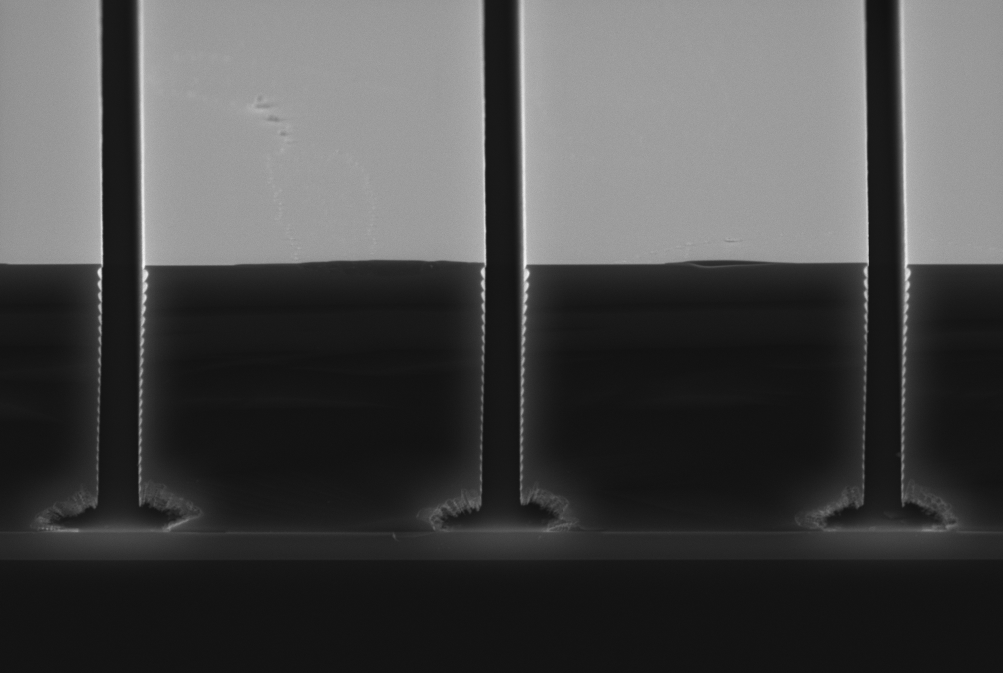

凹槽效应,英文名称notching effect,又可以叫做缺口效应。指的是在多层结构的干法刻蚀过程中,会在某一层的边缘形成不希望出现的凹槽,影响整个芯片的性能。"Notching Effect" 并不是SOI衬底的专属,它是一个广泛存在于多层材料刻蚀过程中的现象。本文以SOI衬度刻蚀为例,来解释这一现象。

SOI衬底的中间有一层氧化硅,上下均为硅单晶。理论上,干法刻蚀过程在遇到氧化硅层时应当自动停止,即氧化硅作为一个刻蚀终止层。但是,实际过程中,在刻蚀到二氧化硅层后,刻蚀并没有完全停止。刻蚀在二氧化硅层的表面继续进行,形成横向的刻蚀,造成了凹槽效应。

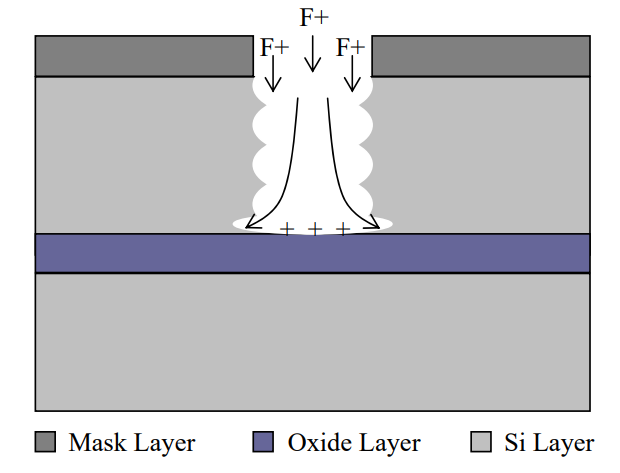

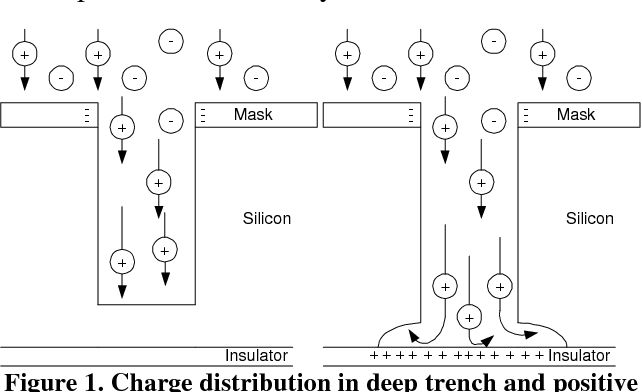

凹槽效应的形成机理

由于氧化硅层本身的绝缘特性,离子电荷会在氧化硅上大量积聚。在氧化硅层表面积累的正电荷形成一个局部电场。这个电场会改变进入材料的离子轨迹,使其沿着硅氧化层的表面横向刻蚀,在多层材料的交界处,由于离子的横向刻蚀,形成一个不期望的缺口。

如何减弱凹槽效应?

上面我们已经了解到凹槽效应主要来源于绝缘层电荷的积累,那么我们抑制凹槽效应的一大思路便是及时导散掉积累的电荷,不让氧化硅表面有过多的电荷聚集。围绕着这个思路,我们可以从以下几个当面入手:

1,设计时做好考虑

在设计阶段就需要考虑到凹槽效应的可能性,预留出相应空间,避免高深宽比的结构,防止负载效应加深凹槽效应,负载效应见前文:

干法刻蚀的负载效应是什么?

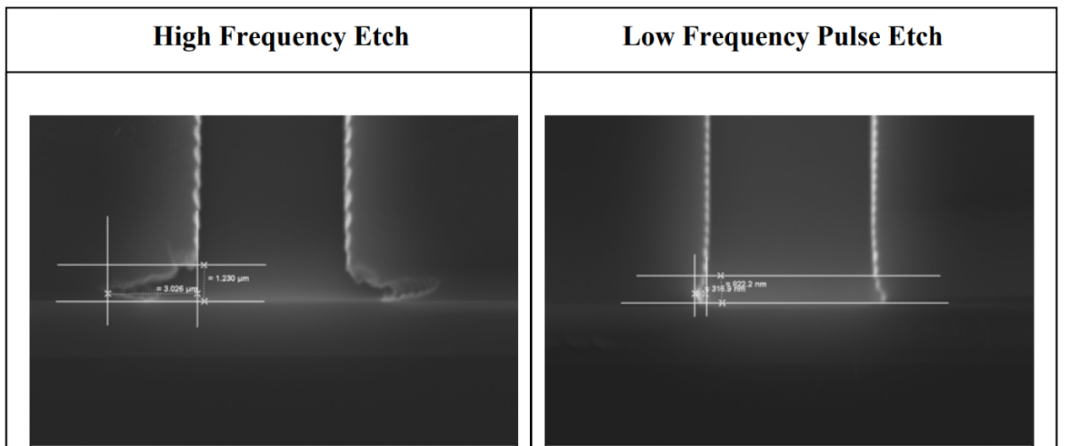

2,优化工艺参数

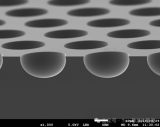

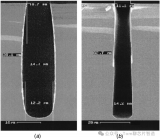

通过改变刻蚀参数(电源频率、刻蚀气体种类和流量等)来找到一个更优化的刻蚀条件,以减轻凹槽效应。例如,在其他条件不变的情况下,采用低频率产生的凹槽效应就远远小于高频率产生的凹槽效应。如下图:

3,分步刻蚀

在刚开始阶段,使用高刻蚀速率的参数来移除大部分材料。当刻蚀接近目标层时,减小刻蚀速率、减小RF功率或增加保护气体的流量,以减小Notching Effect。

分步刻蚀适合优化在单一参数设置下可能出现的问题,有利于解决复杂结构中的刻蚀问题。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50832浏览量

423813 -

SOI

+关注

关注

4文章

70浏览量

17646 -

刻蚀

+关注

关注

2文章

186浏览量

13110

原文标题:【光电集成】什么是干法刻蚀的凹槽效应?

文章出处:【微信号:今日光电,微信公众号:今日光电】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

干法刻蚀常用设备的原理及结构

释放MEMS机械结构的干法刻蚀技术

【转帖】干法刻蚀的优点和过程

释放MEMS机械结构的干法刻蚀技术

两种基本的刻蚀工艺:干法刻蚀和湿法腐蚀

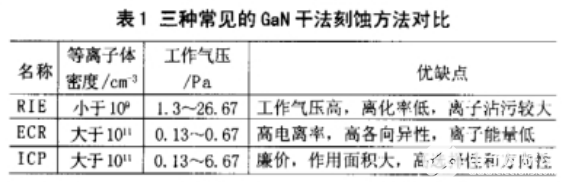

GaN材料干法刻蚀工艺在器件工艺中有着广泛的应用

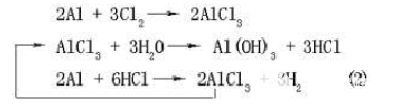

干法刻蚀之铝刻蚀的介绍,它的原理是怎样的

干法刻蚀工艺介绍

干法刻蚀和清洗(Dry Etch and Cleaning)

干法刻蚀工艺的不同参数

晶圆表面温度对干法刻蚀的影响

干法刻蚀侧壁弯曲的原因及解决方法

什么是干法刻蚀的凹槽效应?凹槽效应的形成机理和抑制方法

什么是干法刻蚀的凹槽效应?凹槽效应的形成机理和抑制方法

评论