本文要点:

掌握信号完整性基础知识

实现良好信号完整性的 PCB layout 技术

有助于提高信号完整性的 layout 工具和功能

诚信 (integrity) 的本质特征之一是始终如一、不妥协、值得信赖。在现代电子设备和系统中,高速电信号的质量也得讲究“诚信”,不过其定义是 integrity 的另一涵义——完整性。如果信号质量下降或信号完整性表现不佳,就可能无法达到预期目的。这会导致设计的电子产品出现各种问题,如间歇性故障,甚至彻底无法运行。

为避免此类中断和故障,需要根据特定的设计标准对 PCB 进行布局和布线,创建最有利于传输高速信号的环境。这涉及 PCB 设计的方方面面,包括所使用的元件、原始电路板的制造以及元件的摆放和连接方式。要成功设计高速电子产品,设计人员必须了解信号完整性的基础知识。

1

信号完整性不佳可能导致的问题

干扰可能对电子设备运行产生巨大影响。比如说,坐飞机时手机需要关机、收音机受到干扰会传出静电噪声;一些老式电脑会产生大量的电磁干扰,最终只能退出市场。信号完整性不佳导致的大多数问题更加隐蔽——性能可能偶尔出现故障,数据可能丢失,甚至设备都可能无法运行。这些问题的根源通常都可以追溯到信号完整性问题。

电子设备中的信号速度越来越快,更容易受到各种干扰,包括阻抗失配导致的信号反射、地弹和串扰。如果不专门针对这些问题去设计电路板的布局,信号恶化会愈演愈烈,直至电路板无法按预期正常工作。此外,电路板的设计还必须确保不会给自身电路或附近的电子设备带来信号完整性问题。在针对这些问题下手设计之前,首先要了解一些关键的信号完整性基本知识。

恰当的约束规则设置有助于高速设计的成功

*本视频可能录制于产品用户界面更新之前,也可能基于更早版本录制;视频中的概念和工作流程仍适用于产品当前最新版本。

2

必备的信号完整性基本知识

导致电路板上的信号质量下降有多种类别的影响因素。以下四种值得关注。

01

电磁干扰(EMI)

如果在电路板上布设高频信号时未加谨慎,就会产生 EMI 辐射。不仅走线的长度和配置会造成问题,走线和过孔残桩也会起到天线的作用。EMI 的另一个来源是信号返回路径,该路径最好位于相邻的参考平面上。如果返回路径受阻,信号在寻找返回信号源的路径时就会辐射出更多的噪声。

02

串扰(Crosstalk)

相距太近的高速走线可能会意外耦合,导致一个信号压倒另一个信号。这种串扰会导致受害者信号模仿攻击者信号的特性,无法完成其预期的作用。不仅并排布线会产生串扰,在电路板相邻的层上并行布线也会产生串扰。这种串扰被称为“宽边耦合”,这也是大多数电路板设计在相邻层上交替进行水平和垂直布线的原因。

03

同步开关噪声(地弹)

电路板上有众多元件在高电平和低电平状态之间切换,切换到低电平状态时,电压电平可能无法完全恢复到接地电位。如果低电平状态的电压电平反弹过高,信号的低电平状态可能会被误认为是高电平状态。这种情况大量且同时地发生的话,可能会导致错误切换或双重切换,干扰电路的运行。

04

阻抗失配

敏感的高速传输线路的均匀性发生变化会导致信号反射,从而破坏信号的完整性。在没有妥善关注阻抗值的情况下布线,不同电路板区域的阻抗值会根据各种条件发生变化。要正确布设受控阻抗的敏感走线,需要合理设计层叠、走线宽度和间隙。

明确了信号完整性的主要问题后,可以通过哪些 PCB 设计方法来解决呢?

3

增强信号完整性的 PCB 设计方法

1. PCB 层叠设置和器件布局

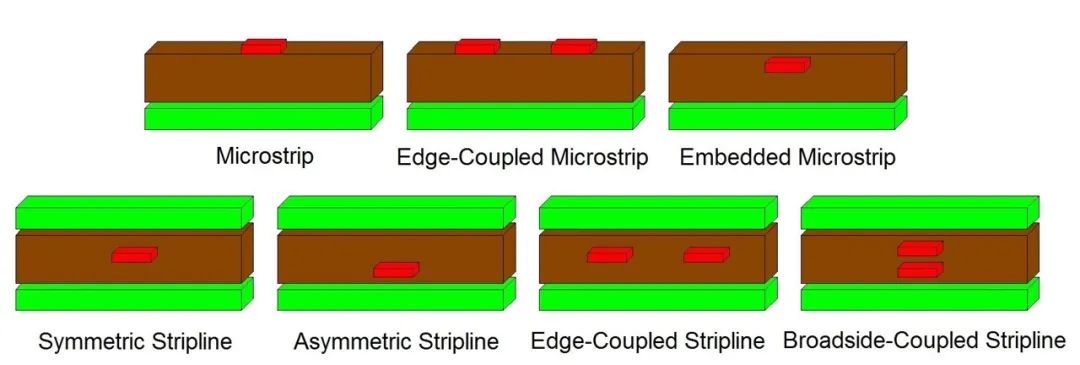

PCB 的信号完整性问题通常是由于信号返回路径不当。返回路径不能有障碍物,而且需要位于相邻的参考平面层上,以获得更好的信号完整性。要实现这种配置,需要在电路板层叠中设置专用的层,用于微带线或带状线配置的敏感高速布线和相邻参考平面。微带线配置由表面走线和下面的单个平面组成,而带状线走线则在内部布线,夹在两个参考平面之间。

微带线和带状线层配置对信号完整性的影响

相邻参考平面和清晰的返回路径对所有信号都有益处,不过对于必须以受控阻抗布线的敏感信号来说,这一点变得更加重要。要确定用于受控阻抗布线的走线宽度,就需要计算介质厚度、介电常数以及走线厚度。若改变电路板层叠或用于 PCB 制造的材料,上述计算结果就会改变,因此设计人员必须在 layout 开始前确定电路板的 layout 配置。除此之外,受控阻抗走线采用哪种微带线或带状线配置进行布线,也会影响计算结果(如上图所示)。

电路板层层叠配置确定后,下一步就是在电路板上摆放器件。许多高速电路由多个网络组成,这些网络从一个器件的驱动引脚开始,穿过其他器件,在最后一个器件的负载引脚处终止。如此形成的回路被称为信号路径。为了保持信号的完整性,必须按照原理图中的详细说明,依次摆放部件,以便引脚之间实现最短的点对点连接。其他器件,如处理器和内存芯片,需要有足够大的间距,以满足所有布线拓扑结构的需要,但距离又要足够近,以实现短连接。

器件摆放注意事项

在摆放高速电路时,应遵循原理图的逻辑流程。

为逃逸布线和总线布线留出空间。

确保运行时会发热的器件能够有效散热。

在电路板上摆放好器件后,下一步就是布线。

2.电路板布线和参考平面

此时就可以开始布线。要保证信号完整性良好,走线与器件的位置密切相关。例如,逃逸布线必须精心设计,确保所有信号妥当连接,以及相关器件(如旁路电容)尽可能靠近引脚。针对引脚数量众多的 BGA,许多设计需要依靠盘中孔 (via-in-pad) 来确保连接简短,并为布线留出更多空间。

妥当完成器件布局后,就可以进行高速电路布线了。

布线准则

信号路径走线要简短、直接。

敏感信号应尽可能布设在内部层上、紧邻参考平面旁边或位于参考平面之间。

时钟线和其他敏感高速信号应尽可能与其他走线分开。间距应为所用走线宽度的三倍,这条经验法则屡试不爽。

差分对布线要紧密相邻,不要在过孔等障碍物周围拆散差分对。

对长度必须匹配的一组网络进行布线时,先从最长的连接开始,然后在其他连接上增加可以调节的绕线,与第一个连接相匹配。

不要让敏感信号穿过电路的嘈杂区域,如电路板的模拟或电源部分。

留出足够的空间,以便在需要时采用菊花链等特定布线拓扑结构。

尽可能减少过孔的使用,避免过孔长度和电感带来更多信号完整性问题。

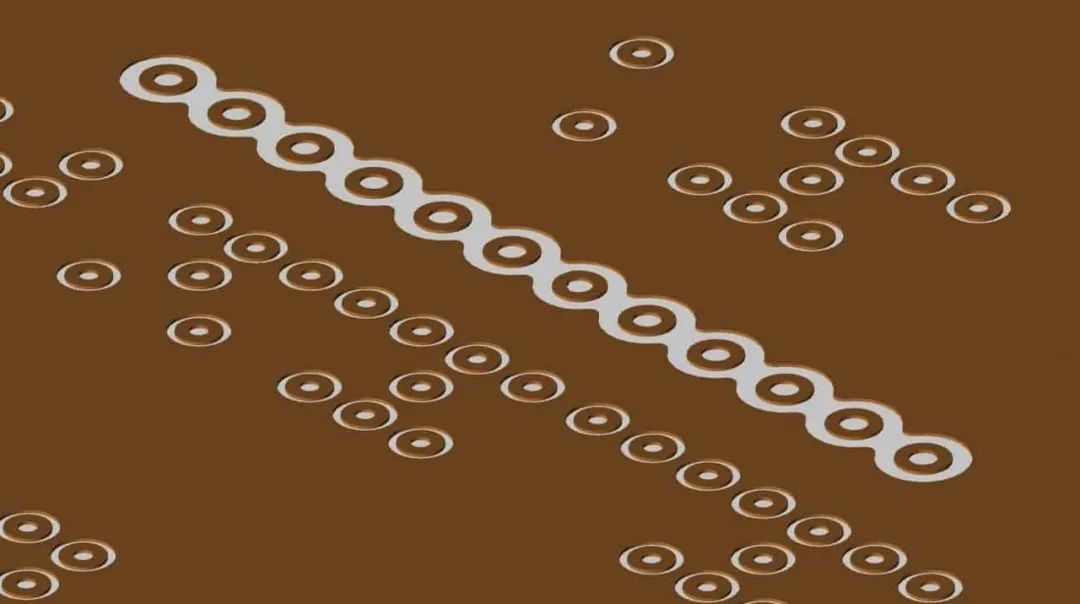

除了布线,还需要设计电路板的电源分配网络 (PDN)。干净的 PDN 对电源完整性至关重要,同时也有助于确保信号完整性。另外,高速传输线应避免穿过参考平面上的阻塞区域,否则电路板会产生更多电磁干扰,因为信号会四处游荡,试图找到返回信号源的清晰路径。阻塞区域包括分割平面、电路板切口和密集的过孔区域,如下图所示:

密集的过孔区域可能会堵塞参考平面上的信号返回路径

设计出有良好信号完整性的电路板虽然复杂,但 CAD 工具可以助力设计人员提高效率,更好完成。

4

有助于确保信号完整性的 layout 工具

当下的 PCB 设计系统包括许多实用的工具和功能,有助于确保设计具有良好的信号完整性。例如,Cadence Allegro PCB 设计软件提供了一个规则系统,用于为器件、网络、高速网络和电气属性(阻抗、传播延迟等)设置规则。此外,Sigrity Aurora 工具提供设计同步分析(In-design Analysis)功能,可将信号完整性、电源和电磁仿真无缝直接集成到 layout 环境中。

目前,Cadence Allegro PCB 设计软件已进化到最新的 Allegro X 23.1 版本!不仅包含以上全部功能,更与 Cadence Clarity 3D Solver、Celsius Thermal Solver 等电磁分析、热仿真分析工具无缝集成,为 PCB 和系统设计的工程师提供集成了逻辑/物理设计、系统分析和设计数据管理的系统设计平台和新的技术升级!

全新的 EE 控制面板,可进行版图规划和输入分析;集成的 X AI 技术,能自动完成元件放置、电源网络分配和布线;升级更新的 Allegro System Capture、Allegro Pulse 数据管理和云连接等主要产品,能确保您获得迄今为止最强大的 Allegro 性能,将整体设计生产力提高 4 倍。

-

pcb

+关注

关注

4338文章

23284浏览量

403284 -

信号

+关注

关注

11文章

2823浏览量

77517 -

Layout

+关注

关注

15文章

409浏览量

62370

发布评论请先 登录

相关推荐

恶劣环境中的PCB信号完整性维护的实践建议

听懂什么是信号完整性

一文速通 PCB layout 中的信号完整性基础知识

一文速通 PCB layout 中的信号完整性基础知识

评论