MOS器件物理基础——基本概念

PART01

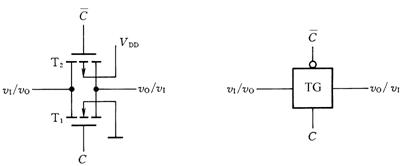

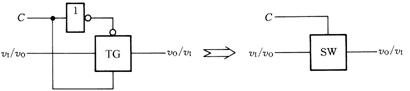

MOSFET 开关

在研究MOSFET的实际工作原理前我们来考虑这种器件的一个简化模型,以便对晶体管有一个感性认识:我们预期它有什么样的特性以及特性的哪些方面是重要的。

图1是一个n型MOSFET的符号,图中表示了三个端口:栅(G)、源(S)和漏(D)。这种器件是对称的,因而源和漏可以互换。作为开关工作时,如果栅电压VG是高电平,晶体管把源和漏连接在一起;如果栅电压为低电平,则源和漏是断开的。

即使对于这样简单的描述,我们还是必须回答几个问题。VG取多大值时器件导通?换句话说,阀值电压是多少?当器件导通(或断开)时,源和漏之间的电阻有多大?这个电阻与端电压的关系是怎样的?总是可以用简单的线性电阻来模拟源和漏之间的通道吗?是什么因素限制了器件的速度?

虽然所有这些问题都是在电路级产生的,但是仅通过分析晶体管的结构和物理特性就可以对其作出回答。

图1

PART02

MOSFET的结构

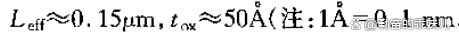

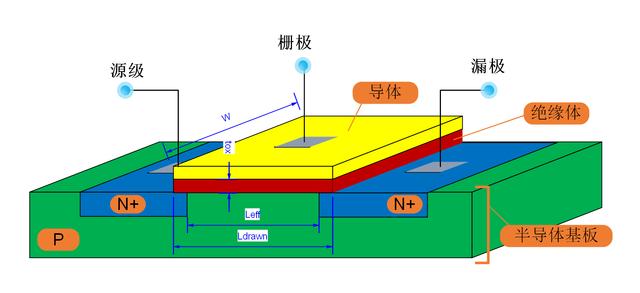

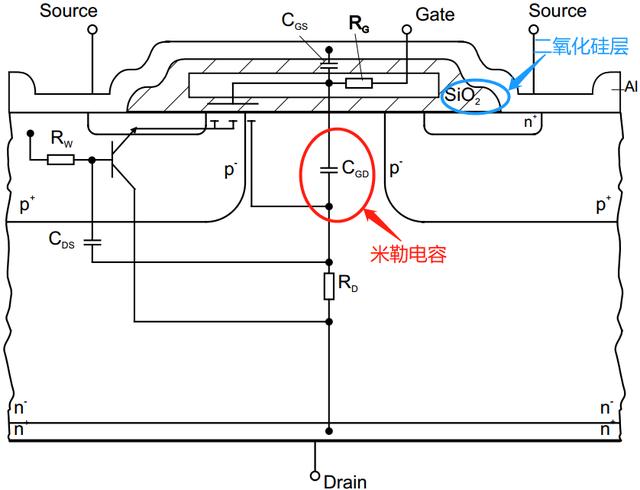

n型MOS(NMOS)器件的简化结构如图2所示。器件制作在p型衬底上(衬底也称作bulk或者body),两个重掺杂n区形成源端和漏端,重掺杂的(导电的)多晶硅区(通常简称poly)作为栅,一层薄SiO2使栅与衬底隔离。器件的有效作用就发生在栅氧下的衬底区。注意,这种结构中的源和漏是对称的。

图2

源漏方向的栅的尺寸叫栅长L,与之垂直方向的栅的尺寸叫做栅宽W。由于在制造过程中,源/漏结的横向扩散,源漏之间实际的距离略小于L。为了避免混淆,我们定义Leff=Ldrawn-2L eff,式中Leff称为有效沟道长度,Ldrawn是沟道总长度,而LD是横向扩散的长度。正如在以后我们将会看到的那样,Leff和氧化层厚度tox对MOS 电路的性能起着非常重要的作用。因此,MOS 技术发展中的主要推动力就是不使器件的其它参数退化而一代一代地减小这两个尺寸。后续文章这两个尺寸的典型值为

。后续文章以后将用 L 来表示有效长度。

。后续文章以后将用 L 来表示有效长度。

既然MOS结构是对称的那么为什么还要将一个n区称为源而另一个n区称为漏呢?如果将源定义为提供载流子(NMOS器件中为电子)的终端而漏定义为收集载流子的终端这一点就很清楚了.因此,当器件三个端子的电压变化时,源和漏的作用可以互换。在本章后面的习题中给出了这些概念的练习。

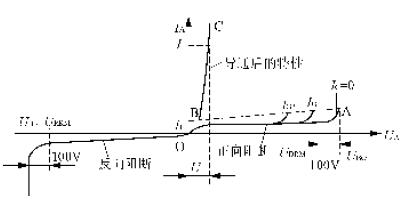

到目前为止,我们还没有考虑器件的衬底。实际上,衬底的电位对器件特性有很大的影响。也就是说,MOSFET 是一个四端器件。由于在典型的 MOS 工作中,源/漏结二极管都必须反偏,所以我们认为 NMOS 晶体管的衬底被连接到系统的最低电压上。例如,如果一个电路在03V工作,则 Vsub.NMOS =0。实际的连接如图3 所示通常通过一个p+欧姆区来实现。

图3

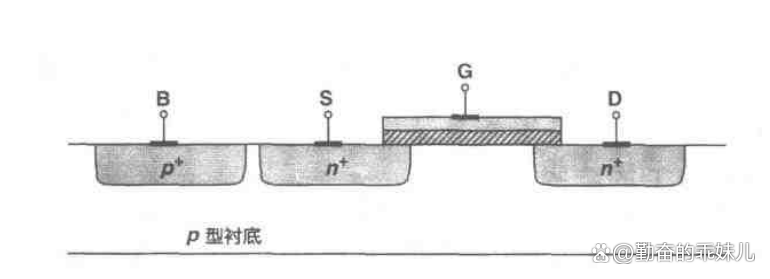

在互补MOS(CMOS)技术中同时用到NMOS和PMOS。从简单的角度来看,PMOS器件可通过将所有掺杂类型取反(包括村底)来实现,如图4(a)所示。但实际生产中NMOS和PMOS器件必须做在同一晶片上,也就是说做在相同的村底上。由于这一原因,其中某一种类型的器件要做在一个“局部衬底”上,通常称为“阱”。现在大多数 CMOS工艺中PMOS器件做在n阱中(图4b))。注意n阱必须接一定的电位,以便 PMOS管的源/漏结二极管在任何情况下都保持反偏。在大多数电路中,n阱与最正的电源供给相连接。为了简化,有时分别称NMOS和PMOS器件为“NFETs”和“PFETs”。

图4(b)指出了NMOS和PMOS 晶体管一个有意义的区别每个PFETs可以处于各自独立的n阱中而所有 NFETs则共享同一衬底。PFETs的这种灵活性在一些模拟电路中被应用。

图4

PART03

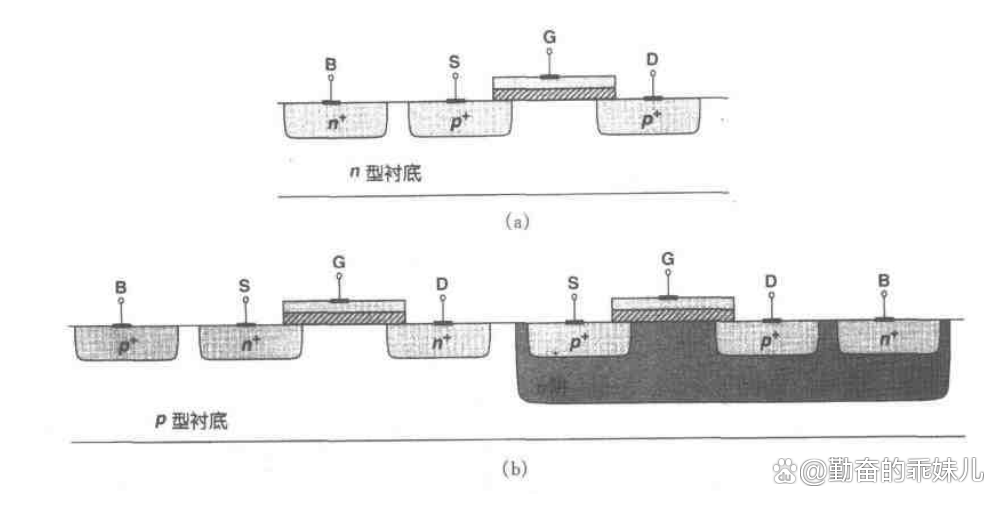

MOS符号

用来表示NMOS和PMOS 晶体管的电路符号如图5所示。图5(a)中的符号包括晶体管的所有四个端子,其中衬底用 B(bulk)而不是用S来表示,以免与源极相混淆。PMOS 器件的源极放在顶端,这是为了直观起见,因为源极比栅极的电压高。由于在大多数电路中,NMOS和PMOS器件的村底端子分别接地和 VDD ,所以我们画图时通常省略这一连接图5(b)在数字电路中惯上用图 5(C)所示的开关符号来表示两种 MOS管。但是我们更喜欢图5(b)的表示,因为明确区分源和漏对于理解电路的工作被证明是很有帮助的。

图5

-

MOSFET

+关注

关注

147文章

7156浏览量

213142 -

NMOS

+关注

关注

3文章

294浏览量

34348 -

晶体管

+关注

关注

77文章

9682浏览量

138080 -

PMOS

+关注

关注

4文章

245浏览量

29555 -

MOS器件

+关注

关注

0文章

9浏览量

6436

发布评论请先 登录

相关推荐

MOSFET的结构、电学符号和电学特性

MOSFET的基本结构与工作原理

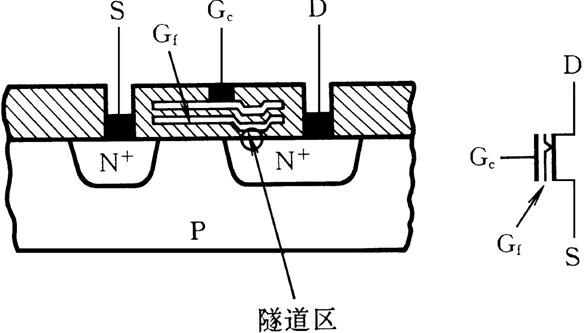

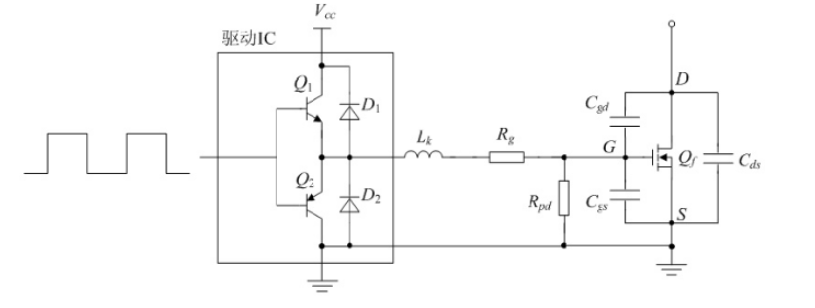

基于MOSFET内部结构设计优化的驱动电路

单向晶闸管的结构、符号

基于图元结构的电气早图符号识别

MOSFET结构和符号及教程摘要

MOSFET的结构和电路符号

MOSFET的结构和电路符号

评论