MOS器件物理基础——MOS的I/V特性

分析MOSFETs 中电荷的产生和传输建立它们与各端电压之间的函数关系。推导出I/V特性方程。这样就能够将抽象级别从器件物理级提升到电路级。

PART01

阀值电压

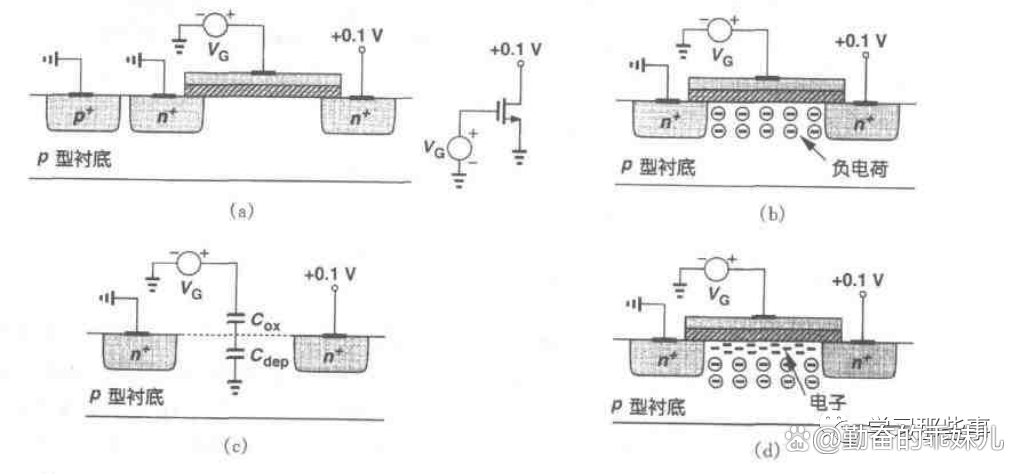

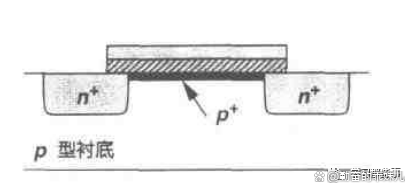

考虑如图1(a)所示的NFET。当栅压VG从0V上升时会发生什么情况?由于栅和衬底形成一个电容器,所以当 VG逐渐升高时,p衬底中的空穴被赶离栅区而留下负离子以镜像栅上的电荷。换句话说,就是形成了一个耗尽层图1(b)。在这种情况下由于没有载流子而无电流流动。

图1(a)由栅压控制的MOSFET;(b)耗尽区的形成;

(c)反型的开始 (d)反型层的形成

随着VG的增加,耗尽层宽度和氧化物与硅界而处的电势也增加。从某种意义上讲,这样的结构类似两个电容的串联:栅氧化层电容和耗尽区电容(图1(c))。当界面电势达到足够高时,电子便从源流向界而并最终流到漏端。这时,源和漏之间的栅氧下就形成了载流子“沟道”,同时晶体管“导通”。我们也称之为界面“反型”。形成沟道所对应的VG称为“阀值电压”,VTH。如果 Vc进一步升高,则耗尽区的电荷保持相对定恒定,而沟道电荷密度继续增加,导致源漏电流增加。

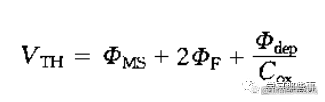

实际上,导通现象是栅电压的增函数,这就使得明确地定义VTH变得比较困难。在半导本物理学中,NFET的VTH通常定义为界而的电子浓度等于p型衬底的多子浓度时的栅压可以证明:

式中 是多晶硅栅和硅衬底的功函数之差,

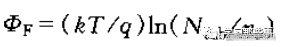

是多晶硅栅和硅衬底的功函数之差, ,q是电子电荷,Nsub是衬底的掺杂浓度,Qdep是耗尽区的电荷,Cox是单位面积的栅氧化层电容.由pn结理论可知,

,q是电子电荷,Nsub是衬底的掺杂浓度,Qdep是耗尽区的电荷,Cox是单位面积的栅氧化层电容.由pn结理论可知, ,其中表示硅的介电常数。由于Cox在器件和电路计算中经常出现,所以记住它的值是有帮助的:这样,对于其它的氧化层厚度,Cox的值可以依比例确定。

,其中表示硅的介电常数。由于Cox在器件和电路计算中经常出现,所以记住它的值是有帮助的:这样,对于其它的氧化层厚度,Cox的值可以依比例确定。

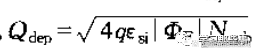

在实际中,由上式得到的“本征”阙值电压可能不适用于电路设计,举例来说VTH=0因而VG≥0时器件不会大断。因此,在器件制造过程中通常通过向沟道区注入杂质来调整阙值电压,其实质是改变氧化层界面附近衬底的掺杂浓度。例如,如图2所示如果形成了p+薄层,那么就需要增加栅压使此区域耗尽。

图2 用来改变阀值电压的 p +掺杂剂的注人

以上的定义不能直接适用于 VTH的测量。在图1(a)中,只有漏极电流可以表示器件的通或断,因此不能揭示 VGS为何值时界面的电子浓度等于p型衬底的多子浓度。结果,给借助 I/V 测量来计算VTH带来一些不确定性。后面的部分会讲到这一点,不过在基础分析中假定当 V GS ≥VTH时器件会突然导通。

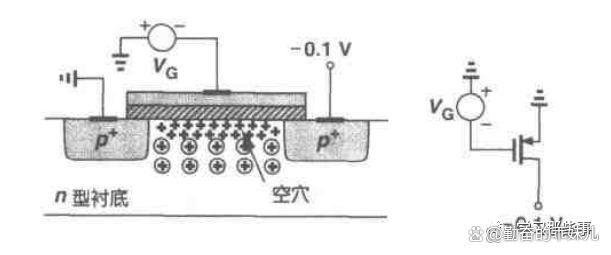

PMOS器件的导通现象类似于NFETs,但是其所有的极性都是相反的。如图3 中所示,如果栅-源电压足够“负”在氧化层-硅界面就会形成一个由空穴组成的反型层,从而为源和漏之间提供了一个导电通道。

图3 PPET反型层的形成

-

电容器

+关注

关注

63文章

6199浏览量

99306 -

MOSFET

+关注

关注

144文章

7085浏览量

212707 -

MOS

+关注

关注

32文章

1246浏览量

93472 -

电荷

+关注

关注

1文章

612浏览量

36105 -

MOS器件

+关注

关注

0文章

9浏览量

6427

发布评论请先 登录

相关推荐

MOS管的种类、结构及导通特性详解

详解MOS管驱动电路

详解MOS管驱动电路

挖掘MOS管电路应用的特性

偏微分方程式数值解之计算机Fortran算法详解附图(续i)

MOS管的特性是什么

利用Van der Pol方程分析MOS LC差分振荡器

含受控源电路例题网孔分析详解(方程和矩阵)

详解MOS的I/V特性方程

详解MOS的I/V特性方程

评论