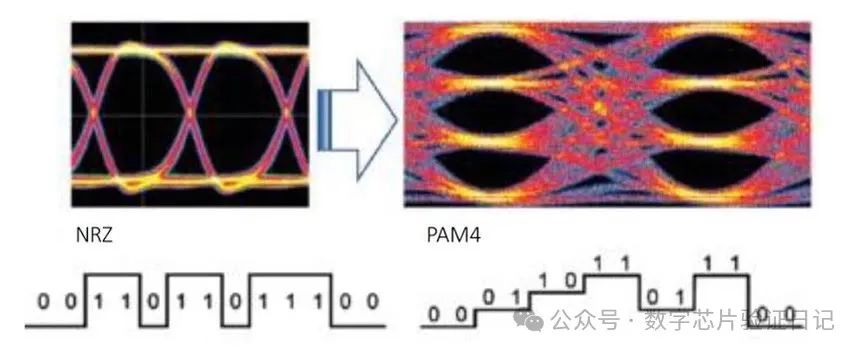

怎么解释1nf的电容链路整体波形或眼图的幅度拉下来的现象呢,除了电容选对外,还有什么方法来改善这种长“0”长“1”码型对高速信号的影响呢?

在电子系统中,高速信号的传输对于系统的性能和可靠性是至关重要的。传输过程中,信号穿过复杂的电路,也可能面临各种干扰,而其中一个重要的因素是电容链路的影响。在电容链路中,通常会出现整体波形或眼图的幅度拉下来的现象。这个现象会对高速信号的传输质量造成不良的影响。在本文中,我们将讨论这个问题,并尝试寻找如何改善这种长“0”长“1”码型对高速信号的影响的方法。

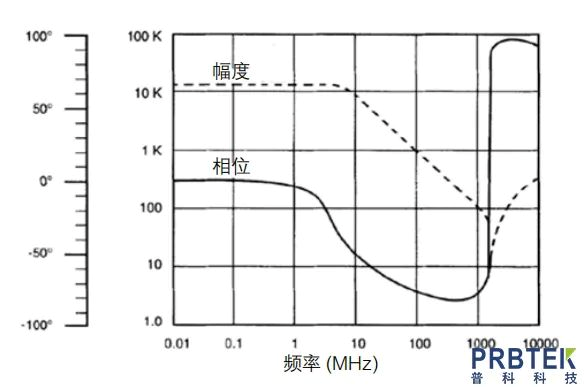

首先,我们需要理解电容链路对高速信号的影响。在电容链路中,由于电容的存在,高频信号会在电容中产生反射。这会导致信号的幅度被削弱,并会影响整个信号的形状。特别地,长时间处于高电平(或低电平)的信号会更容易受到影响。这是因为在信号处于高电平(或低电平)期间,电容充电(或放电)的速率变化最大,从而产生最强烈的反射。

那么,如何解决这个问题呢?首先,我们需要确保电容链路的电容选择正确。电容的大小越小,其对信号的影响就越小。因此,选择尽可能小的电容可以有效地减少信号的反射,从而改善信号的传输质量。另外,我们可以采用双电容隔离方法。即在电容链路两端各加一个电容,从而将信号隔离开来,减少对信号的反射。这种方法可以有效地降低信号的干扰,提高信号传输的可靠性。

除了电容选择和双电容隔离方法,还有其他一些方法可以改善长“0”长“1”码型对高速信号的影响。例如,我们可以采用预加重技术。预加重技术是在信号传输之前对信号进行加重处理,使其在传输过程中受到的衰减更小。这可以提高信号的幅度,并改善信号的传输质量。另外,我们还可以采用差分信号传输方法。差分信号传输是在信号传输过程中使用一对反向的信号,从而使信号在穿过电容链路时更加稳定。这种方法可以有效地降低信号的噪声和干扰,从而提高信号传输的可靠性。

综上所述,电容链路是高速信号传输中常遇到的一个问题。其会导致信号的幅度被削弱,并影响整个信号的形状。因此,选择合适的电容、采用双电容隔离、预加重技术和差分信号传输方法可以有效地改善这种情况。这些方法可以帮助提高信号传输的可靠性和稳定性,并最终提高电子系统的性能。

-

电容充电

+关注

关注

0文章

68浏览量

8588 -

高速信号

+关注

关注

1文章

225浏览量

17694

发布评论请先 登录

相关推荐

ADS8365在测试时发现将输入端短接,频谱波形异常的原因?如何解决?

TLV320AIC3104-Q1为了避免ESD事件引起复位需要加一个1nf的电容,这个1nF的电容是1KV的吗还是普通的陶瓷电容?

TPA3111D1的OUTP引脚下管MOS烧毁短路的原因?怎么处理?

TDK贴片电容的标识方法中,101丶102、103、104、105、106丶107分别对应的容量是多少呢

OPA2348用作电压放大,输出端直接接1nF电容,请问是否有什么风险吗?

贴片电容104电容量是多少?怎么进行计算?

加上拉电阻后的整体波形为什么可以向上移动呢?

高速信号眼图测试的基本原理

示波器眼图是啥?怎样形成示波器眼图又如何分辨信号质量?

电容负荷对波形中高频成分的幅度和相位的影响

怎么解释1nf的电容链路整体波形或眼图的幅度拉下来的现象呢?

怎么解释1nf的电容链路整体波形或眼图的幅度拉下来的现象呢?

评论