RISC-V 不再满足于颠覆 CPU 行业。它正在对集成到 SoC 或高级封装中的每种类型的处理器发动战争,这是一项雄心勃勃的计划,将面临来自拥有雄厚研发业务和构建良好生态系统的老牌厂商的激烈竞争。

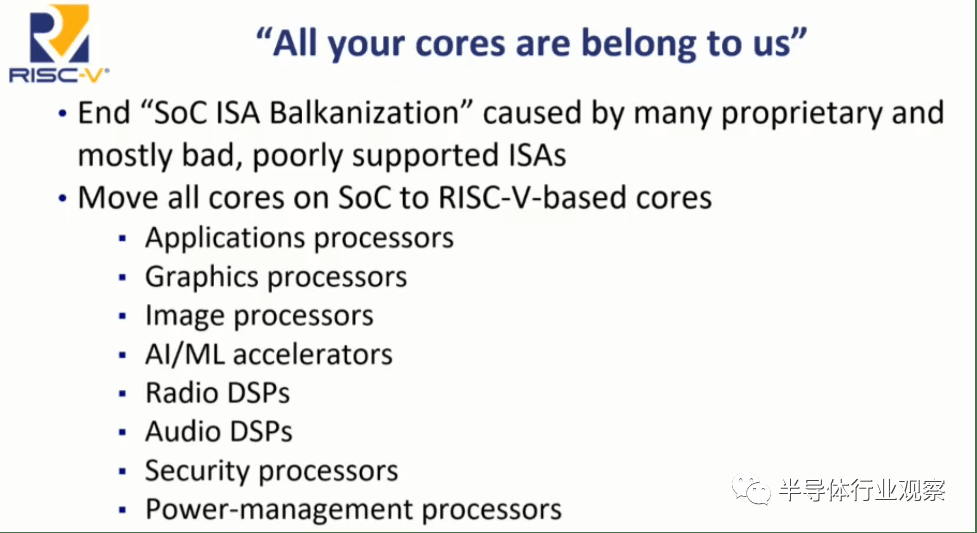

当 RISC-V International 首席执行官 Calista Redmond 在去年的峰会上表示 RISC-V 将无处不在时,大多数人可能认为她在谈论 CPU。很明显,该组织打算在服务器和深度嵌入式设备中使用 RISC-V 内核。但该组织的目标远不止于此。Redmond暗示,每个处理核心、GPU、GPGPU、AI 处理器以及尚未构思的所有其他类型的处理器都将基于 RISC-V。加州大学伯克利分校教授兼 RISC-V 国际主席 Krste Asanović 在他的国情咨文中展示了下面的幻灯片,这一点变得更加清晰。

如今,随着最近完成的安全和加密工作,这一愿景开始成形。正在组建小组并审查捐款,以增加对矩阵乘法的支持,矩阵乘法是 GPU 和 AI 处理器的基本功能。

这些大胆声明的背后是数据和计算架构的根本性转变。这不再是哪家公司拥有最快的CPU的问题,因为无论设计得多么好,所有的CPU都有局限性。“在一些垂直市场,例如 5/6G、推理和视频处理,它们的计算工作负载不再适合在传统 CPU 上处理,”西门子 EDA 的 Catapult HLS 团队项目总监 Russell Klein表示。“这就是我们看到新计算方法被采用的地方。”

几乎每个应用程序都有某种形式的控制结构。“从内存访问的角度来看,图形是一种非常特殊的野兽,具有非常特殊的要求,”Arteris 解决方案和业务开发副总裁 Frank Schirrmeister说道。“如果你看一下最近发布的一些 AI 和 RISC-V 公告,你会发现有些公司宣布的处理元素显然包含 ISA。”

在某些情况下,这些只需要正确的说明。Bluespec 首席执行官 Charlie Hauck 表示:“RISC-V 有一种叫做向量扩展的东西。” “根据您如何实现这一点,您可以获得一些看起来非常像 GPU 的东西,其中有许多并行运行的小型单元,或者以 SIMD 类型的方式运行。”

然而,这条路并不容易。“通过指令扩展将GPU功能添加到RISC-V架构中很有吸引力,因为GPU在AI领域发挥着重要作用,”Stream Computing研发总监Fujie Fan表示。“然而,我们已经意识到架构和生态系统中不可避免的问题。”

怀疑论者比比皆是。处理器的历史上充斥着失败的初创公司,它们宣称他们将用新的计算架构粉碎竞争。许多人没有考虑到竞争并没有停滞不前,计算领域正在经历持续且加速的变化,而转向新方法和工具以及培训/再培训工程师的痛苦和费用绝非微不足道。

“RISC-V 为采用者带来的价值在于控制处理领域,它拥有现成的开源工具、现成的操作系统(Linux 或实时)以及提供的长期软件兼容性/可移植性的承诺通过 ISA 通用性,” Quadric工程副总裁 Dhanendra Jani 说道。“图形处理是一个非常不同的挑战——特定领域的处理挑战。要将基本 RISC-V 指令集调整为一种非常适合 GPU 任务的指令集,需要大量投资来定义自定义 ISA 扩展、构建高度复杂的微架构更改,并对开源工具进行重大手术,使它们与原来不同。这样做时,使用 RISC-V 的几乎所有固有价值都因广泛的定制而消失了,您将失去大部分优势,同时可能会受到核心 ISA 功能的束缚,这些功能限制了特定领域 GPU 环境中的有用性。简而言之,从 RISC-V 开始而不是从头开始有什么意义呢?”

那么RISC-V的计划是什么?“矢量是 SIMD 操作,使您能够同时对多条数据进行操作,并让芯片找出从内存中取出数据的最佳方式,处理单个指令,然后将数据放回内存,或者将它们转移到下一个操作,”RISC-V International 首席技术官 Mark Himelstein 说道。“缺少的基本内容是矩阵乘法。我们收到了多个提案,其中之一类似于适合 32 位指令的向量扩展。这非常困难并且需要设置说明。您设置了stride和masks等内容,然后扣动扳机并执行操作。但如果您想与其他架构上更大的矩阵实现竞争,则必须采用更宽的 64 位指令。这是很多人都在谈论的话题。”

问题是有多少复杂性被暴露,有多少仍然隐藏。“ISA 是一个关键组件,” Arm客户端业务线产品管理高级总监 Anand Patel 说道。“然而,GPU 的复杂性通常由 Vulkan 或 OpenCL 等标准 API 抽象出来。这使得开发人员可以更轻松地跨多个供应商进行定位,同时将较低级别的优化留给 GPU 供应商。即使在 GPGPU 类型的应用中,GPU 的架构也在快速发展,以跟上人工智能处理等新兴用例的步伐,因此开发人员能够访问成熟的软件生态系统来跟上这些变化至关重要。标准 API 确保开发人员不必担心 ISA 更改,而是透明地看到这些底层改进的好处。”

宏观架构和微架构

区分这两个问题很重要,因为 RISC-V 仅定义了宏观架构,而将所有微架构决策留给了实现者。当超越 CPU 时,这将成为一个更大的问题。“冯·诺依曼在某些方面有限制性,但特定实现如何与内存交互并不是由 RISC-V 决定的,”RISC-V 的 Himelstein 说。“大多数 GPU 实现都通过多级管道中的内存来优化这一点。当一些操作正在进行时,一些东西来自内存。当您开始研究 GPU 时,您会谈论暴露内存交互。我们确实对事情发生的顺序有一些限制,因为你想确保操作被明确定义。”

看待问题的方法有很多种。“最先进的 GPU 产品可以按照传统图形处理和现代人工智能加速来划分,”Stream 的 Fan 说道。“前者更像是可编程ASIC,而不是通用处理器,其核心能力来自于流处理器的实现,而不是ISA。指令集通常对程序员来说是不可见的,并且总是处于次要位置。图形处理器的设计与微架构密切相关,适合用定制指令来实现。对于我们大多数人来说,人工智能和多媒体功能的标准化更具吸引力。要实现这样的能力,复制GPU并不是唯一的方法。对于RISC-V来说,多媒体功能可以通过矢量架构来实现,AI能力可以通过更高效的异构架构和矩阵加速器来实现。”

如果您希望外部程序员为您的设备编写软件,则某些方面会发生变化。“数据流处理可以通过多种方式完成,”西门子的Klein说。“一种是使用小型通用处理器甚至专用处理器的管道,每个处理器都处理问题的一个阶段。这比单个大型 CPU 更快、更高效。使用可编程处理器作为计算元件保留了很大的灵活性,但确实放弃了一些性能和效率。这种方法确实可以在任何有能力的多核处理器上构建。问题是这种方法已被软件开发社区彻底拒绝,他们不愿意放弃单线程编程模型。”

这对于很多企业来说都是一个大问题。“如果您正在寻找通用处理器,根据应用要求,它可以是从单级、两级或三级微控制器一直到运行多级的多级超标量设计。Bluespec 的 Hauck 说道。“或者,你会看到人们拥有 4096 个 RISC-V 处理器,每个处理器都是小型、简化的 RV32I 类型的东西,它们被组合在特定的系统架构和互连中,使这些东西能够按照 GPU 的精神运行。它们由许多较小的整数单元组成,这些单元共同协作完成一项艰巨的任务。挑战在于如何为此开发软件?”

有了更大的灵活性,可能需要新的方法。“在大型 HPC 中,如果您运行的工作负载更加面向数据中心,则它具有一组特定的特征。但如果您的应用程序是科学应用程序,也许有一些关于加载和存储以及多种数学类型运算的功能可以扩展,”西门子 EDA 首席产品营销经理 Andy Meyer 说道。“如果人们选择这条路线,生态系统就会面临一些挑战。最大的增长领域是超大规模应用。如果你看看风险投资的金额,你就会发现他们显然正在解决一个独特的问题。”

软件和生态系统

硬件/软件协同设计一直是几十年来的目标,而 RISC-V 是少数几个取得进展的领域之一。“传统的数据处理设计不遗余力地将硬件和软件分开,”Klein说。“硬件被创建出来,然后软件人员就可以在上面自由发挥。假设是,如果硬件足够通用,那么软件将能够完成提供系统功能所需的任何操作。如果您的计算能力和功耗有足够的余量,那么这是可行的。我不会说它效果很好,但它确实有效,尽管相当浪费。”

特定领域的计算开始改变这一点。“要真正发挥数据流处理器的潜力就意味着针对特定应用程序进行定制,”Klein 补充道。“这意味着硬件和软件团队需要共同努力才能取得成功。这让很多组织和设计团队感到非常不舒服。”

有时协同设计是唯一的方法。“假设您需要在边缘进行一些处理,”Bluespec 的 Hauck 说。“总会存在外形尺寸、尺寸或功率限制。再多的软件创新也无济于事。如果您有一个软件堆栈,那么该堆栈就是它的本质。您将无法对任何具有这些类型的约束的特定解决方案进行软件优化。你必须进入硬件领域。”

创建嵌入式系统时,处理器接触到广泛编程受众的可能性较小,并且可以进行更多优化。“考虑一下已经完成的矢量加密工作,”Himelstein说。“没有人会在他们的程序中编写矢量加密。这不是他们所做的。他们所做的是使用库,例如 libSSL 或其他一些加密库,并且使用这些指令。有时他们通过汇编语言来使用它们,然后提供 C、C++ 或 Java 接口,以便程序、应用程序可以利用它们。”

当需要通用编程时,它就会变得更加困难。“如果你看看 GPU 的生态系统,就会发现工具链是由 NVIDIA 控制的,”Fan 说。“包括AMD在内的其他竞争对手曾试图打破垄断,但失败了。通过扩展RISC-V的标准指令集来兼容不断更新的NVIDIA生态系统几乎是不可能的。另一方面,重新开始也很难,因为 NVIDIA 具有先发优势。”

成功的时刻

尽管如此,RISC-V 的核心在于实现创新。“我们所看到的关于为什么遗留解决方案是目前最佳解决方案的许多观点都是历史性的,”Hauck 说。“智能架构师和智能软件开发人员真正发挥其专业知识的地方将是 RISC-V 类型的环境。”

它始于公共需求。“如果有需要,人们就会聚集在一起进行协作,而 RISC-V 就是协作,”西门子的 Meyer 说道。“你会看到一个又一个的例子,世界各地正在发生各种不同的倡议和联盟。生态系统将会发展,但商业方面和支持社区之间需要保持平衡。”

这可能会带来一些业务挑战,尤其是在收回投资回报时。“RISC-V 还需要一段时间才能赶上并与成熟的产品和生态系统竞争,”Hauck 说。“但你会开始发现,对于某些应用程序,只要有合适的公司支持,RISC-V 处理器就没有理由不能成功。那里有很多优秀的软件开发人员。最终他们会到达那里,因为社区拥有他们创新所需的所有工具。”

那么我们还要多久才能看到 RISC-V GPU 和 AI 处理器呢?Himelstein 表示:“如果您想要为非 GPU 类型的世界提供合理的 AI 功能补充,那么今天您已经拥有了。” “但是,经过批准的矩阵以及这些团体一直要求的所有其他内容的完整补充可能会在大约一年半的时间内出现,其中基本内容可能会出现,然后高级内容可能会在三到四年内出现”。

增量方法可以使部件的使用速度更快。Fan 表示:“分别标准化每个 GPU 功能比标准化整个 GPU 产品要好得多。” “至于人工智能功能,我们认为正在进行的 RISC-V 矩阵扩展对于 IC 设计人员来说是更好的选择。”

审核编辑:刘清

-

处理器

+关注

关注

68文章

19316浏览量

230075 -

SoC芯片

+关注

关注

1文章

612浏览量

34934 -

人工智能

+关注

关注

1791文章

47354浏览量

238792 -

RISC-V

+关注

关注

45文章

2292浏览量

46210 -

GPU芯片

+关注

关注

1文章

303浏览量

5833

原文标题:RISC-V,要颠覆GPU?

文章出处:【微信号:算力基建,微信公众号:算力基建】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ISA ARM 对比 RISC-V

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

risc-v的发展历史

rIsc-v的缺的是什么?

【RISC-V信息速递】反X86和ARM垄断?很多人低估了RISC-V的颠覆性

RISC-V有哪些优点和缺点

RISC-V有哪些优缺点?是坚持ARM方向还是投入risc-V的怀抱?

解锁RISC-V技术力量丨曹英杰:RISC-V与大模型探索

什么是RISC-V?RISC-V的关键技术

Imagination:RISC-V CPU的重要力量

RISC-V要颠覆GPU吗?

RISC-V要颠覆GPU吗?

评论