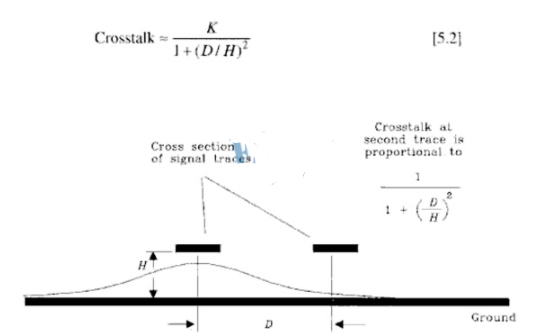

讲到串扰,基础的串扰知识比如串扰是由电场耦合和磁场耦合的共同结果啊,从串扰影响的方向来分有FEXT和NEXT这些小P就都不说了。当小P在学习一篇PCIe 5.0连接器一致性的paper里出现了ICN的字样。

那么ICN到底是什么,度娘搜到的解释是Integrated Crosstalk Noise,集成串扰噪声,但度娘也就到此为止了,没有其他更进一步的解释了,很无语。于是又找了很多的paper,发现ICN的来源应该是IEEE 802.3。

小P找来了IEEE 802.3的协议学习,关于ICN的描述在802.3 section6里。在40GBASE-CR4和100GBASE-CR10标准下对ICN进行了定义。

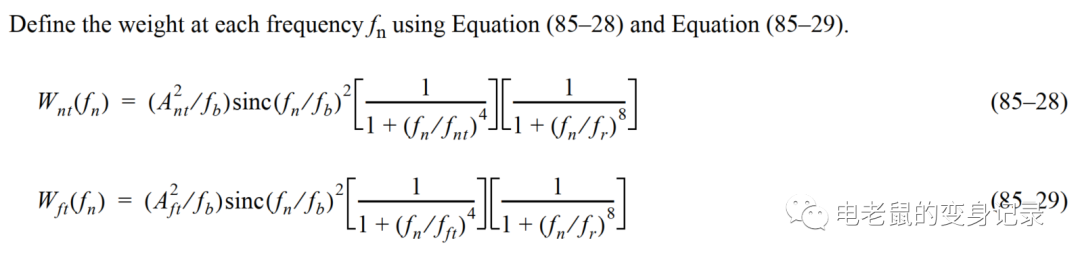

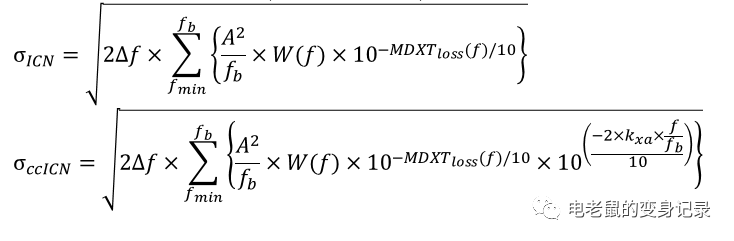

ICN是结合了测试插损,用于约束多个串扰源对单一接收器的干扰的时域要求。串扰噪声的有效值(RMS)是通过一个接收滤波函数(85-28和85-29)的输出和多通道的串扰传递函数(85-30和85-31)进行表征。

最终单个接收器的ICN要求是FEXT和NEXT的能量求和,见公式(85-32)。

(85-28和85-29)两个公式,其实就是近端串扰(NEXT)和远端串扰(FEXT)的能量频谱分布公式(Power Weighting Function, PWF),小P参考其他paper,把A^2/fb从W(f)中摘了出去。这个是个固定的常数,不影响公式曲线的分布,如下图所示,频率越高能量占比越小。

以上参数都是可以从前面的规范表格中获取。

然后小P再对(85-30和85-31)两个公式进行解读。这两个公式其实就是一个公式,只是一个表征的是远端串扰一个是近端串扰。其中公式中的MDNEXT_loss和MDFEXT_loss如下两个公式所得。MD就是multiple disturber的缩写,翻译过来就是多通道近端串扰损耗和多通道远端串扰损耗。

以上就是802.3中关于串扰和ICN的描述,往下则是小P自己的理解记录了。

针对CR4和CR10,其实分别就是4lane和10lane,每lane上传输的信号速率为10Gbps。CR4的NEXT的干扰通道数是4,FEXT的干扰通道数是3(自身作为victim)。而CR10的NEXT通道是10,FEXT通道是9。当然数学公式都是一样的,仅是参数的区别,所以我们只选择汇总成以下两个公式进行解读。

MDXT_loss其实等同于我们平时说的PSXT,也就是多通道串扰的平方和,其中的NLi(f)就是每个通道对victim串扰的频域s参数在对应频点f的值。小P把公式推导了一下(这突然就有在学校上课老师给讲公式推导的感觉了)。

当推导到这一步的时候,就很明显可以看出来是一个Power Sum。再把MDXT_loss代入到ICN公式中,可得

这个公式写到这一步以后,小P就觉得就好像明白了ICN到底是怎么来的了。咱们把这个公式拆成一部分一部分来理解。

1、多通道串扰比值Ri平方和

Ri表示的是每个aggressor对victim串扰耦合比值,因此这个平方和表示的就是所有关注的aggressor通道对victim的串扰集合(注意这个是平方和,能量和的概念)。单位为1。

2、能量频谱

W(f)就是前面咱们讲到的PWF(f),能量频谱分布系数。单位为1。

3、单位频率内的平均能量

A是电压幅值,平方可以认为是无损的总能量,fb是信号的波特率。两个相除后,单位为V^2/Hz。

4、单位频率宽度以及求和

delta_f就是在求和计算中我们的频率的step,从关注的最低频率fmin到波特率fb的求和个数以及单位频率宽度。单位为Hz。当然,这里的常数系数2,小P还没想明白。哪位明白人可以给小P讲解一下,小P不胜感激。

上述4个部分的计算结果单位已经是

因此,再开个平方根,那么单位就是V,也就是我们的ICN噪声。

以上公式需要注意一点,可以分开计算NEXT和FEXT的ICN噪声,然后再通过前面公式(85-32)的平方和开根号计算得出总的ICN。也可以在计算多通道串扰比值平方和的时候,就把NEXT和FEXT一起求平方和,然后通过ICN公式直接计算得出总的ICN噪声。

于是乎,小P也就搞明白ICN到底是个什么玩意儿了,ICN就是通过频域的S参数反推得到的被关注的单个通道收到的串扰总和的时域幅值。在2018 DesignCon的一篇paper里,也有这样的解释:

ICN provides a time domain representation of a channel characterized in the frequency domain using S-parameters.

Chien-Ping Kao, Brent Rothermel, Jeremy Stephens

关于ICN的学习记录暂时就写到这里,其实ICN衍生出来还有一个定义ccICN(component contribution ICN)。这个ccICN小P觉得另外再开一篇推文来记录会更清晰。

-

接收器

+关注

关注

14文章

2486浏览量

72504 -

连接器

+关注

关注

98文章

14835浏览量

137828 -

PCIe

+关注

关注

15文章

1281浏览量

83647 -

串扰

+关注

关注

4文章

189浏览量

27072

发布评论请先 登录

相关推荐

什么是串扰?如何减少串扰?

串扰学习笔记(2)

如何解决PCB串扰问题

串扰是怎么引起的 降低串扰有哪些方法

理解串扰Crosstalk

串扰学习笔记(1)

串扰学习笔记(1)

评论