目前集成电路的封装内部最常见的方式有「打线封装(Wire bonding)」与「覆晶封装(FCP:Flip Chip Package)」两种,如果芯片的正面朝上,也就是含有黏着垫的那一面朝上,通常使用「打线封装(Wafer bonding)

1.Wire bond原理: 对金属丝和压焊点同时加热和超声波,接触面便产生塑性变形,并破坏了界面的氧化膜,使其活性化,通过接触面两金属之间的相互扩散,形成金属化合物而完成连接。

2.常用线材: 金线,Ag合金线,钯铜线,纯铜线。 基于0.8mil,20um各种线材特性比较如下: 金线的主要优点: 硬度低,应力小,不容易产生弹坑。 抗氧化性好,在高温高湿下环境下的长期可靠性好。 缺点:成本较高,金属迁移率高,相比其他线材易产生Kirkendall Void。

银合金线的主要优点: 硬度低,应力小,不容易产生弹坑,成本低。 缺点:相比其他线材断裂载荷偏小。

铜线的主要优点: 成本低,电阻率小,金属迁移速率低,高温不易产生Kirkendall Void。 缺点:硬度大,容易产生弹坑,高温高湿下易腐蚀。

铜线和钯铜线优缺点比较:1)钯铜线具有更好的耐腐蚀性 2)钯铜线开封后可以存储7天,纯铜线只能存储3天。3)钯铜焊接时在纯氮气环境下,纯铜线需要在氮氢混合气体中。

打线封装的制作流程

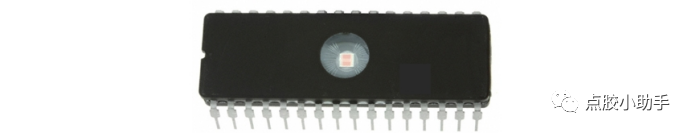

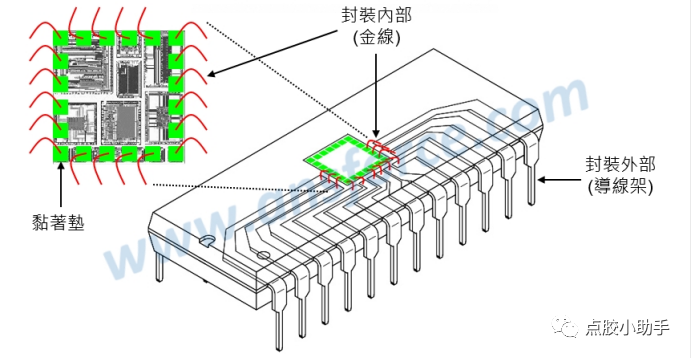

打线封装一般都使用「导线架」与「金线」,而且必须将黏着垫(Bond pad)制作在芯片的四周围,导线架的金属接脚(蜈蚣脚)也必须制作在集成电路封装外壳的四周围,如<图一>所示,因此打线封装的接脚数目不能太多。打线封装的步骤为:在靠近芯片的一侧,以机械钢嘴将金线加压加热打在芯片四周围的「黏着垫」上;在靠近导线架的一侧,以机械钢嘴将金线加压加热打在「导线架」上,打完第一根金线,再打第二根,依此类推。

图一打线封装技术。

打线封装最大的缺点是打线的动作必须「一根一根地」完成,非常费时;而且芯片上的黏着垫与导线架的金属接脚只能制作在四周围,所以当芯片上的CMOS数目愈多,传送的电讯号愈多,需要的金线也愈多,但是芯片的四周围空间有限,只能容纳固定数量的「黏着垫」,封装外壳的四周围空间也有限,只能容纳固定数量的「金属接脚」,因此打线封装接脚数目不能太多。然后将芯片放到lead frame上,并且用银浆固化,其实就是将芯片和lead frame的底部粘住啦。lead frame可以理解为引线框架,是一种阵列结构,

打线封装的应用

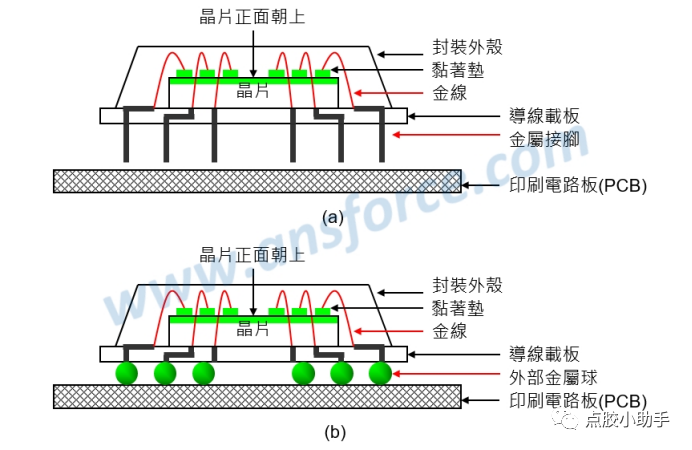

打线封装除了可以使用「导线架」之外,也可以使用「导线载板leadframe」,如<图二>所示,配合封装外部使用针格阵列(PGA)或球格阵列(BGA)如下:

内部打线封装,外部针格阵列(PGA):如<图二(a)>所示,是以前英特尔(Intel)的中央处理器(CPU)常用的封装方式,目前内部大都已经改用覆晶封装了。

内部打线封装,外部球格阵列(BGA):如<图二(b)>所示,是以前个人计算机的北桥芯片与南桥芯片经常使用的封装方式,目前内部大都已经改用覆晶封装了。

图二打线封装的应用。

打线封装的优缺点

优点:适合中小型芯片,大型芯片也有使用,技术较成熟。

缺点:每支接脚必须打线封装速度较慢,封装体积较大。

审核编辑:汤梓红

-

芯片

+关注

关注

463文章

54463浏览量

469537 -

集成电路

+关注

关注

5464文章

12695浏览量

375782 -

封装

+关注

关注

128文章

9339浏览量

149059

原文标题:了解打线封装吗?(Wire bonding)

文章出处:【微信号:半导体封装工程师之家,微信公众号:半导体封装工程师之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

芯片封装与芯片打线

封装打线强度测试

封装打线强度试验 (Wire Bond Test)

怎样进行芯片封装打线强度试验?

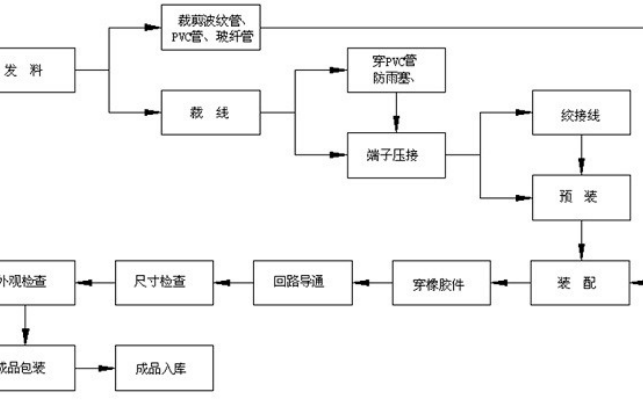

汽车线束的制作工程流程

Cadence PCB封装制作流程

打线封装的制作流程和应用

打线封装的制作流程和应用

评论