前段时间,一个朋友聊叙到这个后仿真任务命令都咋用,随即整理了下,可以完成基本的后仿真不成问题,但是如果还要完成一些其他的幺蛾子,那就需要各位仔细研读各工具的UserGuide了。下文如果觉得有帮助,烦请“三连”,当然加鸡腿也是可以的。。。哈哈哈,开玩笑了,只要对需要的人有用即可。

后仿真时,需要使用sdf对网表记性反标,即对网表中的时序信息记性“替换”,本文将示例常用的时序反标方法和一些EDA工具反标方法。

1 采用SystemVerilog(Verilog)系统任务

SystemVerilog和Verilog中在过程块中使用系统任务$sdf_annotate实现sdf文件对于网表的反标,其使用格式如下:

$sdf_annotate(sdf_file,module_instance,”config_file”,”log_file”,”mtm_spec”,”scale_factors”,”scale_type”);

其中各参数的主要意义如下:

sdf_file:指定要使用的sdf文件;

module_instance:指定sdf文件要反标的设计层次,需要注意的是此时指定的是例化名而非模块名。同时该参数本身是可选择的,默认实例名为调用$sdf_annotate所在模块的实例名(注意顶层模块名与实例名相同,可参阅《【168】仿真时为什么顶层不例化》);

config_file:指定进行反标时一些详细的反标控制信息,该选项可选,一般不指定,详细看参考各EDA工具帮助手册;

log_file:指定保存反标过程中产生的log信息文件名,该选项可选,建议指定,以方便查阅反标过程中的信息;

mtm_spec:指定反标的时序类型,也是可选项,反标常用类型主要有下表几种。

| 关键字 | 说明 |

| MAXMIN | 反标时选用最大延迟值 |

| MINIMUM | 反标时选用最小延迟值 |

| TOOL_CONTROL(默认) | 默认值,由仿真工具指定 |

| TYPICAL | 反标时选用典型值 |

这里需要注意,该参数为字符串类型,所以在任务中指定表格中的参数时需要给对应的关键字加上双引号。

scale_factors:指定最大延迟、最小延迟和典型延迟值的缩放因子,该选项也是可选的,一般情况下也不指定。该参数可以实现对于反标值的缩放,默认值为1.01.0,当然也可以指定不同的值,实现延迟值的不同缩放比例,例如,scale_factors设置为“1.2:1.3:1.4”,此时sdf中指定的反标值为“24”,那么实际反标给网表的值为“1.2*21.4*4”,即此时的实际反标值为“2.45.6”;

scale_type:该参数也属于可选项,用于指定缩放因子具体作用的延迟值,指定该参数后,confg_file中指定的配置文件中的SCALE_TYPE将会被覆盖掉,该参数可以指定的关键字如下表所示。

| 关键字 | 说明 |

| FROM_MAXMIN | 缩放因子仅作用于最大延迟值 |

| FROM_MINIMUM | 缩放因子仅作用于最小延迟值 |

| FROM_MTM(默认) | 缩放因子作用于min/typ/max |

| FROM_TYPICAL | 缩放因子仅作用于典型值 |

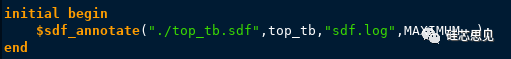

【示例】

其中第二个参数top_tb是要反标模块的例化名,一般从顶层开始写起。个人比较推荐使用该方法,因为该方法不依赖于具体的EDA工具,而下述的方法依赖于具体的EDA工具,也因此,这些依赖于具体工具的命令不能复用。

2 EDA工具反标

因为反标操作是发生在析构(elaboration)阶段完成的,所以可以在工具的析构阶段增加对应的参数实现反标操作。下面将针对Synopsys的VCSMX和Cadence的NCSIM进行示例说明。

2.1 VCSMX(Synopsys)

2.1.1命令行

在析构命令中增加如下参数选项,可以实现指定层次和sdf的反标,具体格式如下:

-sdf min|typ|maxfile_sdf

注意其中min、typ和max是可选的,根据需要指定。

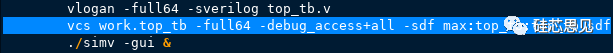

【示例】

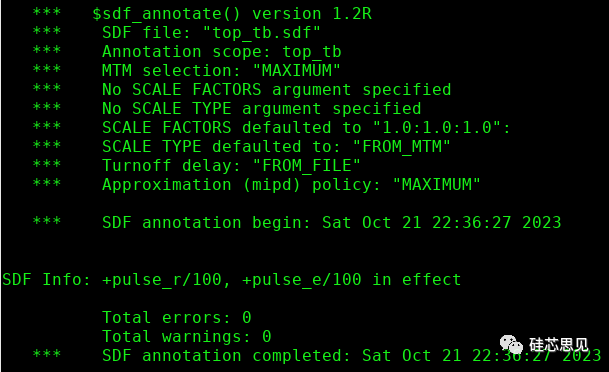

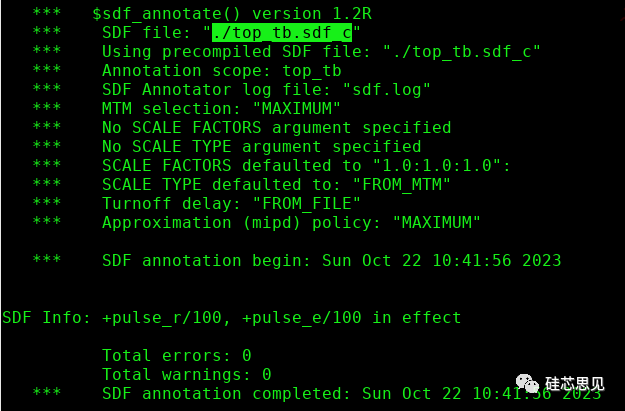

【反标信息】

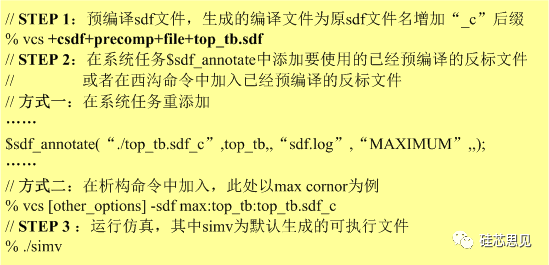

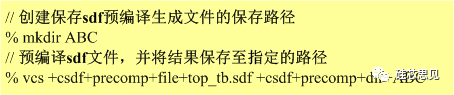

2.1.2 预编译方式

上面在析构命令中直接指定反标层次和sdf文件的方式存在一个问题,那就是如果我们的设计代码进行了修改,但是sdf文件并没有修改,此时如果编译完后,在析构的时候还要再进行一次sdf文件的解析反标,将会比较耗费时间,为此,一般的EDA工具都提供了另外一种反标方式,即对sdf文件进行预编译,如果sdf文件并没有修改,仅设计文件进行修改,此时就可以采用sdf预编译方式,具体操作步骤如下示例。

【示例】

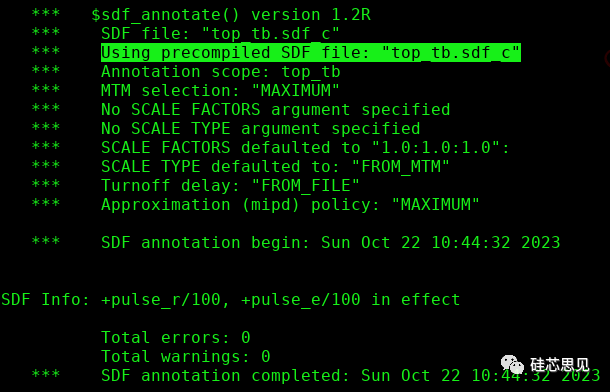

【反标信息一】在系统任务$sdf_annotate中添加要使用的已经预编译的反标文件

【反标信息二】在析构命令中加入已经预编译的反标文件,大家可以仔细观察下两者差异。

另外,在VCSMX中,还可以指定sdf预编译生成文件的保存路径,指定方式如下:

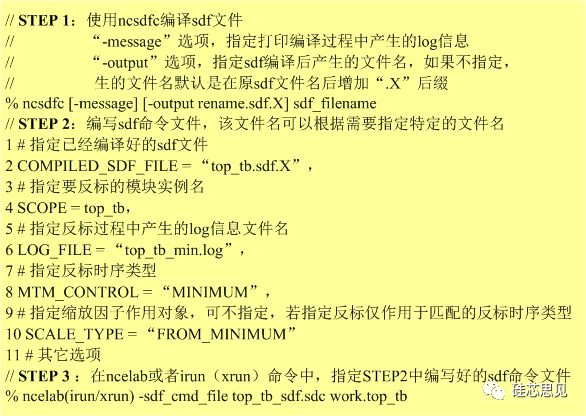

2.2 NCSIM

在NCSIM中使用较多的反标方式除了调用$sdf_annotate之外,就是采用命令文件的方式,其主要特点也是将sdf的编译与设计的编译分开,将sdf单独编译,在析构时再指定已经编译好的sdf文件,其具体操作如下示例。

【示例】

反标信息同上,此处不再赘述。另外,如果使用nc的64模式进行仿真,那么在编译析构命令中加上“-64bit”即可。

当然上述EDA工具对应的各种命令还有很多对应的参数,想了解的朋友可以参考对应工具的UserGuide,示例中仅是一些基本设置项,大家可以根据需要记性调整。

审核编辑:汤梓红

-

仿真

+关注

关注

50文章

4040浏览量

133412 -

Verilog

+关注

关注

28文章

1343浏览量

109980 -

System

+关注

关注

0文章

165浏览量

36881 -

eda

+关注

关注

71文章

2708浏览量

172865 -

时序

+关注

关注

5文章

385浏览量

37274

原文标题:常用的后仿真绝绝子---(VCSMX&NCSIM)

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Cadence 16.5 Concept HDL原理图反标后每个元件出现CDS_PART_NAME信息

Cadence 16.5 Concept HDL原理图打包反标后电源、地网络显示为红色

金橙子打标卡labview打标开发没头绪?c#封装成dll后labview调用真香!

如何将PT产生的SDF文件反标设计进行后仿真?

招标评标方法的适用性研究

直流锅炉汽温、汽压控制系统的反标架正规化设计

反熔丝FPGA配置和编程方法

反激电路工作原理和如何进行反激电路变压器的设计详细方法说明

单端反激式开关电源RCD反激钳位电路设计方法

常用的时序反标方法和EDA工具反标方法

常用的时序反标方法和EDA工具反标方法

评论