本节主要介绍:

vcs常用选项

vcs仿真流程

vcs代码覆盖率

vcs综合后后仿

图一乐技巧

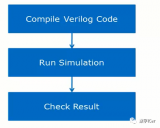

VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

vcs编译后,生成可执行二进制文件simv:执行./simv进行仿真;

vcs常用选项

vcs -help :列出所有vcs编译运行选项

-Mupdate :增量编译

-R:编译后立即执行仿真

-l:输出编译log的文件

-sverilog:支持systemverilog

+v2k:支持2001 verilog标准

-f:指定包含文件列表的filelist

-o:修改可执行文件simv文件名

-full64:支持64位模式下的编译仿真

-fsdb:dump fsdb波形

-ucli:在UCLI命令行模式下执行simv

-gui :DVE 界面运行

-work library:将设计库名称映射到接收vlogan输出的逻辑库名称work

-v lib_flie:搜索指定lib库文件

-y lib_dir:搜索指定lib库路径

+libext+ext:搜索具有指定文件扩展名的文件,如+libext+.v +.sv

+incdir+directory:搜索指定include文件路径

+define+macro:使用源代码中`ifdef所定义的宏或者define源代码中的宏

-parameters filename:将filename文件中指定的参数更改为此时指定的值

-timescale=1ns/1ns:设置仿真精度

-debug、debug_all、debug_pp:打开debug开关

vcs仿真流程

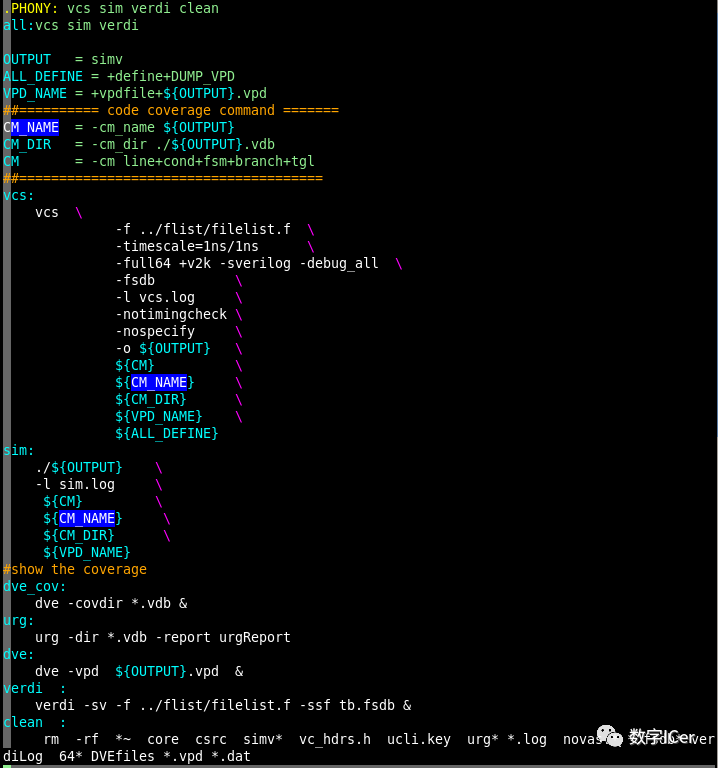

编写makefie脚本运行仿真:

makefie

执行下面编译仿真:

makevcs makesim

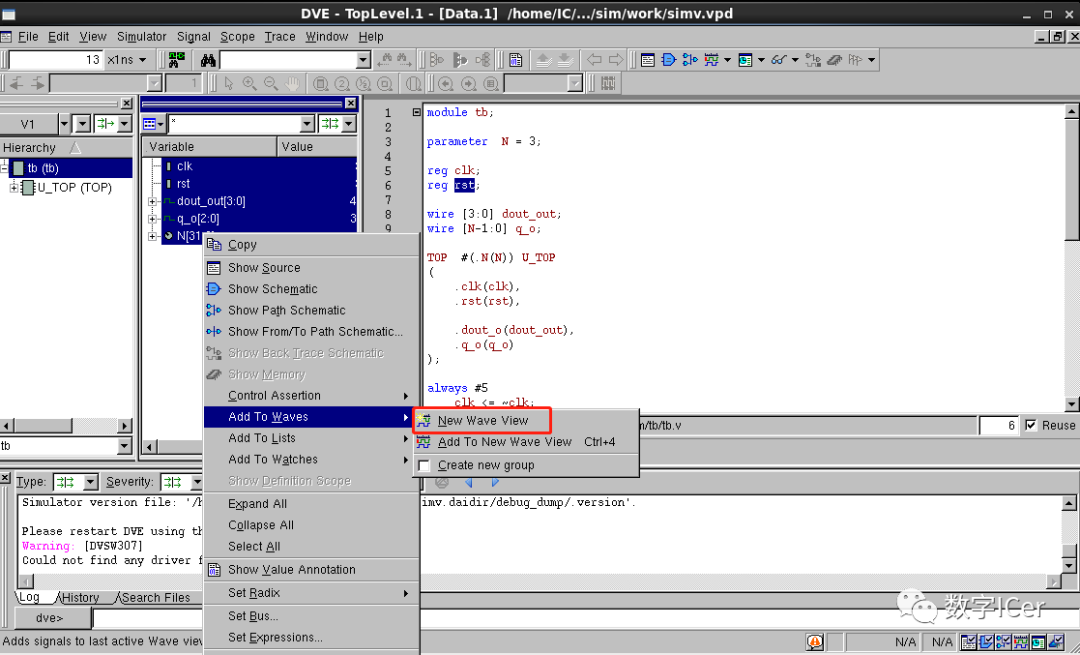

1.DVE图形界面打开

在编译时,使用 +vpdfile+filename 可以更改生成 VPD 文件的文件名,默认为vpdplus.vpd。

makefile中添加:

ALL_DEFINE=+define+DUMP_VPD VPD_NAME=+vpdfile+simv.vpd

仿真文件tb.v中添加:

`ifdefDUMP_VPD

initialbegin

$display("DumpVPDwave!");

$vcdpluson();

//$vcdpluson(0,tb);//记录tb及其所有子模块的波形。

//$vcdpluson(1,tb );//只记录tb层的波形

//$vcdpluson(2,tb );//记录tb层和tb下一层的波形

end

`endif

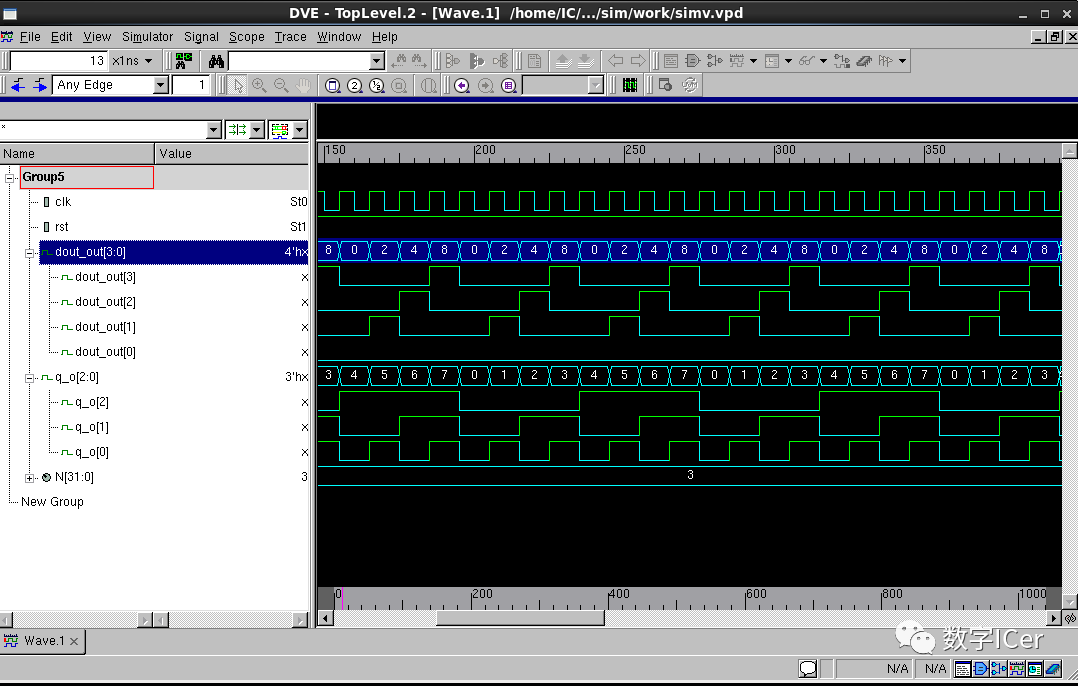

在仿真完成后,生成了simv.vpd 这个文件,这个文件记录了仿真过程中所有信号的波形,

可以使用dve打开:

dve-vpdsimv.vpd&

选中所有信号 --> 右键Add to Waves --> New Wave View

2.verdi图形界面打开

通常使用VCS生成fsdb格式的波形文件,将其导入另一个软件Verdi查看波形,代替DVE进行联合仿真;

vcs选项加上-fsdb,仿真文件tb.v中添加:

initialbegin

$display("Dumpfsdbwave!");

$fsdbDumpfile("tb.fsdb");

$fsdbDumpvars;

end

仿真完成后执行下面命令打开verdi:

makeverdi

推荐查看verdi实用技巧和fsdb实用技巧

代码覆盖率

在一个芯片验证的工程中,通常以代码覆盖率和功能覆盖率来体现验证是否完备;

功能覆盖率就是检查设计的功能是否完善,需要考虑很多不同的情况,是使用SV的重点内容。

代码覆盖率是检查代码是否存在冗余,检查所有的代码是否都已经执行,包括:行,状态机,翻转,条件,分支覆盖率等,这里只讨论代码覆盖率。

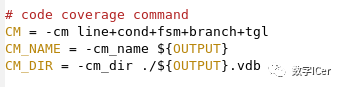

VCS在统计代码覆盖率的过程中,需要在编译和仿真命令上添加对应的开关选项,生成.vdb文件记录覆盖率情况。

再使用dve打开该文件进行查看覆盖率。

代码覆盖率选项

-cm

-cm_name:统计覆盖率文件名字。

-cm_dir:指定生成.vdb文件目录。

-cm_log+filename.log:记录仿真过程中log信息。

-cm_nocasedef: 在统计case语句的条件覆盖率时,不考虑default条件未达到的情况。

-cm_hier xxx.cfg:通过.cfg文件选择要查看覆盖率的模块或文件。

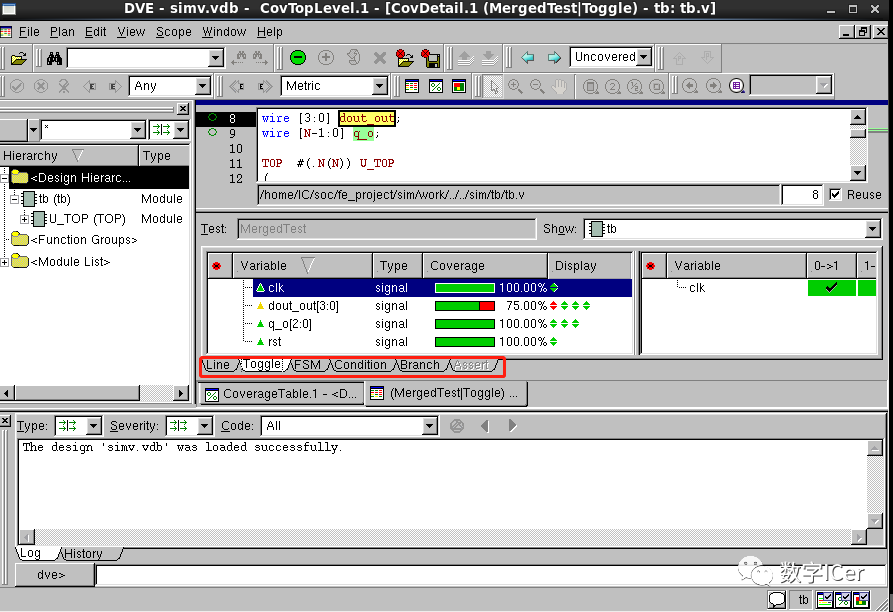

通过DVE查看覆盖率(方法1)

仿真完成后执行下面命令dve -covdir *.vdb &打开dve查看覆盖率:

makedve_cov

代码覆盖到的为绿色,没有覆盖到的为红色:

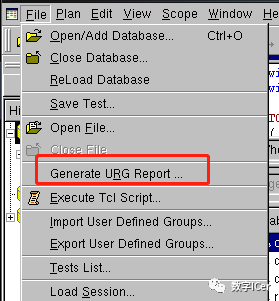

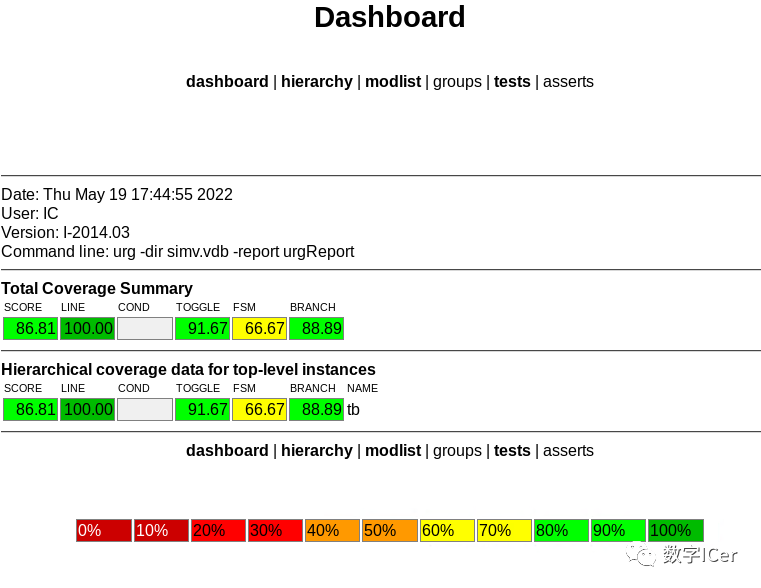

通过URG查看覆盖率(方法2)

可以以文本格式或者网页格式显示覆盖率;

或者:

urg-dir*.vdb-reporturgReport

进入urgReport目录,执行下面命令打开网页版,查看覆盖率报告

firefox*.html

综合后仿真

推荐查看综合与时序分析

推荐查看后仿及反标

vcs门级网表仿真

当RTL功能仿真通过之后,DC工具中进行逻辑综合,在逻辑综合完成之后,需要对综合生成的网表再进行仿真验证。

综合后包含电路的实际信息,如映射的门电路信息、寄生参数、.v的网表、SDF标准延时信息、SDC约束、工作条件等信息。

后仿选项

后仿不需要的选项

带时序的后仿,一定要注意仿真器是否关闭了notimingcheck和nospecify的选项。

如果有-nospecify,那么SDF中的时序信息就反标不到仿真模型中;

如果有-notimingcheck,那么后仿过程中就不检查时序违例,后仿就失去了意义。

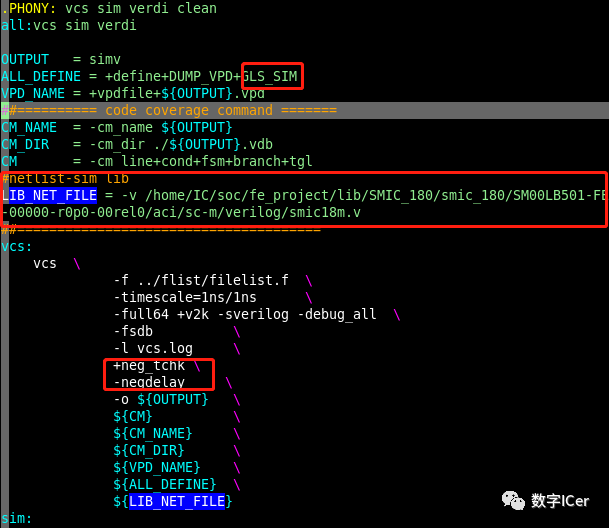

后仿添加选项

+neg_tchk:若要使用负延时检查,在编译后仿时必须包含+neg_tchk选项。如果省略此选项,VCS将所有负延迟更改为0。

-negdelay:用于SDF文件中有负延迟,如果省略此选项,VCS将所有负延迟更改为0。

sdf_annotate反标

使用$sdf_annotate将SDF文件反标到网表中:

$sdf_annotate("sdf_file"[,module_instance][,"sdf_configfile"][,"sdf_logfile"][,"mtm_spec"][,"scale_factors"][,"scale_type"]);

在tb中加载sdf文件,指定反标模块:

`ifdefGLS_SIM

initialbegin

$sdf_annotate("../../netlist_sim/sdf/TOP.sdf",tb.U_TOP,,"sdf.log","TYPICAL");

end

`endif

修改makefie脚本运行仿真:

LIB_NET_FILE指定的是基本的工艺库单元,因为网表文件netlist_TOP.v中包括综合后的由门电路和触发器等例化形成的verilog文件,所以需要基本的工艺库单元。

makefile

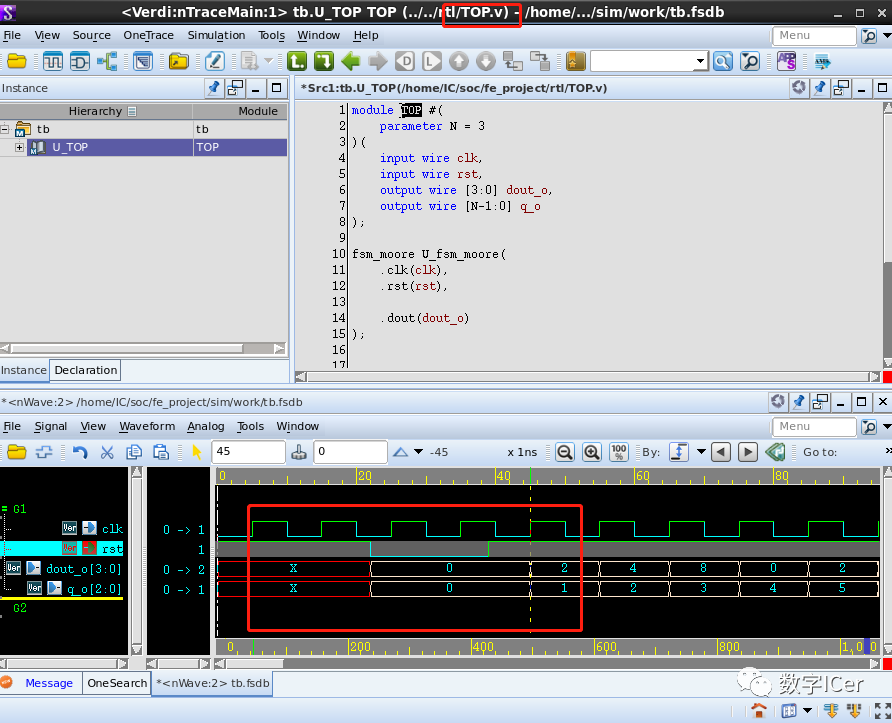

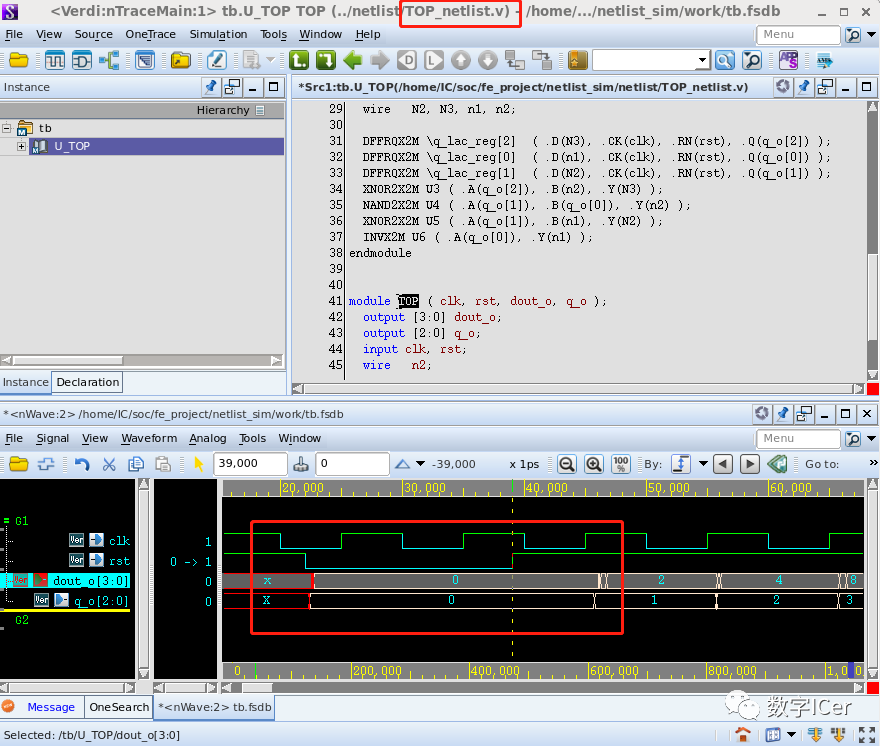

rtl仿真和netlist仿真结果对比:

可以看到netlist仿真的输出信号存在一些毛刺及延迟,与理想的没有延迟信息的rtl仿真不同。

rtl仿真

netlist仿真

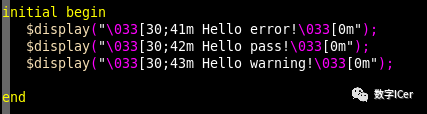

图一乐技巧

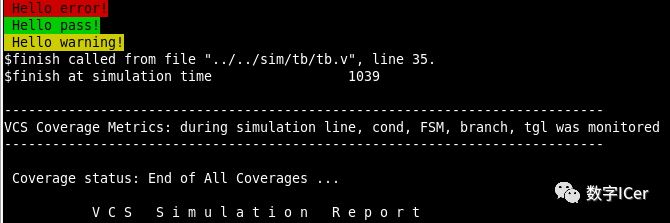

display打印彩色字/背景

可在仿真中加入颜色显示case的情况,如:

红色:前景色31,背景色41:

$display("�33[31;41mHelloerror!�33[0m");

绿色:前景色32,背景色42:

$display("�33[32;42mHellopass!�33[0m");

黄色:前景色33,背景色43:

$display("�33[33;43mHellowarning!�33[0m");

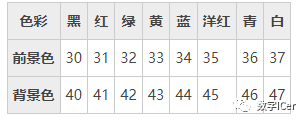

涉及的颜色:

涉及的颜色

审核编辑:汤梓红

-

Linux

+关注

关注

87文章

11304浏览量

209461 -

仿真器

+关注

关注

14文章

1018浏览量

83739 -

Verilog

+关注

关注

28文章

1351浏览量

110091 -

VCS

+关注

关注

0文章

79浏览量

9605 -

代码

+关注

关注

30文章

4787浏览量

68591

原文标题:vcs实用技巧

文章出处:【微信号:数字芯片设计工程师,微信公众号:数字芯片设计工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是VCS

基于linux系统实现的vivado调用VCS仿真教程

vcs实用技巧

vcs实用技巧

评论