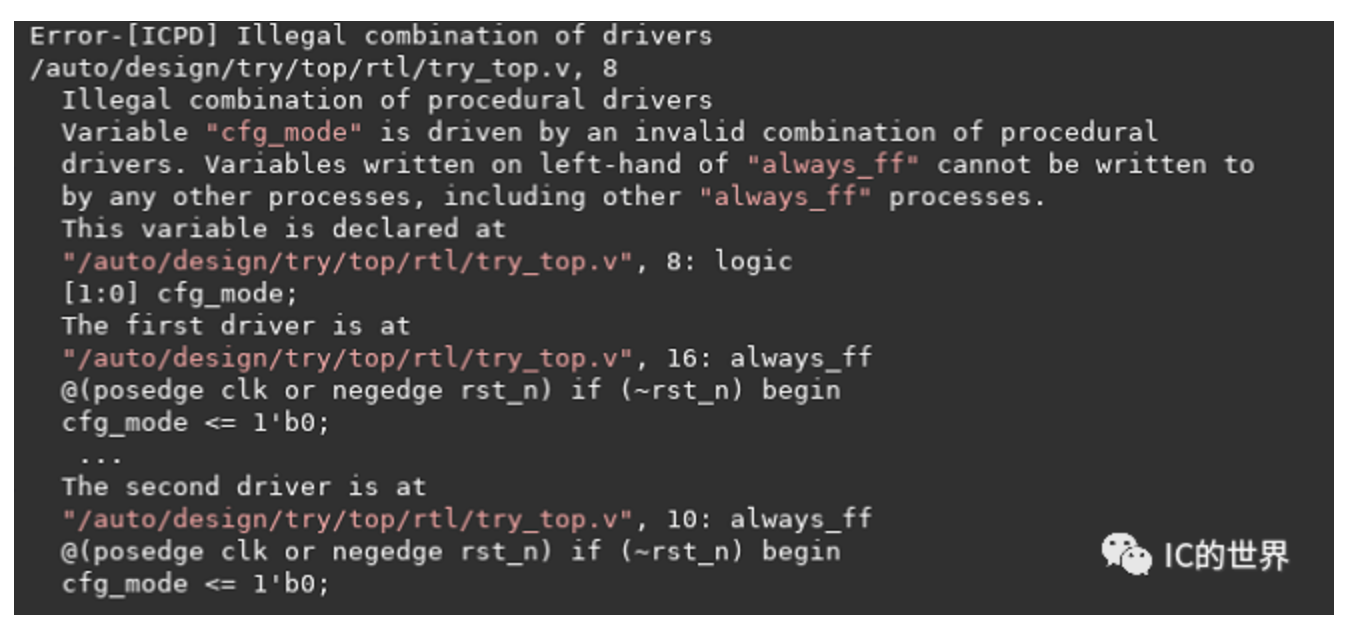

我们再从对可综合代码的支持角度看看SystemVerilog相比于Verilog的优势。针对硬件设计,SystemVerilog引入了三种进程always_ff,always_comb和always_latch。always_ff用于描述时序逻辑,对应FPGA中的触发器,其内部应使用非阻塞(<=)赋值方式,因为它模拟的正是触发器传输数据的方式。always_comb用于描述纯组合逻辑,其内部使用阻塞赋值方式,采用了隐式的全变量敏感列表。always_latch用于描述锁存器。FPGA设计中一般不建议使用锁存器。这样,三种进程对应三种场景,无论是设计者还是工具本身对电路意图都非常清晰。在Verilog中,只有always,换言之,这三种进程都能通过always实现。例如:

always @(posedge clk) 对应 always_ff@(posedge clk)

always @* 对应always_comb或always_latch

SystemVerilog引入了转换操作符,支持类型转换、位宽转换和符号转换。

类型转换:casting_type’(expression)

位宽转换:size’(expression)

符号转换:signed’(expression) 和unsigned’(expression)

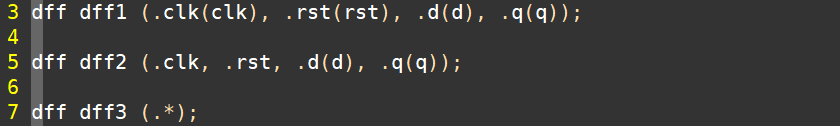

再从端口映射看,SystemVerilog支持Verilog传统的一一映射方式,如下图所示代码第3行。同时也支持自动匹配,如代码第5行,.clk和.rst会自动与名为clk和rst的信号相连。而更为简洁的是代码第7行所示的.*连接方式,这表明所有端口将自动与其名字相同的信号相连。尽管这三种方式都是可综合的,但从代码风格角度而言,仍然建议采用第3行所示方式。在描述测试文件时,可采用第7行所示方式。

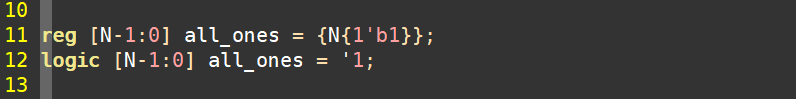

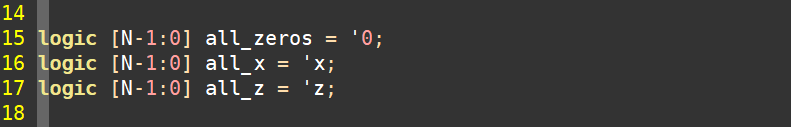

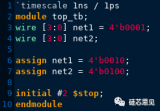

在Verilog中,给一个信号所有位赋值为1,需要采用如下图所示方式,而SystemVerilog可直接采用下图代码第12行所示方式。同时此方式还适用于赋值全0、全X和全Z。

审核编辑:汤梓红

-

FPGA

+关注

关注

1635文章

21836浏览量

608240 -

Verilog

+关注

关注

28文章

1355浏览量

110827 -

System

+关注

关注

0文章

165浏览量

37213 -

触发器

+关注

关注

14文章

2024浏览量

61482

原文标题:SystemVerilog不只是用于验证(2)

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SystemVerilog学习一 —— 计数器

相比较于LPDDR4X,LPDDR5有哪些优势?

SystemVerilog 3.1a语言参考手册

SystemC 和SystemVerilog的比较

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计

从Verilog PLI到SystemVerilog DPI的演变过程

verilog-2005和systemverilog-2017标准规范

systemverilog:logic比reg更有优势?

SystemVerilog在硬件设计部分有哪些优势

systemverilog:logic比reg更有优势

SystemVerilog相比于Verilog的优势

SystemVerilog相比于Verilog的优势

评论