点击上方蓝字关注我们

引言

21世纪是电子信息产业主导的知识经济时代,信息领域正在发生一场巨大变革,其先导力量和决定性因素正是微电子集成电路。硅片技术的日益成熟,特别是深亚微米(DSM,Deep Sub-Micron)和超深亚微米(VDSM,Very Deep Sub-Micron)技术,极大促进了集成电路产业的快速发展。

集成电路发展经历了电路集成、功能集成、技术集成,直至今天基于计算机软硬件的知识集成,这标志着传统电子系统已全面进入现代电子系统阶段,这也被誉为进入3G时代,即单片集成度达到1G个晶体管、器件工作速度达到1GHz、数据传输速率达到1Gbps。

EDA(Electronic Design Automation,电子设计自动化)技术基于计算机辅助设计,它融合了应用电子技术、计算机技术、信息处理技术、智能化技术的最新成果,以实现电子产品的自动设计。EDA是现代电子设计技术的核心,在现代集成电路设计中占据重要地位。FPGA(Field Programmable Gate Array,现场可编程门阵列)作为可编程逻辑器件的典型代表,它的出现及日益完善适应了当今时代的数字化发展浪潮,它正广泛应用在现代数字系统设计中。

EDA技术与FPGA原理

1.EDA技术特征

EDA是电子设计领域的一场革命,它源于计算机辅助设计(CAD,Computer Aided Design)、计算机辅助制造(CAM,Computer Aided Made)、计算机辅助测试(CAT,Computer Aided Test)和计算机辅助工程(CAE,Computer Aided Engineering)。利用EDA工具,电子设计师从概念、算法、协议开始设计电子系统,从电路设计、性能分析直到IC版图或PCB版图生成的全过程均可在计算机上自动完成。

EDA代表了当今电子设计技术的最新发展方向,其基本特征是设计人员以计算机为工具,按照自顶向下的设计方法,对整个系统进行方案设计和功能划分,由硬件描述语言完成系统行为级设计,利用先进的开发工具自动完成逻辑编译、化简、分割、综合、优化、布局布线(PAR,Place And Route)、仿真及特定目标芯片的适配编译和编程下载,这被称为数字逻辑电路的高层次设计方法。

作为现代电子系统设计的主导技术,EDA具有两个明显特征:即并行工程(Concurrent Engineering)设计和自顶向下(Top-down)设计。其基本思想是从系统总体要求出发,分为行为描述(Behaviour Description)、寄存器传输级(RTL,Register Transfer Level)描述、逻辑综合(Logic Synthesis)三个层次,将设计内容逐步细化,最后完成整体设计,这是一种全新的设计思想与设计理念。

2.FPGA原理

今天,数字电子系统的设计方法及设计手段都发生了根本性变化,正由分立数字电路向可编程逻辑器件(PLD,Programmable Logic Device)及专用集成电路(ASIC,Application Specific Integrated Circuit)转变。FPGA与CPLD(Programmable Logic Device,复杂可编程逻辑器件)都属于PLD的范畴,它们在现代数字系统设计中正占据越来越重要的地位。

FPGA是由用户编程来实现所需逻辑功能的数字集成电路,它不仅具有设计灵活、性能高、速度快等优势,而且上市周期短、成本低廉。FPGA设计与ASIC前端设计十分类似,在半导体领域中FPGA应用日益普及,已成为集成电路中最具活力和前途的产业。同时,随着设计技术和制造工艺的完善,器件性能、集成度、工作频率等指标不断提升,FPGA已越来越多地成为系统级芯片设计的首选。

FPGA由PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)发展而来,其基本设计思想是借助于EDA开发工具,用原理图、状态机、布尔表达式、硬件描述语言等方法进行系统功能及算法描述,设计实现并生成编程文件,最后通过编程器或下载电缆用目标器件来实现。

FPGA器件采用逻辑单元阵列(LCA,Logic Cell Array)结构、SDRAM工艺,其中LCA由三类可编程单元组成。

(1)可配置逻辑块(CLB,Configurable Logic Block):被称为核心阵列,是实现自定义逻辑功能的基本单元,散布于整个芯片;

(2)输入/输出模块(IOB,Input/Output Block):排列于芯片四周,为内部逻辑与器件封装引脚之间提供可编程接口;

(3)可编程互连资源(PI,Programmable Interconnect):包括不同长度的连线线段及连接开关,其功能是将各个可编程逻辑块或I/O块连接起来以构成特定电路。

全球生产FPGA的厂家很多,但影响力最大的是Xilinx公司和Altera公司,世界上第一片FPGA是在20世纪80年代中期Xilinx公司率先推出的。不同厂家生产的FPGA在可编程逻辑块的规模、内部互连线结构及所采用的可编程元件上存在较大差异,实际使用时应注意区分。

FPGA设计应用及优化策略

1.FPGA设计层次分析

FPGA设计包括描述层次及描述领域两方面内容。通常设计描述分为6个抽象层次,从高到低依次为:系统层、算法层、寄存器传输层、逻辑层、电路层和版图层。对每一层又分别有三种不同领域的描述:行为域描述、结构域描述和物理域描述。

系统层是系统最高层次的抽象描述,针对于电子系统整体性能。算法层又称为行为层,它是在系统级性能分析和结构划分后对每个模块的功能描述。算法层所描述的功能、行为最终要用数字电路来实现。而数字电路本质上可视为由寄存器和组合逻辑电路组成,其中寄存器负责信号存储,组合逻辑电路负责信号传输。寄存器传输层描述正是从信号存储、传输的角度去描述整个系统。寄存器和组合逻辑本质上是由逻辑门构成,逻辑层正是从逻辑门组合及连接角度去描述整个系统。

FPGA各个描述层次及综合技术关系如图1所示。传统的综合工具是将寄存器传输级(RTL)的描述转化为门级描述。随着以行为设计为主要标志的新一代系统设计理论的不断成熟,能够将系统行为级描述转化为RTL描述的高层次综合技术不断涌现。

作为现代集成电路设计的重点与热点,FPGA设计一般采用自顶向下、由粗到细、逐步求精的方法。设计最顶层是指系统的整体要求,最下层是指具体的逻辑电路实现。自顶向下是将数字系统的整体逐步分解为各个子系统和模块,若子系统规模较大则进一步分解为更小的子系统和模块,层层分解,直至整个系统中各子模块关系合理、便于设计实现为止。

2.VHDL在FPGA设计中的应用

集成电路设计规模及复杂度不断增大,用传统原理图方法进行系统级芯片设计已不能满足设计要求,而硬件描述语言(HDL,Hardware Description Language)在进行大规模数字系统设计时具有诸多优势,因此利用硬件描述语言进行系统行为级设计已成为FPGA与ASIC设计的主流。目前最流行、最具代表性的硬件描述语言是美国国防部(DOD)开发的VHDL(VHSIC Hardware Description Language)和GDA(Gateway Design Automation)公司开发的Verilog HDL。

VHSIC代表Very High Speed Integrated Circuit,因此VHDL即甚高速集成电路硬件描述语言。VHDL语法严格,1987年即成为IEEE标准,即IEEE STD 1076-1987,1993年进一步修订成为IEEE STD 1076-1993。

VHDL作为IEEE标准,已得到众多EDA公司支持,其主要优点有:

● 描述能力强,支持系统行为级、寄存器传输级和门级三个层次设计;

● 可读性好、移植性强,其源文件既是程序又是文档,便于复用和交流;

● 支持自顶向下的设计和基于库(Library-based)的设计;

● 支持同步、异步及随机电路的设计;

● 与工艺无关,生命周期长。

VHDL语言主要应用在行为层和寄存器传输层,这两层可充分发挥出VHDL面向高层的优势。利用VHDL实现数字电路的实质是利用综合工具将高层次描述转化为低层次门级描述,其中综合可分为三个层次:高层次综合(High-Level Synthesis)、逻辑综合(Logic Synthesis)和版图综合(Layout Synthesis)。

3.基于VHDL的FPGA系统行为级设计FPGA设计应用及优化策略

1.FPGA设计层次分析

FPGA设计包括描述层次及描述领域两方面内容。通常设计描述分为6个抽象层次,从高到低依次为:系统层、算法层、寄存器传输层、逻辑层、电路层和版图层。对每一层又分别有三种不同领域的描述:行为域描述、结构域描述和物理域描述。

系统层是系统最高层次的抽象描述,针对于电子系统整体性能。算法层又称为行为层,它是在系统级性能分析和结构划分后对每个模块的功能描述。算法层所描述的功能、行为最终要用数字电路来实现。而数字电路本质上可视为由寄存器和组合逻辑电路组成,其中寄存器负责信号存储,组合逻辑电路负责信号传输。寄存器传输层描述正是从信号存储、传输的角度去描述整个系统。寄存器和组合逻辑本质上是由逻辑门构成,逻辑层正是从逻辑门组合及连接角度去描述整个系统。

FPGA各个描述层次及综合技术关系如图1所示。传统的综合工具是将寄存器传输级(RTL)的描述转化为门级描述。随着以行为设计为主要标志的新一代系统设计理论的不断成熟,能够将系统行为级描述转化为RTL描述的高层次综合技术不断涌现。

作为现代集成电路设计的重点与热点,FPGA设计一般采用自顶向下、由粗到细、逐步求精的方法。设计最顶层是指系统的整体要求,最下层是指具体的逻辑电路实现。自顶向下是将数字系统的整体逐步分解为各个子系统和模块,若子系统规模较大则进一步分解为更小的子系统和模块,层层分解,直至整个系统中各子模块关系合理、便于设计实现为止。

2.VHDL在FPGA设计中的应用

集成电路设计规模及复杂度不断增大,用传统原理图方法进行系统级芯片设计已不能满足设计要求,而硬件描述语言(HDL,Hardware Description Language)在进行大规模数字系统设计时具有诸多优势,因此利用硬件描述语言进行系统行为级设计已成为FPGA与ASIC设计的主流。目前最流行、最具代表性的硬件描述语言是美国国防部(DOD)开发的VHDL(VHSIC Hardware Description Language)和GDA(Gateway Design Automation)公司开发的Verilog HDL。

VHSIC代表Very High Speed Integrated Circuit,因此VHDL即甚高速集成电路硬件描述语言。VHDL语法严格,1987年即成为IEEE标准,即IEEE STD 1076-1987,1993年进一步修订成为IEEE STD 1076-1993。

VHDL作为IEEE标准,已得到众多EDA公司支持,其主要优点有:

● 描述能力强,支持系统行为级、寄存器传输级和门级三个层次设计;

● 可读性好、移植性强,其源文件既是程序又是文档,便于复用和交流;

● 支持自顶向下的设计和基于库(Library-based)的设计;

● 支持同步、异步及随机电路的设计;

● 与工艺无关,生命周期长。

VHDL语言主要应用在行为层和寄存器传输层,这两层可充分发挥出VHDL面向高层的优势。利用VHDL实现数字电路的实质是利用综合工具将高层次描述转化为低层次门级描述,其中综合可分为三个层次:高层次综合(High-Level Synthesis)、逻辑综合(Logic Synthesis)和版图综合(Layout Synthesis)。

具体包括以下重要环节:设计输入(Design Entry)、设计综合(Design Synthesis)、设计约束(Design Constraints)、设计实现(Design Implement)、设计仿真(Design Simulation)和器件编程(Device Programming)。

设计输入主要采用HDL(硬件描述语言)、ECS(Engineering Schematic Capture,原理图编辑器)和FSM(Finite State Machine,有限状态机);

设计综合就是依据逻辑设计描述和约束条件,利用开发工具进行优化处理,将HDL文件转变为硬件电路实现方案,其实质就是优化设计目标的过程;

设计约束主要包括设计规则约束、时间约束、面积约束三种,通常时间约束的优先级高于面积约束;

设计实现对于FPGA分为编译规划、布局布线(PAR,Place And Route)、程序比特流文件产生;对于CPLD则是编译、配置、比特流文件产生;

设计仿真分为功能仿真和时序时延仿真。功能仿真在设计输入之后、综合之前进行,只进行功能验证,又称为前仿真。时序时延仿真在综合和布局布线之后进行,能够得到目标器件的详细时序时延信息,又称为后仿真;

器件编程是指在功能仿真与时序时延仿真正确的前提下,将综合后形成的位流编程下载到具体的FPGA/CPLD芯片中,又称芯片配置。FPGA/CPLD编程下载通常可使用JTAG编程器、PROM文件格式器和硬件调试器三种方式,其中JTAG(Joint Test Action Group,联合测试行动组)是工业标准的IEEE 1149.1边界扫描测试的访问接口,用作编程功能可省去专用的编程接口,减少系统引出线,有利于各可编程逻辑器件编程接口的统一,因此应用广泛。

4.FPGA设计优化及方案改进

在FPGA设计中,必须首先明确HDL源代码编写非常重要;不同综合工具包含的综合子集不同致使有些HDL语句在某些综合工具中不能综合;同一逻辑功能可用不同HDL语句进行描述,但占用资源却可能差别很大。同时应当深刻理解并发性是硬件描述语言与普通高级语言的根本区别,因而设计硬件电路不能受传统顺序执行思维的束缚。

此外,我们应当清楚速度优化与面积优化在FPGA设计中占有重要地位。对于大多数数字系统设计而言,速度常常是第一要求,但FPGA结构特性、综合工具性能、系统电路构成、PCB制版情况及HDL代码表述都会对工作速度产生重要影响。我们通过在电路结构设计中采用流水线设计、寄存器配平、关键路径法可以进行速度优化。

(1)流水线设计

流水线(Pipelining)技术在速度优化中相当流行,它能显著提高系统设计的运行速度上限,在现代微处理器、数字信号处理器、MCU单片机、高速数字系统设计中都离不开流水线技术。图4与图5是流水线设计的典型图示,其中图4未使用流水线设计,图5采用了2级流水线设计,在设计中将延时较大的组合逻辑块切割成两块延时大致相等的组合逻辑块,并在这两个逻辑块中插入了触发器,即满足以下关系式:Ta=T1+T2,T1≈T2。通过分析可知,图4中Fmax≈1/Ta;图5中流水线第1级最高工作频率Fmax1≈1/T1,流水线第2级最高工作频率Fmax2≈1/T2≈1/T1,总设计最高频率为Fmax≈Fmax1≈Fmax2≈1/T1,因此图5设计速度较图4提升了近一倍。

(2)寄存器配平(Register Balancing)

寄存器配平是通过配平寄存器之间的组合延时逻辑块来实现速度优化,两个组合逻辑块延时差别过大,导致设计总体工作频率Fmax取决于T1,即最大的延时模块,从而使设计整体性能受限。通过对图7设计进行改进,将延时较大的组合逻辑1的部分逻辑转移到组合逻辑2中,成为图8结构,以减小延时T1,使t1≈t2,且满足T1+T2=t1+t2。寄存器配平后的图8结构中Fmax≈1/t1>1/T1,从而提高了设计速度。

(3)关键路径法

关键路径是指设计中从输入到输出经过的延时最长的逻辑路径,优化关键路径是提高设计工作速度的有效方法。图9中Td1>Td2,Td1>Td3,关键路径为延时Td1的模块,由于从输入到输出的延时取决于延时最长路径,而与其他延时较小的路径无关,因此减少Td1则能改善输入到输出的总延时。

在优化设计过程中关键路径法可反复使用,直到不可能减少关键路径延时为止。许多EDA开发工具都提供时序分析器可以帮助找到延时最长的关键路径,以便设计者改进设计。对于结构固定的设计,关键路径法是进行速度优化的首选方法,可与其他方法配合使用。

在FPGA设计中,面积优化实质上就是资源利用优化,面积优化有多种实现方法,诸如资源共享、逻辑优化、串行化,其中资源共享使用较多,下面举例说明。

在利用FPGA设计数字系统时经常遇到同一模块需要反复被调用,例如多位乘法器、快速进位加法器等算术模块,它们占用芯片资源很多,使系统成本及器件功耗大幅上升,因而使用资源共享技术能够显著优化资源。图10和图11是资源共享的一个典型实例,由图可见使用资源共享技术节省了一个多位乘法器,从而达到减少资源消耗、优化面积的目的。 最后针对FPGA的设计实现提出一些改进方案,FPGA实现分为编译规划、布局布线(PAR,Place And Route)、程序比特流文件生成三个阶段,当设计不满足性能指标或不能完全布线时,可进行以下改进工作:

● 使用定时约束(Timing Constraints);

● 增大布局布线级别(PAR Effort);

● 对关键通路(Critical Paths)的数字逻辑重新设计;

● 运行重布线(Re-entrant Routing);

● 运行MPPR(Multi-Pass Place & Route,多通路布局布线);

● 运行平面布局(Floorplan)查看布局图及连通性。

下面重点介绍Re-entrant Routing与MPPR,它们都可改进布局布线结果,提高系统性能。其中Re-entrant Routing是指已运行过PAR后再次运行PAR,但跳过布局过程直接进行布线,如图12所示。MPPR则是根据不同功耗表(Cost tables)来运行PAR多次,通过对每一个PAR迭代评分来确定最好路径并保留,其中评分依据是未布线的连线个数、连线延迟与时序约束。

结束语

当今社会,集成电路产业已成为高技术产业群的核心战略产业,已逐渐演化为设计、制造、封装、测试协调发展的产业结构,它正进入以知识产权为创新核心的新时期。这标志着集成电路产业的竞争已由技术竞争、资本竞争进入到智力和知识产权竞争的高级阶段。

FPGA在集成电路设计应用中占有重要地位,现场可编程性是FPGA最突出的优点。用户通过利用强大的开发工具,能在最短时间内对FPGA内部逻辑进行反复设计及修改,直至满意为止,这大大缩短了产品设计开发周期,提高了最终产品性能。因而FPGA以其独有的技术优势在电子设计领域得到越来越广泛的应用。随着科学发展及工艺进步,作为重中之重的集成电路设计业必将遇到更大的挑战及发展机遇。

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:EDA技术与FPGA设计应用的详细阐述

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1628文章

21722浏览量

602870

原文标题:EDA技术与FPGA设计应用的详细阐述

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

国标网线标准详细阐述

智多晶EDA工具HqFpga软件实用小功能

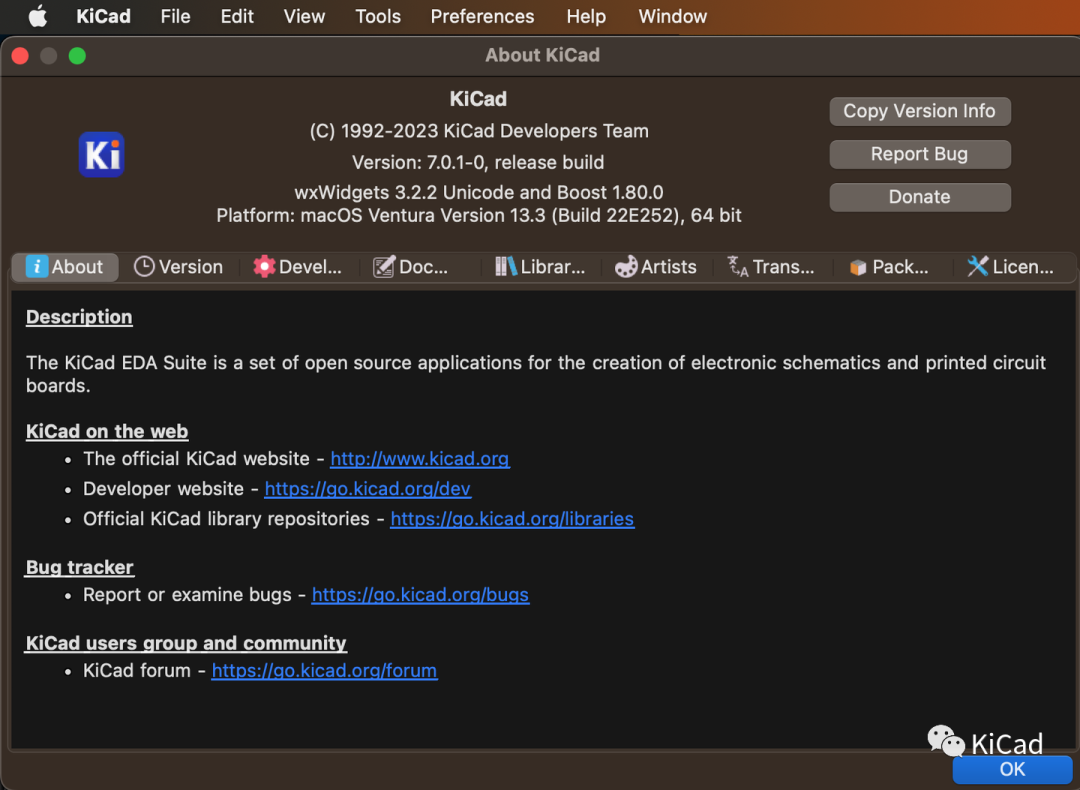

KiCad EDA版本说明

如何提升EDA设计效率

FPGA如何消除时钟抖动

基于FPGA的人脸识别技术

基于FPGA的图像采集与显示系统设计

为昕原理图设计EDA软件(Jupiter)试用

国内EDA工具AI技术应用现状及发展动态分析

EDA技术与FPGA设计应用的详细阐述

EDA技术与FPGA设计应用的详细阐述

评论