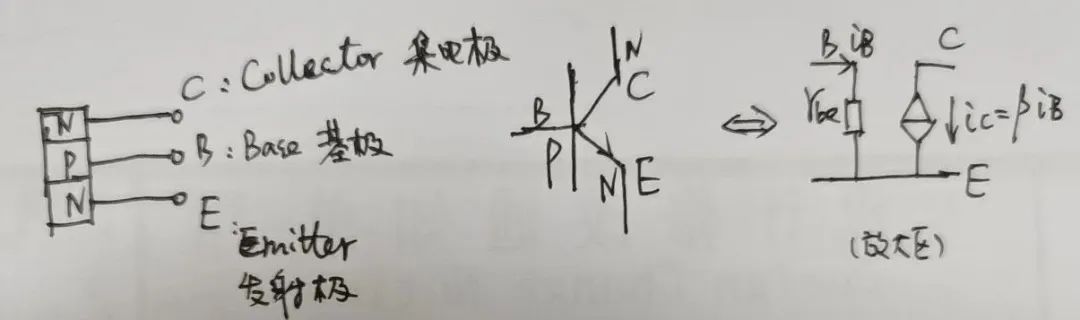

一 NPN和PNP晶体管

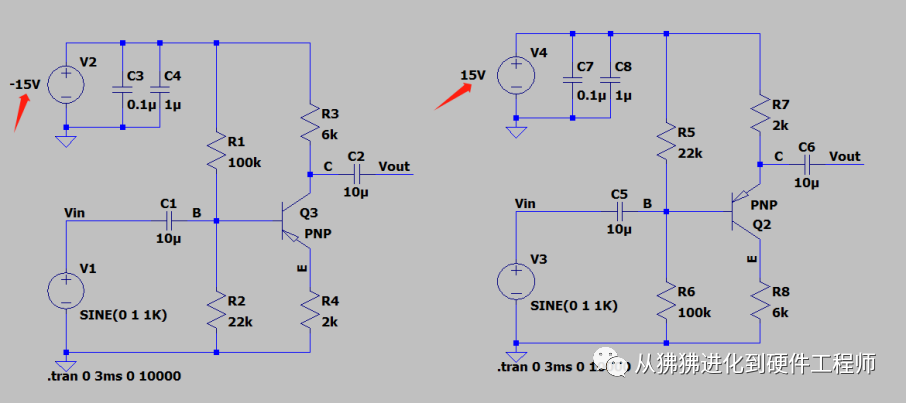

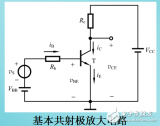

晶体管有NPN和PNP两种类型。上篇展示的电路都是NPN晶体管搭建的放大电路。使用PNP晶体管搭建电路,因为电流流动方向相反,所以偏置电压方向也要反过来,因此将电源和GND进行交换。如下是使用PNP晶体管搭建的两种放大电路。

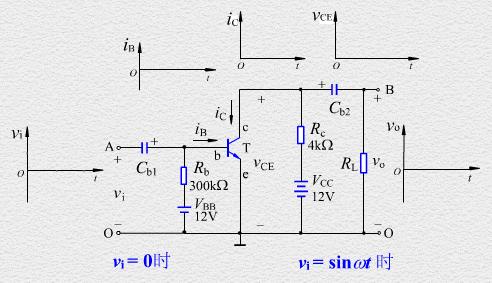

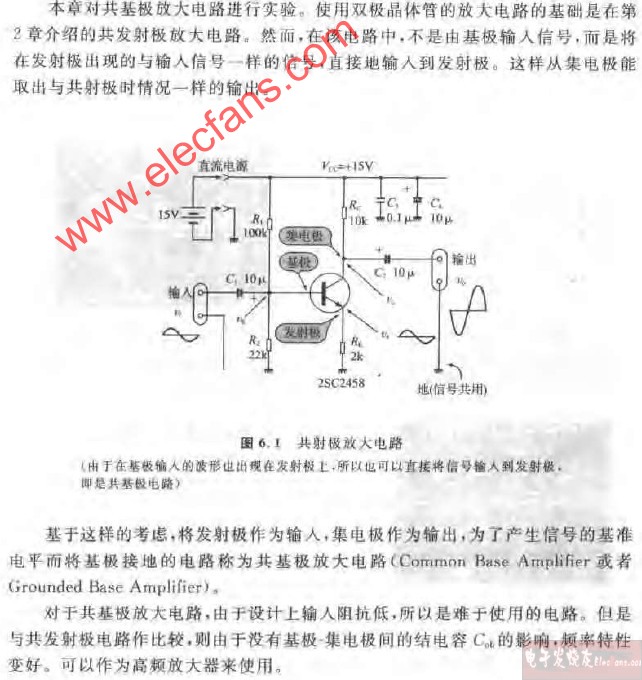

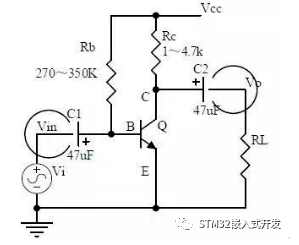

二 设计一个共射极放大电路

让我们基于如下产品需求设计一个共射ji极放大电路:

电压增益:3倍

最大输出电压:6Vpp

频率特性:暂不考虑

输入输出阻抗:暂不考虑

第一步:确定电源电压V2

基于最大输出电压,选择电源电压V2。为了获得不失真的6Vpp,电源电压必须比信号最大电压高。同时要考虑,为了使发射极有电流流过,在发射极上需要有电压。因此电源电压要大于信号电压+发射极电压的和。

而对发射极来说,我们期望它的电压在2V以上。因为虽然Vbe≈0.6V,不过它有个温度特性,元件温度每升高一度,Vbe减小2.5mV。这样的话,随着电路工作时间变长,Vbe的电压会减小,导致Ve的电压会减小。因此我们期望Re的直流电压在2V以上。

基于以上的考虑,电源电压V2应该在8V以上。我们选择15作为V2的输出电压。

第二步:选择晶体管

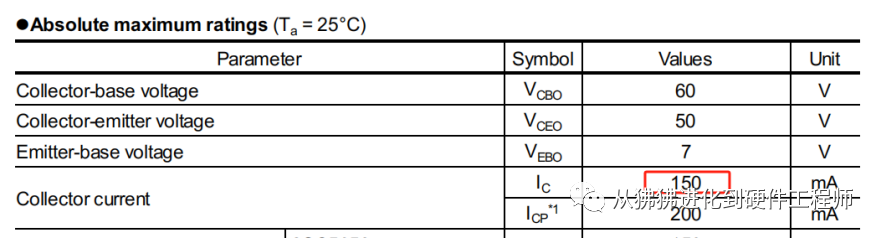

晶体管的特性决定了放大电路的最终性能(噪声、高频特性等)。另外晶体管的最大额定电压不能超过放大电路要求的。例如如果我们选择电源(V2)是15V,,那么在集电极和基极之间、集电极和发射极之间有可能施加最大15V的电压,因此选择晶体管时,Vcbo和Vceo要大于15V。如下是ROHM的2SC2414K的spec,我们选择它设计放大电路。

第三步:确定发射极工作电流

在确定发射极电流之前,先介绍一个参数fT。在上面的spec中出现。它是晶体管的特征频率,表示交流电流放大系数为1时的频率。它的值和发射极电流有关联。如下图。如果希望用此晶体管设计的放大电路频率特性最好,必须是IE=30mA。

另外,放大电路的噪声也和发射极电流有关。需要注意的是,同一颗晶体管频率特性最好的IE和噪声特性最好的IE是不一样的。

如果放大电路对频率和噪声没有严格要求,那么IE取值范围就比较宽松了,只要不大于spec定义的最大额定电路150mA(下图)即可。

我们取IE=1mA,方便后续计算。

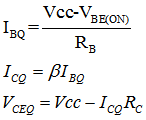

第四步:确定集电极电阻和发射极电阻

前一篇提到此放大电路的放大倍数是由集电极电阻和发射极电阻的比值决定的。因此如果Av=3,则R3:R4=3。

前面也提到我们设定VE=2V,

因此得到R4=VE/IE=2V/1mA=2KR

R3=Av x R4=6KR

VCE=VC-VE=V2 - IC x R3 - IE x R4 =15V - 1mA x 6KR -1mA x 2KR=7V

同时得到晶体管的集电极损耗Pc为

Pc=VCE x IE =4V x 1mA =4mW

它低于元件spec定义的Pd=200mW最大值。

另外,集电极电阻R3的取值也会影响输出波形。如果R3取值太大,在其自身的压降变大,集电极电位下降,在输出大振幅信号时,输出波形的下侧会失真。最好是将集电极电位设置在V2和VE的中点。

注:V2的电压会影响VE电压和IE。如果V2不是15V,例如是12V,则VE不是2V,IE也不是1mA。

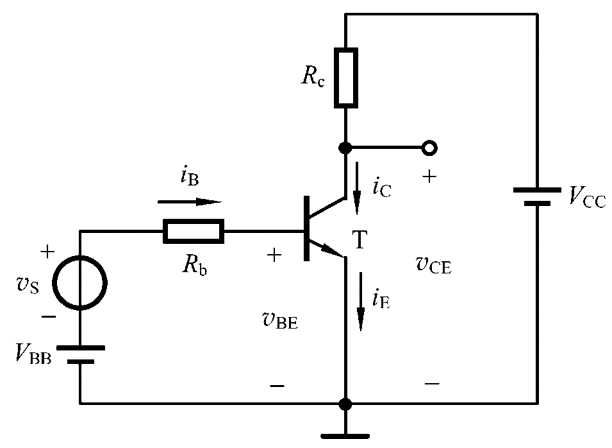

第五步:确定基极偏置电路

因为已经设定VE=2V,又因为VBE=0.6V,因此VB=2.6V。

VB的电压是由R1和R2分压得到。如果VB,也即R2上的分压为2.6V,那么R1上的压降为V2-VB=12.4V。

这颗晶体管的hFE在120~390之间,取个中间值hFE=200,那么基极电流大约在5uA。我们希望流过R1和R2的电流比基极电流大的多(10倍以上就可以),因此设定流过R1的电流是100uA,那么就可以得到R1和R2的阻值

R1=12.4V/100uA=124KR

R2=2.6V/100uA=26KR

不过这两个电阻在电阻系列中不多见(E24系统数列),选择和它俩比值一样的另一组电阻100KR和22KR。不改变R1和R2的比值,是因为比值变了,VB就会变。

通过以上几步,电路的基本框架就搭出来了。

如下图是电路和它的各个直流电压和电流,与计算基本一致。

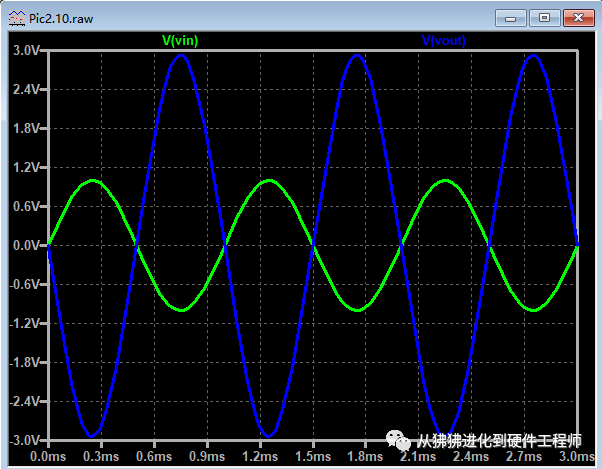

信号放大比例是3倍

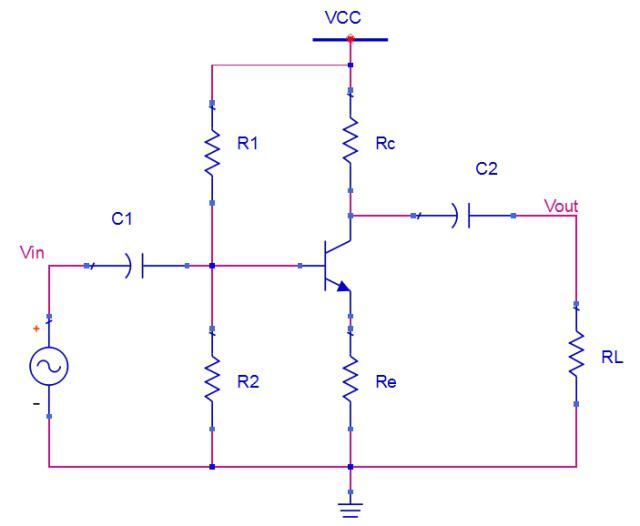

C1和C2的作用是将基极/集电极的直流电压挡住,只让交流信号输入/输出。C1和电路的输入阻抗、C2和负载分别组成高通滤波器。

输入阻抗是R1和R2的并联,因为从交流信号的角度,电源和地是一样的,又因为基极电流非常小,可以认为晶体管本身的输入阻抗非常大,因此输入阻抗是R1和R2的并联。输出阻抗是由C2和RL构成。

当C1和C2取值太小时,会导致截止频率太高,在滤波效果上使低频信号难于通过,此处选择C1=C2=10uF

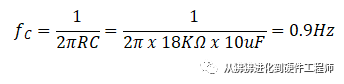

输入端的高通滤波器截止频率fC为:

第七步:电源去耦电容C3和C4的选择

C3和C4是电源的去耦电容,降低电源和GND之间的交流阻抗,也称为旁路电容。如果没有这些电容存在,电路的交流特性会变差,严重时电路会产生振荡。

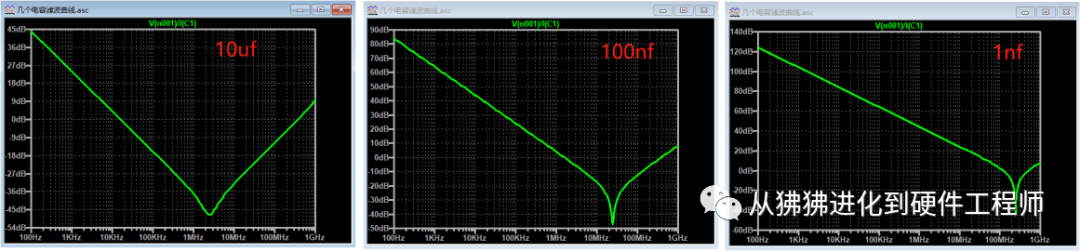

电容的阻抗值是1/2πfC,信号频率越高,阻抗越低。现实中,由于电容结构中寄生电感的影响,当超过某一频率时,电容阻抗反而会上升。如下图三种不同容值的电容,它们各自的阻抗曲线。

在电源设计时,并联容值大小不同的电容,使整个电源网络对GND的交流阻抗在一定的频率段内都比较小。具体的频率范围,可以看负载端的需求。以TI的SOC J6为例,它的spec中对200MHz以内的电源网络交流阻抗有明确要求。

将这三颗电容并联之后的阻抗曲线如下:可以看到在很宽的频率范围内都下降了。小容值电容要布置在电源附近。否则寄生电感变大,影响阻抗和滤波效果。

至此,一个基本的共射极放大电路就搭建好了。

-

放大电路

+关注

关注

104文章

1782浏览量

106570 -

电路设计

+关注

关注

6666文章

2430浏览量

203385 -

晶体管

+关注

关注

77文章

9639浏览量

137870 -

pnp

+关注

关注

11文章

295浏览量

51724 -

共射极放大电路

+关注

关注

0文章

39浏览量

3317

发布评论请先 登录

相关推荐

共射极放大电路设计步骤

共射极放大电路设计步骤

评论