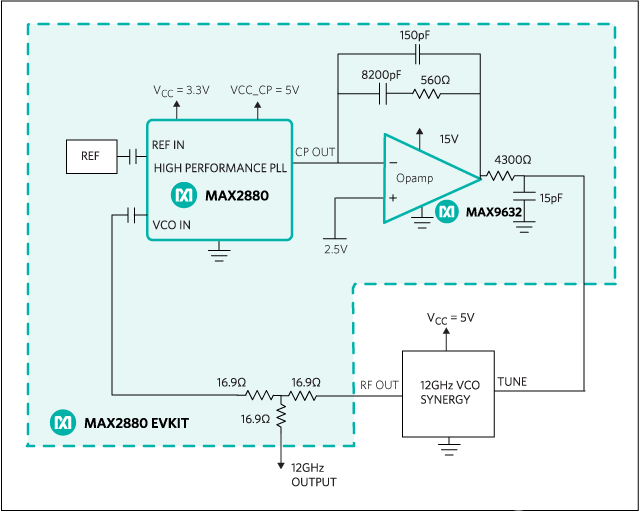

本应用笔记详细介绍了具有外部VCO的完整12GHz、超低相位噪声小数N分频锁相环(PLL)的设计。它由高性能小数N分频PLL (MAX2880)、基于运算放大器的有源环路滤波器(MAX9632)和12GHz VCO (SYNERGY DXO11751220-5)组成。

主要特点:

- 超低相位噪声:92 飞秒 RMS 抖动 (1kHz-20MHz)* 无需外部分频器* 有源滤波器,调谐范围为0.5V至15V

这款高性能PLL可用于生成混频器本振(LO)频率或ADC/DAC时钟,适用于微波点对点系统、测试和测量设备或汽车雷达中的应用。

本应用笔记中包含相位噪声性能数据和详细的设置指南。

*附件:文章-应用-笔记-文件-设计-A-12GHz-超低相位噪声-0.09-PS-rms-抖动-锁相环1.pdf

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

锁相环

+关注

关注

35文章

590浏览量

88052 -

pll

+关注

关注

6文章

785浏览量

135491 -

VCO

+关注

关注

13文章

190浏览量

69486

发布评论请先 登录

相关推荐

电源技巧#8:设计12GHz,超低相位噪声(0.09 ps rms抖动)锁相环

详细介绍了具有外部VCO的完整12GHz,超低相位噪声分数N锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880),基于运算放大器的有源环路滤波器(MAX9632)和

发表于 12-10 10:02

•45次阅读

电源技巧#8:设计12GHz,超低相位噪声(0.09 ps rms抖动)锁相环

详细介绍了具有外部VCO的完整12GHz,超低相位噪声分数N锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880),基于运算放大器的有源环路滤波器(MAX9632)和

发表于 12-10 09:50

浅析低相噪Hittite锁相环产品

频率源可以说是一个通信系统的心脏,心脏的好坏很大程度上决定着一个机体的健康状况,而锁相环又是频率源的主要组成部分,因此性能优异的锁相环芯片对于通信系统来说是非常重要的。锁相环的相位

发表于 06-25 06:22

CN0369 低相位噪声的转换锁相环频率合成器

图1所示电路框图是一个低相位噪声转换环路频率合成器(也称为偏移环路)。此电路将ADF4002 锁相环 (PLL) 的较低100 MHz参考频率转换到5.0 GHz至5.4

发表于 05-29 08:17

•20次下载

12GHz、超低相位噪声小数N分频锁相环的设计

本应用笔记详细介绍了集成外部VCO的完整12GHz、超低相位噪声小数N分频锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880)、基于运算放大器的有源环路滤波器(MAX9

锁相环相位噪声的影响因素

锁相环(Phase Locked Loop, PLL)相位噪声是评估锁相环性能的重要指标之一,它描述了输出信号相位的不稳定性。

数字锁相环固有的相位抖动是怎样产生的,如何解决

数字锁相环(DPLL)固有的相位抖动主要来源于多个方面,这些抖动因素共同影响着锁相环的同步精度和稳定性。以下是数字锁相环

设计12GHz、超低相位噪声(0.09 ps rms抖动)锁相环

设计12GHz、超低相位噪声(0.09 ps rms抖动)锁相环

评论