如何在COMSOL中优化合并解?

在COMSOL中,优化合并解指的是在分析中使用优化模块以找到最佳解决方案的过程中合并模拟结果。在本文中,我们将详细介绍如何实现此目标。

1. 使用多个模型

在COMSOL中,使用多个模型是优化合并解的第一个步骤。您可以创建多个模型以探索不同的参数和方案。每个模型都可以保存在不同的文件中,并在需要时进行加载和分析。确保您在每个模型中定义和优化的参数都是唯一的,以便之后可以直接进行对比。

2. 存储输出结果

在每次模拟之后,将输出结果存储在文件或文件夹中,以便稍后合并。使用COMSOL导出器可以轻松导出结果数据,例如曲线,图像和表。导出的文件保存在您的电脑中。

3. 比较结果

对于每个模型和每个参数,比较结果是必要的。这将有助于您确定哪些参数组合提供了最佳的结果。您可以自己比较结果,但是简单地描述和比较大量的数据可能会引起混乱。因此,建议使用COMSOL的数据组合工具,这些工具可以在单个界面中同时查看多个模型的结果。

4. 使用优化模块

COMSOL优化模块是一种高级工具,可以通过数字算法和参数优化技术来确定最佳结果。优化模块可以与多个模型和结果一起使用,以确定哪个参数设置提供了最佳结果。在使用优化模块之前,请仔细定义您要优化的参数,并确保您已经在您的模型中定义了一个优化器。

5. 合并结果并进行验证

在完成分析之后,您需要合并所有模拟数据并对结果进行验证。为此,使用COMSOL可能很困难,您可以使用其他工具进行数据处理和合并。使用这些工具,您可以将不同模型和参数的数据合并到单个电子表格中,以简化处理。

总结

优化合并解是在COMSOL中使用优化模块找到最佳解决方案的一种方法。如果您按照上述步骤执行,它将帮助您在探索不同参数和模型时管理和处理数据。使用多个模型,存储结果,比较结果,使用优化模块并验证结果是实现优化合并解的关键步骤。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

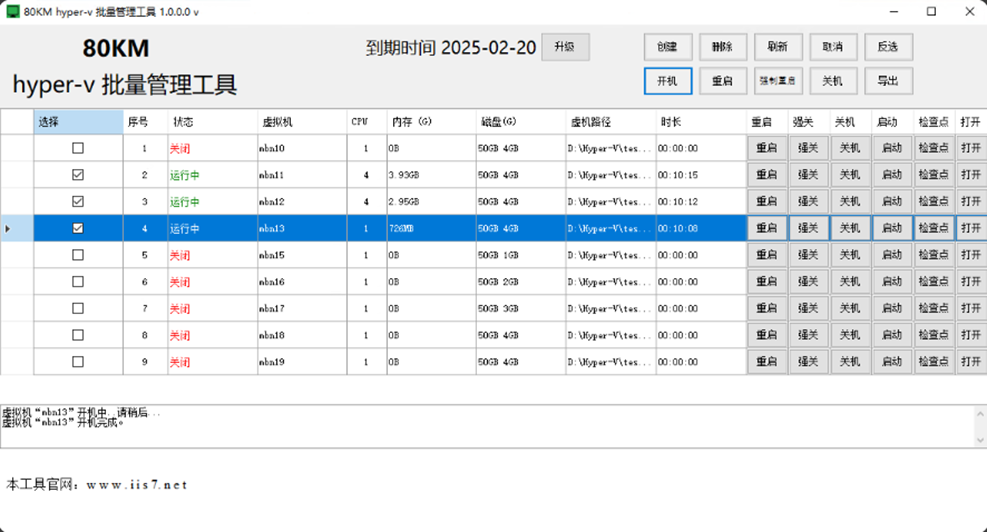

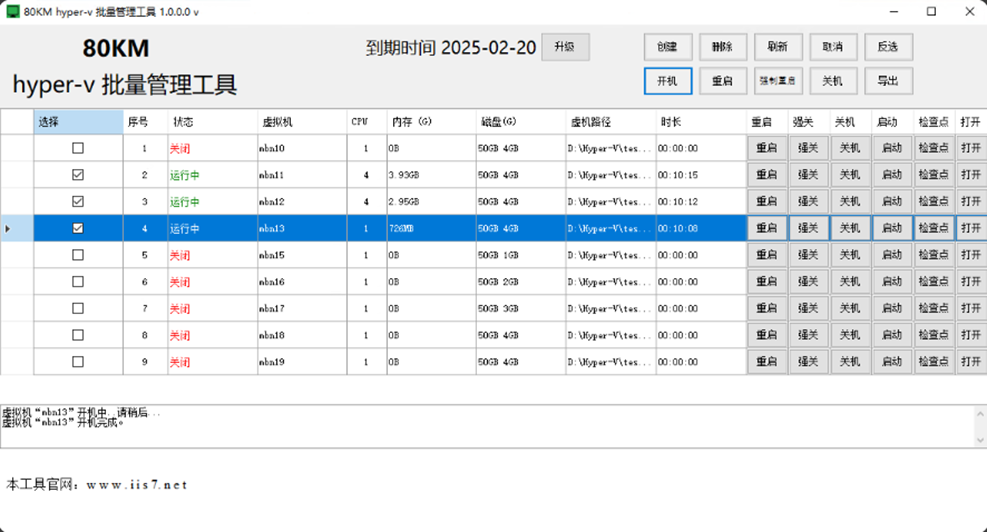

:如何在虚拟机中配置和优化显卡性能。 在虚拟化环境中,显卡性能对于需要高图形处理能力的应用场景(如游戏、图形设计和视频编辑)至关重要。Hyper-V提供了多种显卡配置和

![的头像]() 发表于

发表于 01-24 14:19

•355次阅读

推出合并后的5G网络。 CMA在审查过程中认为,沃达丰与Three的合并有可能对英国移动行业的竞争格局产生积极影响。因此,在确保合并后企业能够履行其投资承诺的前提下,CMA决定给予此次

![的头像]() 发表于

发表于 12-06 13:53

•208次阅读

在电路中优化GND连接以及应对GND在高频应用中的挑战,是确保电路性能稳定、减少干扰和噪声的关键环节。以下是对这两个方面的介绍: 一、优化GND连接的方法 使用适当的布局技术 : 在P

![的头像]() 发表于

发表于 11-29 15:25

•848次阅读

在电路设计中优化电阻的使用,可以从以下几个方面进行: 一、选择合适的电阻类型和规格 电阻类型 : 根据电路的工作频率选择合适的电阻类型。例如,在高频电路中,应选择具有较低介质损耗的电阻,如金属膜电阻

![的头像]() 发表于

发表于 10-31 09:30

•429次阅读

想知道如何在Altium Designer中快速定位器件嘛?

![的头像]() 发表于

发表于 10-12 09:28

•4339次阅读

电子发烧友网站提供《如何在反激式拓扑中实现软启动.pdf》资料免费下载

发表于 09-04 11:09

•0次下载

的是产品或技术系统的理想化状态,即低成本、高功能、高可靠性、无污染等特性的完美结合。 在机器人电机控制设计中,工程师们常常面临诸多挑战,如如何在提高控制精度的同时降低能耗和噪音,如何在有限的资源下实现最优的系统

![的头像]() 发表于

发表于 08-13 10:19

•526次阅读

分享如何在Xilinx Breadboardable Spartan-7 FPGA, CMOD S7中实现4位伪随机数发生器(PRNGs)。

![的头像]() 发表于

发表于 08-06 11:20

•767次阅读

在FPGA(现场可编程门阵列)中实现状态机是一种常见的做法,用于控制复杂的数字系统行为。状态机能够根据当前的输入和系统状态,决定下一步的动作和新的状态。这里,我们将详细探讨如何在FPGA设计中实现状态机,包括其基本概念、类型、设

![的头像]() 发表于

发表于 07-18 15:57

•723次阅读

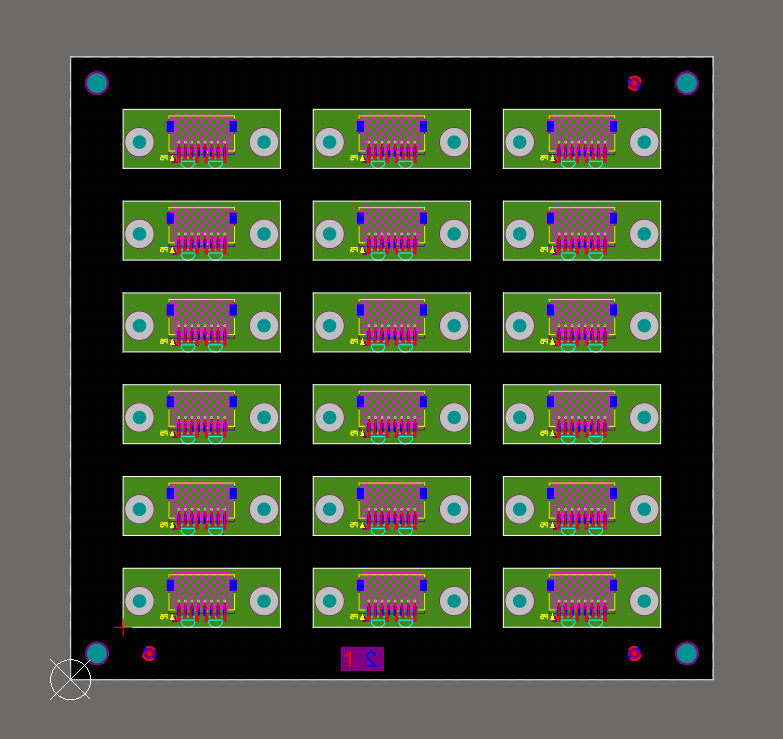

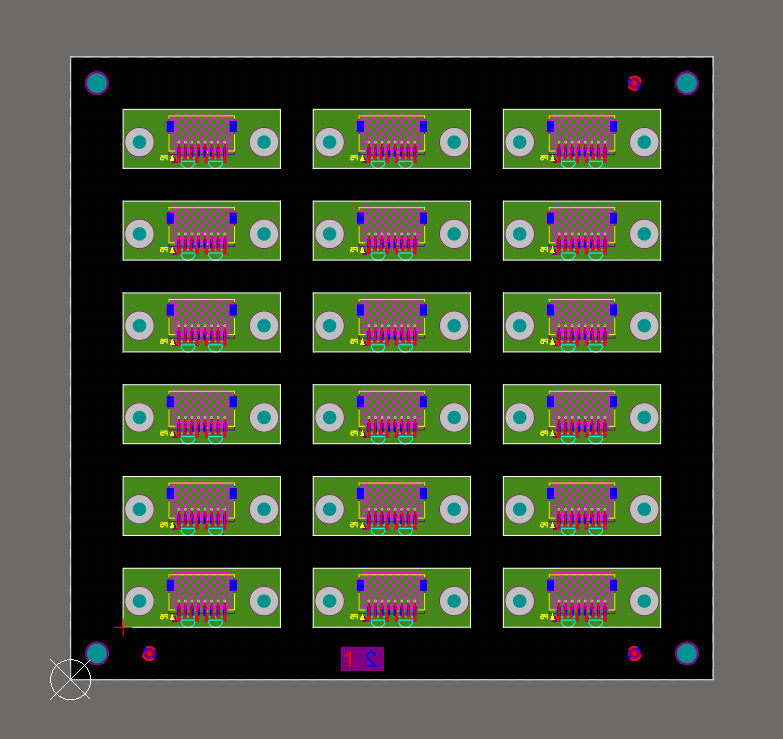

在制作PCB的过程中,绘制面板制造图纸是不可或缺的一步。单个PCB的制造图纸只显示单个PCB的钻孔和板特征,但这些需要合并到整个面板的一张图纸中。根据不同公司或制造商的具体需求,一些设计团队需要接手创建面板图纸,包括指定拆板方法

![的头像]() 发表于

发表于 07-16 09:30

•645次阅读

等人提出,主要用于手写数字识别任务(如MNIST数据集)。下面,我将详细阐述如何在PyTorch中从头开始实现LeNet-5网络,包括网络架构设计、参数初始化、前向传播、损失函数选择、优化器配置以及训练流程等方面。

![的头像]() 发表于

发表于 07-11 10:58

•865次阅读

我使用lv_port_esp32测试LVGL显示正常,但是在将其合并到我自己基于ESP_IDF(v4.2.1)工程中的时候遇见了问题。我将lv_examples、lvgl

发表于 06-21 12:43

大家好,

我有个问题请教,cmakelists.txt中的变量如何在程序中使用?比如以下cmakelists.txt文件中的PROJECT_VER变量,我如何在c程序中使用?试了很多办

发表于 06-11 07:34

如何在代码中动态修改手指电容

发表于 05-22 07:11

作为一款强大的多物理场仿真软件,为超材料和超表面的研究提供了强大的仿真工具。本文将重点介绍COMSOL Multiphysics在周期性超表面透射反射分析中的应用,以期为相关领域的研究提供

发表于 02-20 09:20

如何在COMSOL中优化合并解?

如何在COMSOL中优化合并解?

评论