为何测出的相位噪声性能低于ADIsimPLL仿真预期值?

相位锁定环(PLL)是一种重要的电路,可用于在不同领域中应用,如无线通信、数据传输、数字信号处理等。PLL将信号同步到参考时钟的频率和相位,以保证信号的稳定性和准确性。其中一个重要的指标是相位噪声,它表征PLL锁定的相位偏移情况。在PLL的设计和应用过程中,相位噪声性能是一个非常关键的指标,因为它直接影响系统的性能和精度。本文将就为何测出的相位噪声性能低于ADIsimPLL仿真预期值这个问题进行详尽、详实、细致的探讨。

1. 频率分辨率的影响

首先从频率分辨率的角度来看,ADIsimPLL仿真预期值与实际测量的相位噪声值之间可能有偏差。理论上,频率分辨率越高,测量的相位噪声值就越精确,但是实际上,由于实验装置的限制,无法达到理论上的频率分辨率。因此,实际测量得到的相位噪声值可能比仿真预期值要大。此时可以通过增加测量时的频率分辨率或者使用更高精度的测量设备来提高测量精度,从而得到更准确的测量结果。

2. 仿真模型的不足

其次从仿真模型的角度来看,ADIsimPLL仿真预期值可能存在一些模型上的限制,这些限制可能导致仿真结果与实际的测量结果存在一定偏差。例如,在仿真模型中,可能忽略了一些器件的非线性和噪声,这些因素在实际电路中会对相位噪声产生影响。因此,需要对仿真模型进行完善和验证,并根据实际电路的特点进行模型参数的调整,以减小仿真与测量之间的差异。

3. PCB设计的影响

还有就是PCB设计方面的影响。 PCB的设计质量直接影响PLL电路的性能。 PCB设计不良会导致电路在高频下产生反射、串扰等现象,影响电路的干扰、抗干扰能力和相位噪声性能等。因此,在PLL电路的设计和调试过程中,需要对 PCB进行全面考虑和优化。

4. 环境因素的影响

最后从环境因素的角度来看,测试结果可能受到环境因素的影响。例如温度、湿度等因素会影响电器元件的性能和电路中噪声的产生。因此,需要在实验环境稳定的情况下进行测量,并对测量结果进行修正和分析,以确定真实的相位噪声性能值。

综上所述,为何测出的相位噪声性能低于ADIsimPLL仿真预期值,可能有多种原因。在实际应用中,需要结合具体情况进行综合考虑和分析,以准确评估PLL电路的相位噪声性能,确保系统的稳定、精确和可靠。

-

无线通信

+关注

关注

58文章

4635浏览量

144229 -

PCB设计

+关注

关注

394文章

4711浏览量

87024 -

相位噪声

+关注

关注

2文章

181浏览量

23019

发布评论请先 登录

相关推荐

相位噪声分析仪的技术原理和应用

LMX2582开环相位噪声和闭环相位噪声的区别是什么?

数字振荡器的相位噪声是多少

频谱仪怎么测量相位噪声

时钟抖动与相位噪声的关系

锁相环相位噪声的影响因素

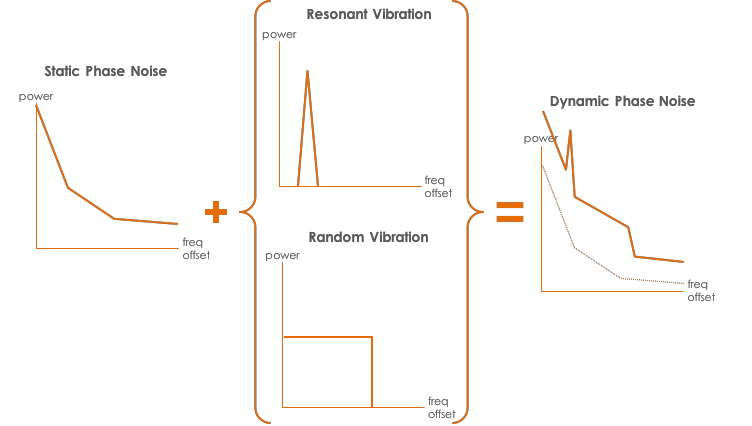

振荡器动态相位噪声优化的四步实操指南

为何测出的相位噪声性能低于ADIsimPLL仿真预期值?

为何测出的相位噪声性能低于ADIsimPLL仿真预期值?

评论