在当今快节奏的世界中,半导体设计的创新是一项永恒的需求。对更快、更准确、更创新的解决方案的需求为探索生成式人工智能(#GenerativeAI)在半导体设计开发领域的潜力铺平了道路。能做到吗?当然可以!在本系列文章中,我们将深入探讨令人兴奋的实验,展示生成式人工智能如何彻底改变半导体设计。

实例 1 - 从 FSM 图到 SV 代码

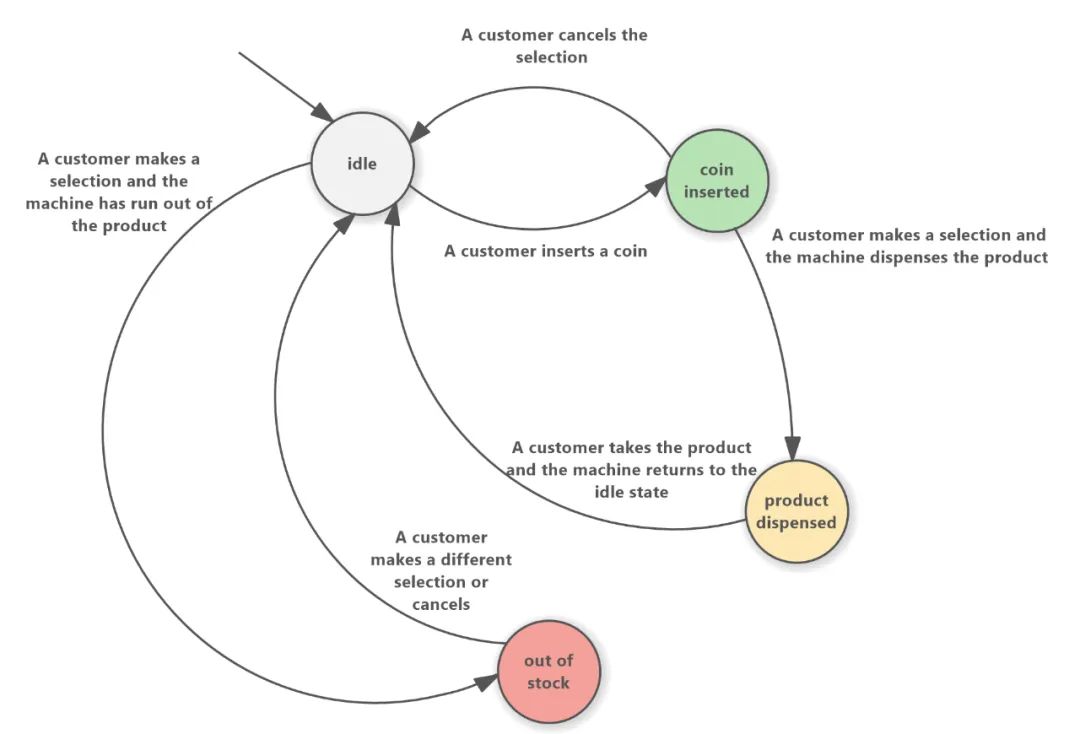

第一个实验通过将有限状态机 (FSM) 图转换为 SystemVerilog (SV) 代码,展示了生成式人工智能的非凡能力。

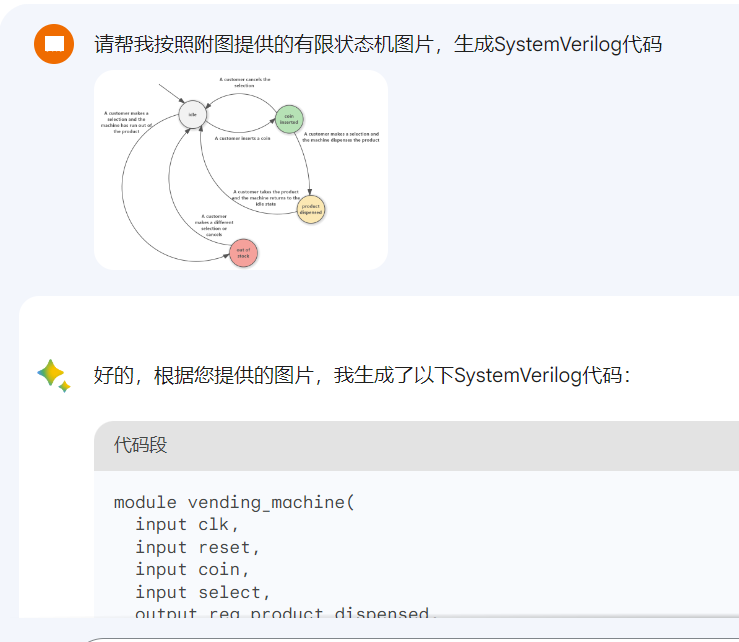

在本例中,谷歌的生成式人工智能模型--BARD 被用来生成一个自动售货机 FSM 的 SystemVerilog 实现。

状态机图片:

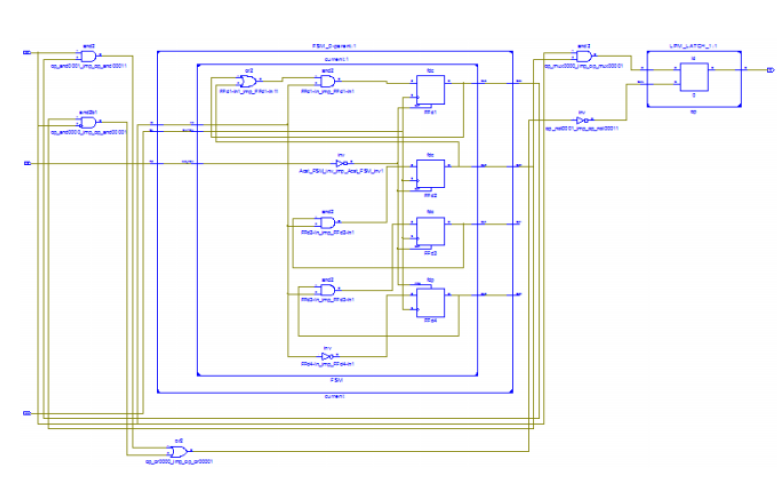

代码如下:

// Vending machine FSM // Disclaimer: This code is not tested for correctness module vending_machine ( input clk, input reset, input coin_inserted, input product_selected, input product_dispensed, output reg dispense_product, output reg return_coin ); // Define the states localparam [2:0] IDLE = 3'b000; localparam [2:0] COIN_INSERTED = 3'b001; localparam [2:0] PRODUCT_SELECTED = 3'b010; localparam [2:0] PRODUCT_DISPENSED = 3'b011; localparam [2:0] OUT_OF_STOCK = 3'b100; // Define the registers reg [2:0] current_state; // Transition logic always @(posedge clk or posedge reset) begin if (reset) begin current_state <= IDLE; end else begin case (current_state) IDLE: begin if (coin_inserted) begin current_state <= COIN_INSERTED; end else begin current_state <= IDLE; end end COIN_INSERTED: begin if (product_selected) begin current_state <= PRODUCT_SELECTED; end else begin current_state <= COIN_INSERTED; end end PRODUCT_SELECTED: begin if (product_dispensed) begin current_state <= PRODUCT_DISPENSED; end else if (out_of_stock) begin current_state <= OUT_OF_STOCK; end else begin current_state <= PRODUCT_SELECTED; end end PRODUCT_DISPENSED: begin current_state <= IDLE; end OUT_OF_STOCK: begin current_state <= IDLE; end endcase end end // Output logic always @(posedge clk) begin case (current_state) PRODUCT_DISPENSED: begin dispense_product <= 1'b1; end default: begin dispense_product <= 1'b0; end endcase end always @(posedge clk) begin case (current_state) OUT_OF_STOCK: begin return_coin <= 1'b1; end default: begin return_coin <= 1'b0; end endcase end endmodule

有限状态机在芯片设计中得到广泛应用,以下是生成式人工智能如何发挥关键作用:

提高生产力:有了生成式人工智能,创建和更新图表变得轻而易举。设计人员现在可以专注于高级概念,让人工智能来做基础工作。这不仅加快了开发过程,还能在需要更改设计时迅速进行迭代。

更高的准确性:FSM 已经成为硬件设计的标准化工具。生成式人工智能模型经过大量数据集的训练,能够熟练地将这些图表转换为准确的 SV 代码。减少了人为错误,提高了代码质量。

提高创新能力:生成式人工智能的速度和准确性为快速探索新的设计理念打开了大门。设计人员可以利用各种 FSM 图表进行头脑风暴和实验,从而推动创新。这种灵活性使每一代半导体器件都能更快地集成先进功能。 虽然生成式人工智能前景广阔,但必须谨慎行事。生成的代码不一定总是完美的。在将人工智能生成的代码部署到生产环境之前,设计人员必须对其进行审查和严格测试。彻底的验证过程对于确保最终半导体设计的可靠性和功能性至关重要。

审核编辑:汤梓红

-

半导体

+关注

关注

334文章

27320浏览量

218293 -

AI

+关注

关注

87文章

30805浏览量

268942 -

人工智能

+关注

关注

1791文章

47229浏览量

238340 -

有限状态机

+关注

关注

0文章

52浏览量

10325

原文标题:用生成式AI设计芯片,实例1:从有限状态机图片直接生成SV代码

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是有限状态机呢

有限状态机的建模与优化设计

VHDL有限状态机设计-ST

初学者对有限状态机(FSM)的设计的认识

如何使用FPGA实现序列检测有限状态机

有限状态机设计是HDL Designer Series的关键应用

基于事件驱动的有限状态机介绍

基于事件驱动的有限状态机介绍

一个基于事件驱动的有限状态机

从有限状态机图片直接生成SV代码

从有限状态机图片直接生成SV代码

评论