先贤有云,人生有三境界“看山是山,看水是水;看山不是山,看水不是水;看山还是山,看水还是水。”这三个阶段,真实反应了先贤对世事万物认知过程的突破进阶过程。而作为一名硬件开发人员,对硬件技术的认知,最近也发现有 了一定的提升。

一个面试题

先抛出来一个面试题:用100nf的电容滤除72MHz干扰时钟信号,是否合适?先思考下。

电容的等效模型

低频时,瓷片电容 就是一颗电容。

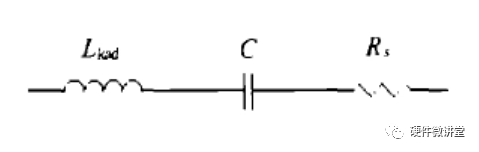

高频时,它就不仅仅一颗电容,而是电感L、电阻R、电容C的复合体。

电容频率阻抗曲线的解读

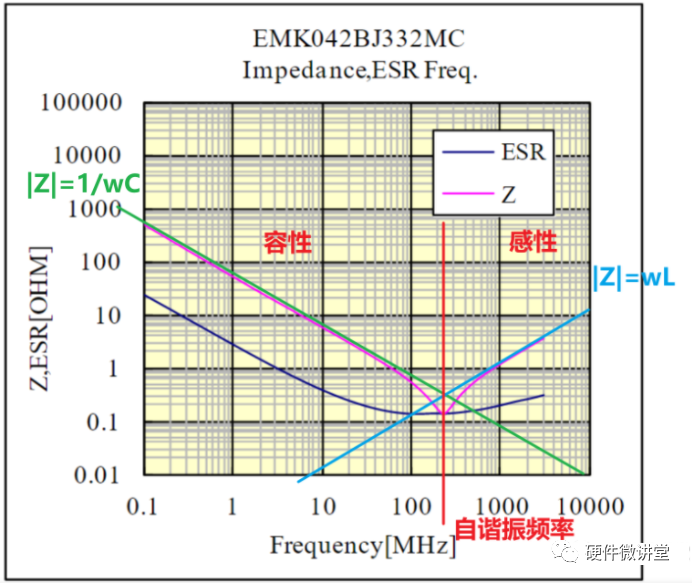

下面实际看下电容EMK042BJ332MC(Taiyo)的频率特性曲线,在曲线中分别用不同颜色标注了几种曲线。

1、深蓝色曲线为电容的ESR;

2、绿色曲线为电容(理想模型)的阻抗频率曲线;

3、天蓝色曲线为电容的ESL;

4、粉红色曲线为电容(实际模型)的阻抗频率曲线;

5、红色直线为电容的自谐振频率f0。

6、当频率f

7、在电容的理想模型下,是不存在ESR和ESL,所以|Z|=1/wC=1/2πfC;

8、在电容的实际模型下,电容相当于LCR的串联,所以ESR和ESL都要考虑,Z=R+j(wL-1/wC);

9、当电容处在谐振频率点时,电容的感抗和容抗相互抵消,此时阻抗最小,|Z|=ESR。

揭晓问题答案

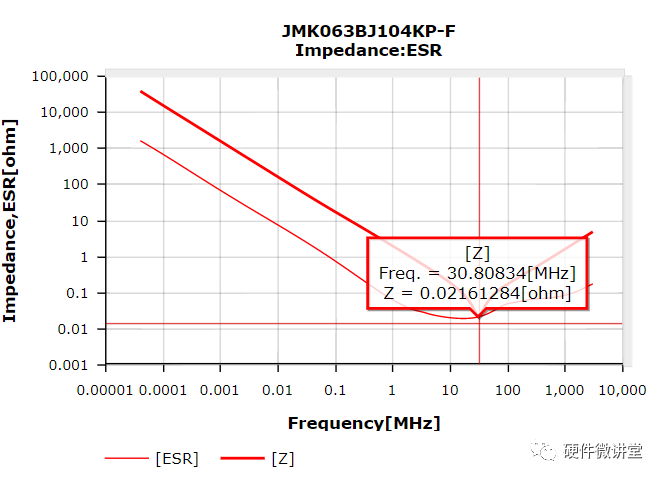

针对文章开头抛出来的面试题,结合上面的描述,我们一起看下100nf电容的阻抗频率特性曲线。下图是TaiyoJMK063BJ104KP-F(100nf),从曲线中可以看出,自谐振频率为30MHz,此时的ESR为21.6mΩ。

当时钟频率在72MHz时,此时的工作频率已远超出100nf的自谐振频率,此时已经是呈感性。原则上讲,此时的电容已经不再是电容,而是电感!这里就如同文章开头讲的:看山不是山,看水不是水。这里再用100nf做退耦,已经不合适。

那我们更深一步,用多大的电容才合适呢?

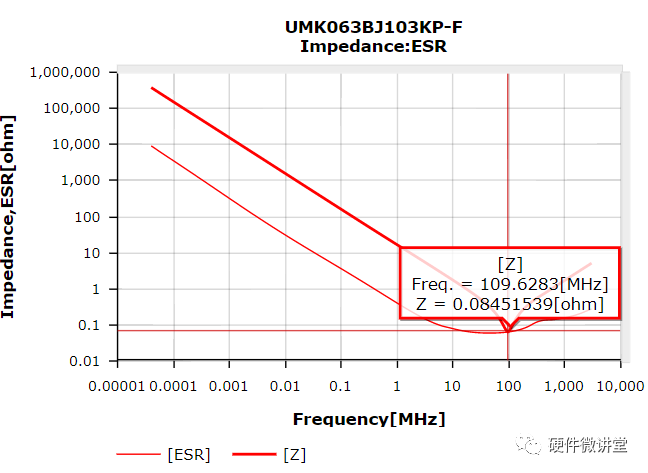

下面再看下UMK063BJ104KP-F(10nf Taiyo),从曲线中可以看出自谐振频率为109MHz,ESR=84mΩ。当工作频率为72MHz时,仍未超过自谐振频率,电容仍表现为容性,可以起到退耦作用。

所以用小于或等于10nf的电容,滤除72MHz的干扰时钟信号比较合适。

本文转载自硬件微讲堂

审核编辑:汤梓红

-

电容器

+关注

关注

64文章

6227浏览量

99735 -

电容

+关注

关注

100文章

6050浏览量

150423 -

瓷片电容

+关注

关注

0文章

76浏览量

14601 -

时钟信号

+关注

关注

4文章

449浏览量

28579 -

退耦

+关注

关注

0文章

16浏览量

8432

原文标题:用100nf电容给72Mhz时钟信号退耦合适么?

文章出处:【微信号:电子设计联盟,微信公众号:电子设计联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

HLW8012功率芯片的电压采集100nF的电容有什么用?

耦合电容与退耦电容资料分享!

STM32F103 72MHz时钟设置 精选资料分享

如何才能配置为72MHz呢

为什么不能在CubeIDE的时钟配置面板中配置72MHz时钟?

STM32F103 72MHz时钟设置

用100nf电容给72Mhz时钟信号退耦合适么?

用100nf电容给72Mhz时钟信号退耦合适么?

评论