DFT PLL向量,ATE怎么用?

自动测试设备(ATE)对PLL(锁相环)进行测试时,我们首先要明白PLL在系统级芯片(SoC)中的重要性。它是SoC中关键的时钟或信号同步部件,其性能直接影响到芯片逻辑的正确运行。在测试PLL

IP时,通常会有多个测试项目,如频率测试、相位噪声、锁定时间、稳定性、误差和漂移等。

但在SoC的ATE测试中,CP阶段通常只进行PLL频率和锁定测试。

那么DFT如何产生PLL 测试pattern,以及ATE如何根据这些pattern进行PLL测试?

DFT(Design For Test)是用于生成测试pattern以检测芯片功能和性能的技术。在生成PLL(Phase-Locked Loop)测试pattern的过程中,DFT通过使用特定的算法和测试向量来生成测试pattern。这些测试pattern旨在模拟PLL在不同条件下的行为,以确保芯片的PLL功能正常。

ATE(Automated Test Equipment)是一种用于自动测试芯片性能和功能的设备。在测试PLL时,ATE会使用由DFT生成的测试pattern来模拟芯片的输入,并监控芯片的输出以检查其功能是否正常。

这里的pattern指的是用于测试PLL的特定数据序列。这些数据序列在测试过程中被发送到芯片的输入管脚,并在芯片的输出管脚比较相应的输出数据序列。通过比较预期输出和模拟输出,ATE可以判断PLL是否正常工作。

总之,DFT通过生成测试pattern来模拟PLL的行为,ATE使用这些测试pattern来测试芯片的功能,并比较预期输出和模拟输出以判断芯片是否正常工作。

DFT 产生 PLL 向量

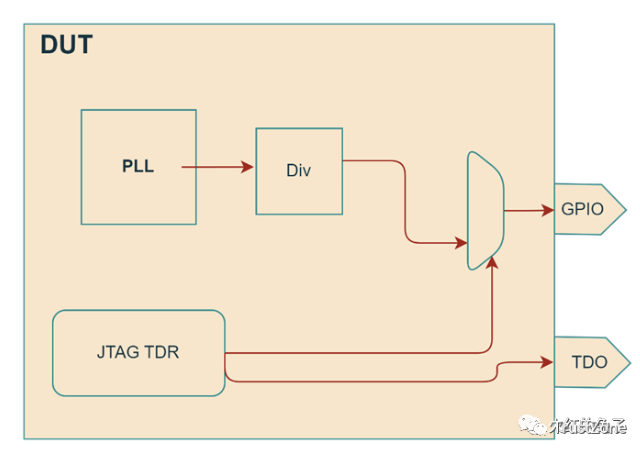

DFTer 每条PLL向量配置要求:(参考下图)

•a) JTAG配置多个PLL为对应的待测频点。

•b) 配置Div系数为最大,尽可能降低输出时钟的频率。

•c) LOCK信号在TDO串行移出观测或者复用到IO上。

•d) 切换IO复用后,PLL div 信号将会输出到对应GPIO上。

PLL输出频率的要求:10M~50M之间。 WHY?

1.上限受限于GPIO,在高于50M时,GPIO的输出特性随频率升高而减弱,最好低于50M。(机台PS1600最高1.6G采样频率,不需要考虑奈奎斯特频率的限制。)

1.下限需要考虑到不同测试方法的测试时间的影响,比如给一个32K的钟,机台需要构造更长的采样向量。

-

芯片

+关注

关注

455文章

50699浏览量

423062 -

测试

+关注

关注

8文章

5266浏览量

126594 -

IC

+关注

关注

36文章

5943浏览量

175461 -

pll

+关注

关注

6文章

776浏览量

135125 -

DFT

+关注

关注

2文章

231浏览量

22705

发布评论请先 登录

相关推荐

Nvidia is hiring-Senior DFT Engineer

什么是DFT,DFT是什么意思

DFT分步法原理分析

DFT如何产生PLL 测试pattern

DFT如何产生PLL 测试pattern

评论