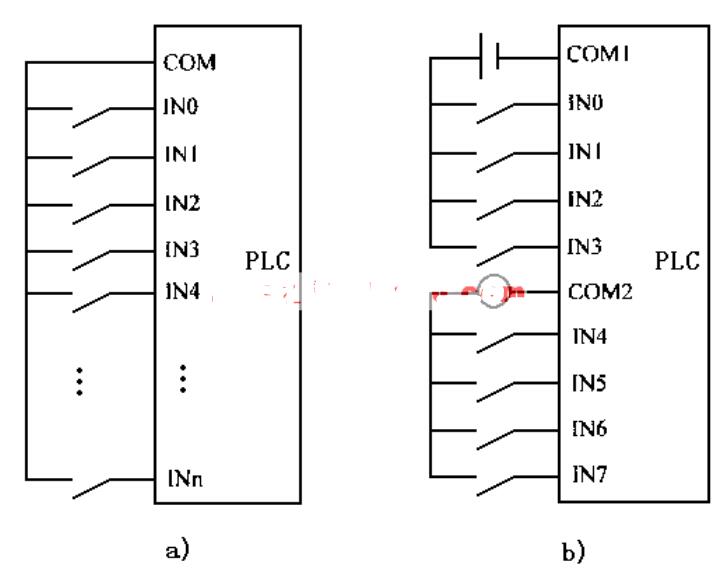

I/O电路中电压比较器

在高速I/O电路设计中,输入I/O的比较器是一个非常重要的模块。它的主要功能是将两个模拟信号进行比较,输出一个二进制值。两个输入模拟信号可以是两个互补的电压信号也可以是一个单端信号与一个参考电压。

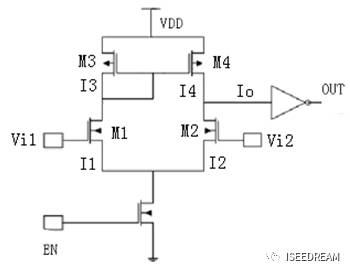

电压比较器电路如下图所示

比较器与运放的符号完全一样,结构上也有许多相似之处。开环工作下的运放本身就可以看作一个比较器。但是比较器与运放在设计上有许多不同点。运放设计时,最重要的是考虑输出与输入之间的线性传输关系及频率补偿的稳定性,因此响应时间与延迟时间往往很大,开环增益也不容易做得很大;而比较器是大信号作用,所以总是处于开环状态,不存在因为负反馈造成的自激振荡,因此频率补偿是不必要的。

在电压比较器的参数中,响应速度是其中非常重要的一个。一般要求比较器的响应速度要很快。也就是说在输入电压发生变化后,相应输出电压的变化应该很快出现。输出电压还应该有很短的上升和下降时间。另外对于高性能的电压比较器来说,还应有高的开环增益、低的失调电压、高的压摆率等。对于MOS差分放大器来说,失调过大是其固有缺点,因此减少失调也是一个关键问题。

对于高速的I/O输入电路设计中,接收器总是工作在一定的噪声环境中,虽然共模噪声能够得到很好的抑制,但差模噪声的存在总是不可避免的。如果比较器足够的快,并且噪声的幅度也足够大,如果输入恰好位于比较器的阈值点附近,则噪声就可能会造成接收器的错误翻转,使输出出现一些错误脉冲。因此当接口电路设计中用到比较器时,接收器通常会引入阈值迟滞。

阈值迟滞在接收器的设计中是一种非常重要的技术。因为当接收器的输入没有连接、连接的驱动器的驱动能力下降时,接收器就会产生不确定的输入,而阈值迟滞则可以在这种情况下确保接收器的输出是一个确定值。如下图所示,中间的方框水平方向的长度大小就是迟滞电压的大小

I/O信号完整性介绍

信号完整性(Signal Integrity,简称SI)是指互连线上信号的质量,信号完整性研究则主要是观察互连线的电气特性参数是如何影响数字信号的电压电流波形的。信号具有良好的信号完整性是指当需要的时候,信号具有所必须达到的电压电流数值。

信号完整性问题一般分成五种:

1、单一网络的信号质量,即在信号路径或返回路径上由于阻抗突变而引起的信号反射和波形失真;

2、相邻网络间的串扰,主要是由与理想回路或非理想回路耦合的电容、电感引起的干扰信号;

3、电平波动(rail collapse),即由输入输出接口电路中封装寄生电感所引起的电压波动,典型的有过冲和地弹;

4、来自系统的电磁干扰,这是因为高频信号传输会产生大量的EMI(Electromagnetic Interference)噪声,最终会导致ISI(inter-symbol interference);

5、高频信号在有损传输线上传输引起的损耗和衰减(lossy and attenuation)。

信号反射

信号的振铃(ringing)和环绕振荡(rounding)是由线上的寄生电感和电容引起的信号反射。振铃属于欠阻尼状态,而环绕振荡属于过阻尼状态。该种类型的信号完整性问题通常发生在周期信号中,如时钟等。振铃和环绕振荡是由多种因素引起的,振铃可以通过适当的端接予以减小,但是不可能完全消除。

源端与负载端阻抗不匹配会引起线上反射,负载将一部分电压反射回源端。如果负载阻抗小于源阻抗,反射电压为负;反之,如果负载阻抗大于源阻抗,反射电压为正。布线的几何形状、不正确的线端接、经过连接器的传输及电源平面的不连续等因素的变化均会导致此类反射。

在高速信号传输中由于信号的频率很高,信号的上升时间或下降时间很短。当信号线的长度足够的长,以至于信号的传播延时大于信号波形的上升时间或下降时间时,传输线效应就起作用了。此时如果传输线特征阻抗与发送器输出阻抗或者接收器输入阻抗不匹配,就会在传输线上产生信号的反射。反射会导致过冲,从而降低系统的噪声容限和引起较大的延时。

解决高频信号反射问题主要方法是在设计时,尽量使传输线特征阻抗与发送器输出阻抗或者接收器输入阻抗匹配,一般加入终端匹配电阻,该电阻要根据信号传输介质和传输长度的不同而做出相应的变化。

串扰

串扰主要是由线间的耦合电容和耦合电感引起的信号相互干扰的现象。串扰噪声就是由相邻跳变的攻击者线通过耦合电容或耦合电感对受害者线的干扰信号。由于耦合电容是导致线间信号串扰的主要因素,而且线间耦合电感很小,所以这里对电感就不作主要分析了。串扰噪声在不同外部条件下主要有两种不同的表现:逻辑毛刺和时序延迟。

当受害者线处于静态,或者其跳变窗口与攻击者线跳变窗口分离时,若噪声信号足够大,超过门限电压,将导致受害者线的逻辑状态改变,经传播并被触发器锁存后,产生功能错误。如下图所示

当攻击者线和受害者线的开关窗口重叠时,串扰效应将导致受害者线的延迟变化,如下图所示。

串扰延迟最大的问题在于该延迟具有不确定性,与攻击者线和受害者线的相对跳变方向相关。若两者跳变方向相反,则串扰延迟增大,将可能导致建立时间问题;反之,则串扰延迟减小,将可能导致保持时间问题。

显然,攻击者跳变越快或者耦合电容越大,串扰噪声就越大。驱动器越强(有更低的驱动阻抗)或者接地电容越多,串扰噪声就越小。对于长线,互连电阻也起作用,互连电阻越大,串扰噪声就越大。对于串扰延迟的不确定性,耦合电容与总的互连电容之比是一个非常重要的因素。

电平波动

接口电路中的电平波动主要是由于寄生电感的作用,某些线上的电流突变导致电源-地网络的电压波动。由于电感作用,线上电流突变将导致该线与其相邻线上的电压突变。如果这些线是片上电源-地网络的一部分,所引起的电压波动就会影响到电源和地网络。由于电感效应只对高频长线重要,自感的提取和分析主要集中于时钟线,互感效应集中于高频总线信号。

对于有电感问题的电路,一种途径是在信号层之间增加电源层。由于制造成本和功耗高,此法不再使用。对于时钟网络,信号电流回路应该使用同层并行的屏蔽电源线,减小时钟的自感,并使对其他连线的感性噪声最小。对于总线,每4到8个并行的长总线信号之间插入电源线。对于长线,增加反相器减小互感效应。Repeater插入仍然是减小电感噪声的最有效的方法之一。

在高频下,接口电路除了考虑片上寄生电感对高速信号完整性的影响外,芯片封装的电感更是不能忽略,尤其是对于wire-bond或者periphery-bumped封装类型的芯片。此时输入输出PAD和电源或地PAD都会表现出比较大的自感,其值在2nH到20nH之间,主要取决于线的长度和封装类型。在高速开关的情况下,流过电源和地的瞬态电流很大,由于自感的存在,引起电源电压的波动或者地电压的反弹---地弹(Ground-bounce)。如果要提高传输速率,减少地弹的影响,必须从如下几个方面入手:

减少输出摆幅;

不要驱动过大的片外负载;

减少同时跳变的驱动器数目;

尽可能减少寄生电感。

EMI噪声

EMI(Electromagnetic Interference)辐射主要是由电场中电荷的运动或者电场本身变化引起的。通常,任何比较陡直的电平变化,如时钟、数据、地址或者控制信号,都会在电子系统中产生电磁辐射。在数字系统中,周期性的时钟信号是产生EMI的主要源头。然而,控制信号和时序信号、地址和数据总线、互连电缆和连接器同样也会产生大量的EMI噪声。在高速串行信号传输系统中,随着数据传输速度的提高,尤其是采用源同步传输方式后,数据传输线上的电平变化很快,这时就要重视传输线产生的EMI了。要减少高速串行信号传输系统中的EMI,通常可以采用差分信号传输方式。

平衡差分线路有两个大小相等,但方向相反的电流,称为奇模态信号(odd-mode signal)。当这些奇模态信号产生的场相互耦合,彼此缠绕,它们就不能辐射出去产生危害,因此有一个平衡紧密耦合的差分传输通路有助于减少电磁干扰的辐射。差分信号同样有抗外部源干扰的能力。这些外部源比如说电动机的感应辐射,邻近传输线的串扰等。

介质损耗与衰减

当信号在长距离有损传输线上传输时,由于非电介质、辐射等原因通常信号的高频分量会衰减得很厉害,有的信号在接收端只剩下基波分量,高频分量完全衰减掉了。为了减少高频分量的衰减,通常要在PCB的设计上下功夫。但在电路设计上,也出现了一些技术,它们并不能减少信号传播过程中的高频分量的衰减,但是它们可以保证信号在经过同样的衰减后,信号仍具有较大比例的高频分量。这些技术最初应用在通信领域,如预加重技术(pre-emphasis)、均衡技术(equalization)。当然,它们应在高速信号传输领域也是非常有用的。

-

驱动器

+关注

关注

53文章

8263浏览量

146681 -

差分放大器

+关注

关注

8文章

450浏览量

52228 -

信号完整性

+关注

关注

68文章

1412浏览量

95546 -

电磁干扰

+关注

关注

36文章

2323浏览量

105527 -

电压比较器

+关注

关注

18文章

218浏览量

37614

发布评论请先 登录

相关推荐

PCB电路中的电源完整性设计

基于Rocket I/O模块的高速I/O设计

基于SmartRail的I/O的介绍

高速串行总线的信号完整性验证

Linux中如何使用信号驱动式I/O?

I/O电路中电压比较器与I/O信号完整性介绍

I/O电路中电压比较器与I/O信号完整性介绍

评论