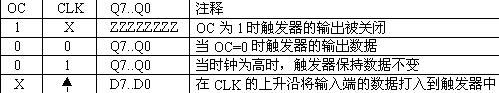

寄存器分为锁存器、触发器;是数字和模拟电路中的核心之一。为了便于快速理解,在这里我们只以D锁存器和D触发器的功能来介绍寄存器的工作原理。一般性的定义可在百度百科搜索关键词:寄存器。

下面我们将介绍具体地介绍 存储单元,传输门结构锁存器,逻辑门结构锁存器,差分信号锁存器;通过锁存器实现寄存器。

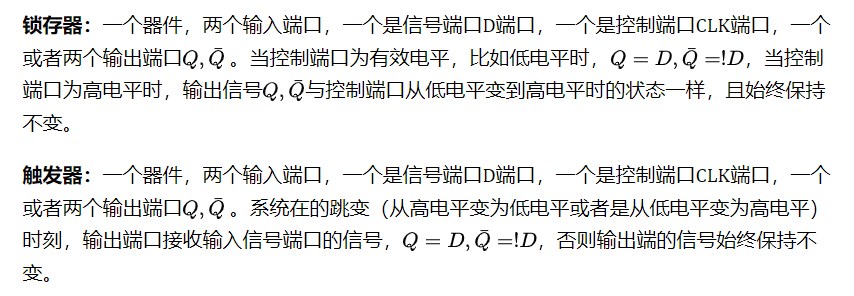

存储单元

在具体介绍寄存器原理图之前,我们先来看一个存储信息的单元。这里我们提到的存储单元是构建一条回路来存储信息,使得信号的信息始终保持在单元内,即这个储存单元内储存了一个高电平信号或者是低电平信号。

存储单元

这个电路,我们可以这样来理解,如果一开始我们在电路的左端输入一个高电平,那么通过反相器,右边的电路是低电平信号,然后右边的低电平信号通过下面的反相器在返回左端电路,信号又变成了高电平信号,电路稳定后,我们撤去外加的初始电平,我们会发现电路会稳定。稳定的原因如下:

1.电路中两个反相器都是接有电源的,撤去外加信号后电路还是有稳定供电,通过反相器后输出电信号的电源来源于反相器上面接的电源。

2.每个反相器内部都是两个MOS管,我们知道MOS管内部是有寄生电容的,在电压传输的过程中,由于寄生电容的存在,电压的变化以充放电的形式出现,电压是连续变化的,因此经过一个反相器都需要一定的时间,当然这个时间很短,不然就没有当今我们这么快速便捷的计算机了。虽然时间很短,但是也起到了一个缓冲的作用,由此这个电路我们可以理解成一条跑道,电信号在里面循环往复地跑圈。由此实现了电信号的存储,我们用的计算机和手机中的RAM用的就是这类存储单元。

传输门结构锁存器

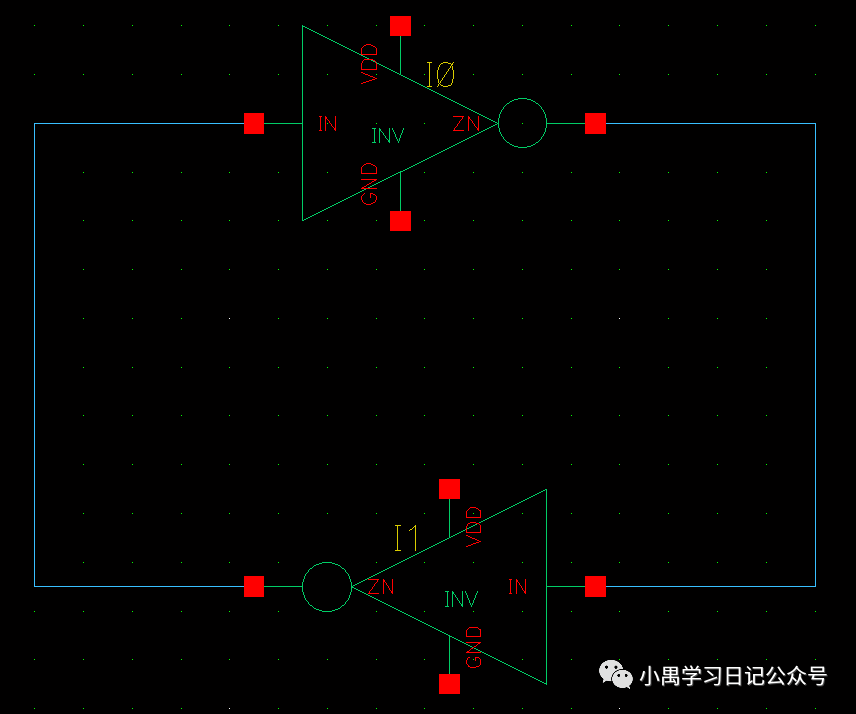

要实现D锁存器和D触发器的功能,我们首先要来分析实现这些功能所需要的电路逻辑。

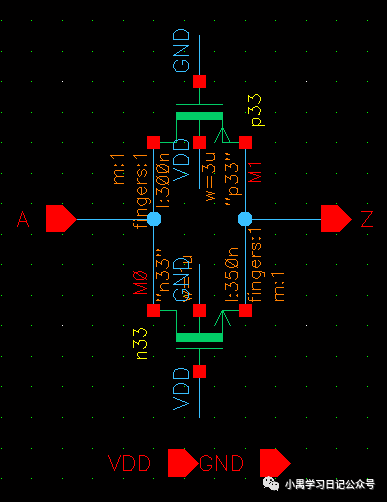

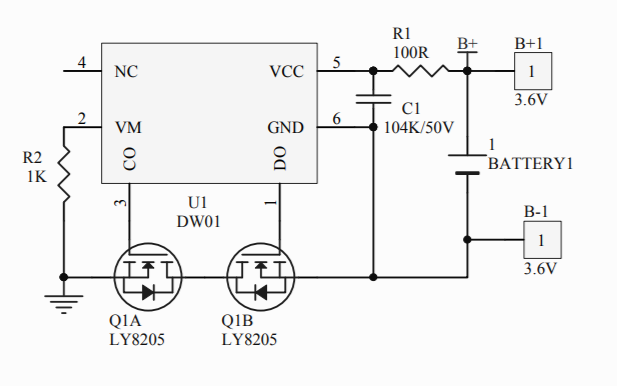

传输门正好就是这样一个开关,其内部是由两个MOS管组成,结构如下:

GND端连接低电平、VDD端连接高电平时,传输门开关导通

传输门:CLK高电平导通,低电平关闭

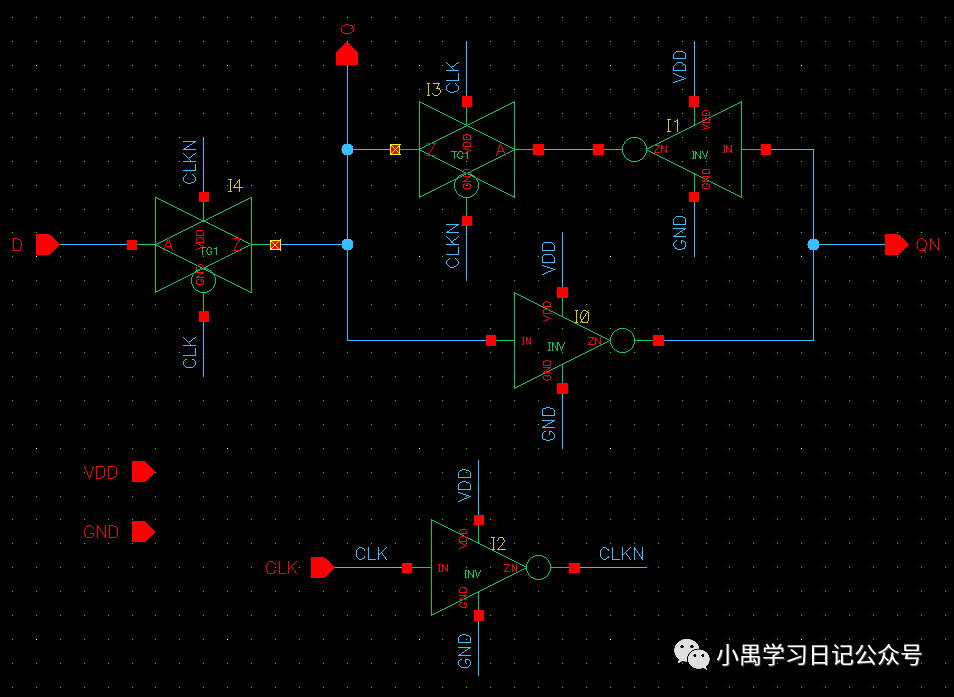

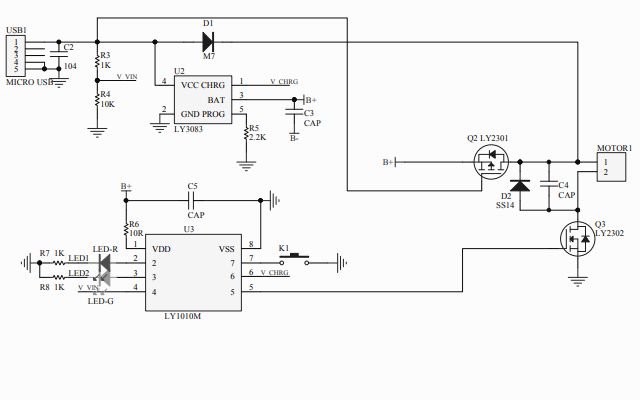

考虑到不让CLK在低电平输入信号时,传输门内电路的左端电压有冲突,我们还在存储单元中加入了一个传输门做开关控制,当CLK低电平时,输入端传输门打开,存储单元中的传输门关闭,输出等于输入。当CLK高电平时,输入端传输门关闭,存储单元中的传输门打开,信号保持不变;由此构成了一个D锁存器结构。

传输门结构D锁存器

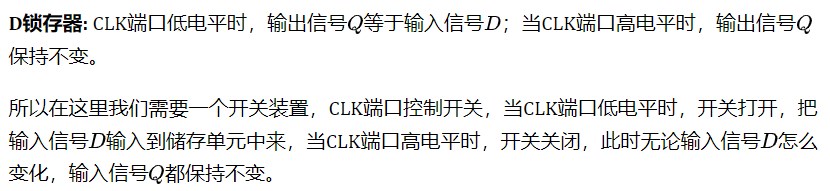

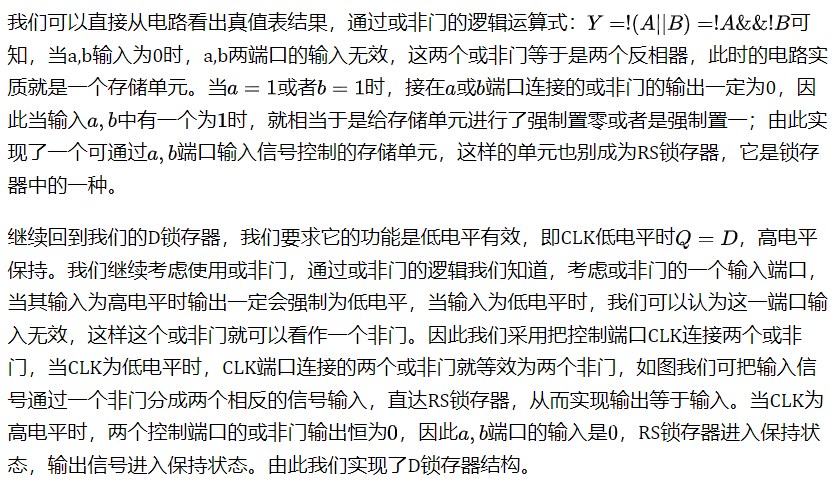

逻辑门结构锁存器

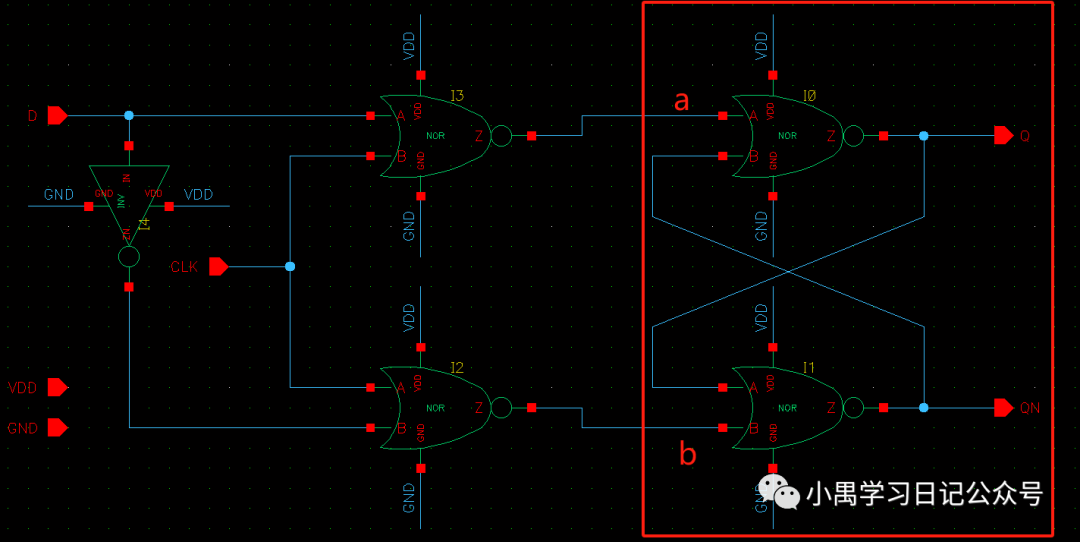

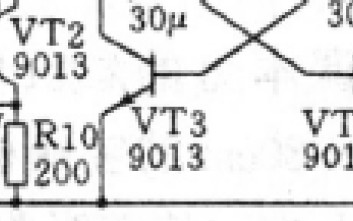

通过或非门搭建的锁存器

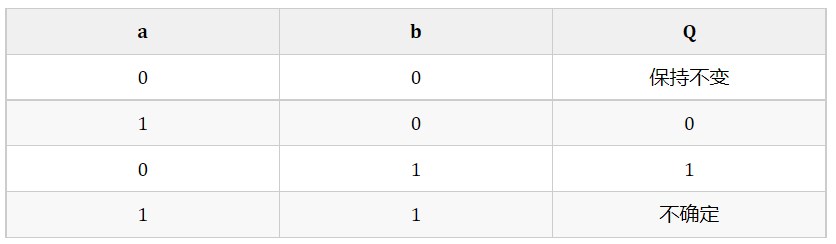

这个电路原理图,我们首先来看右边红色框框住的两个或非门组成的电路结构,这样的结构是一个可输入信号的存储单元,也被称为RS锁存器。通过逻辑运算可见,红色框电路的真值表为:

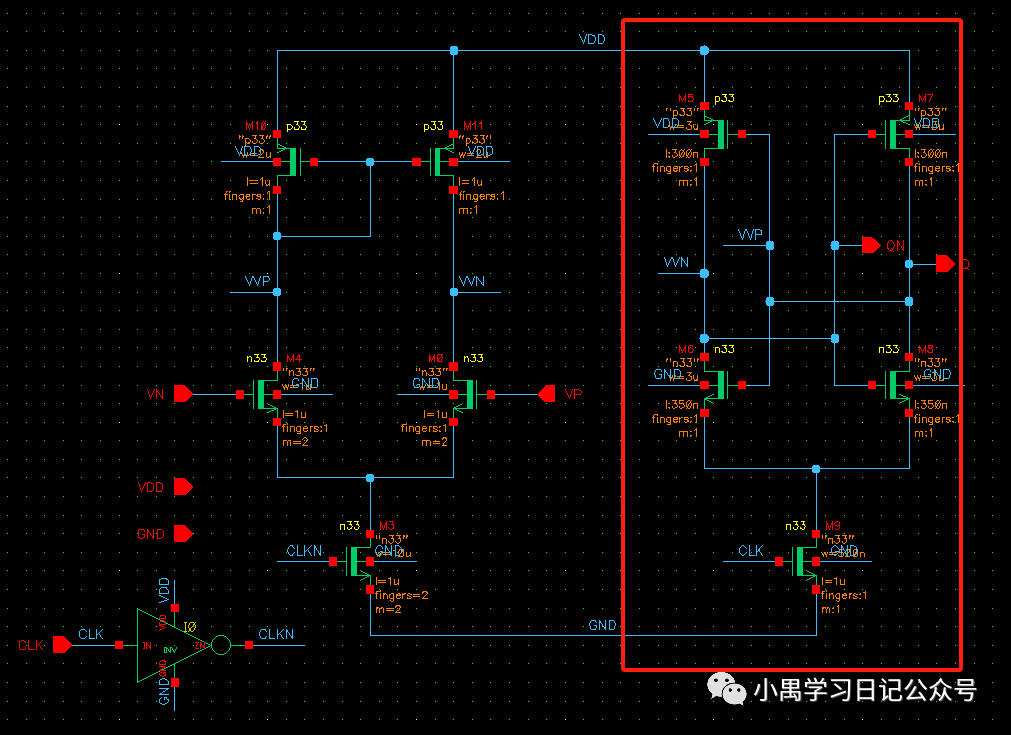

差分信号锁存器

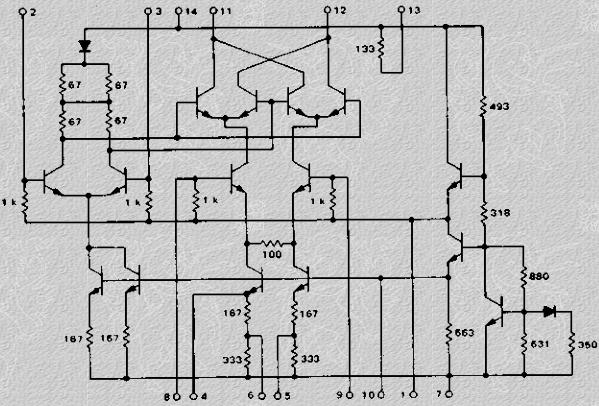

差分信号锁存器

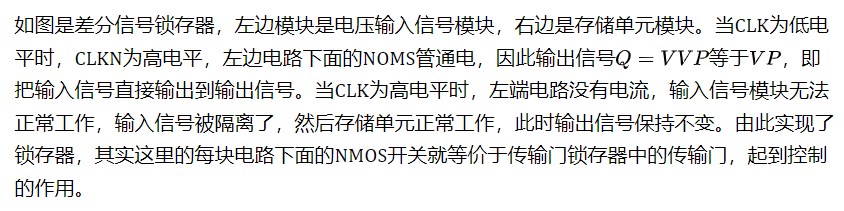

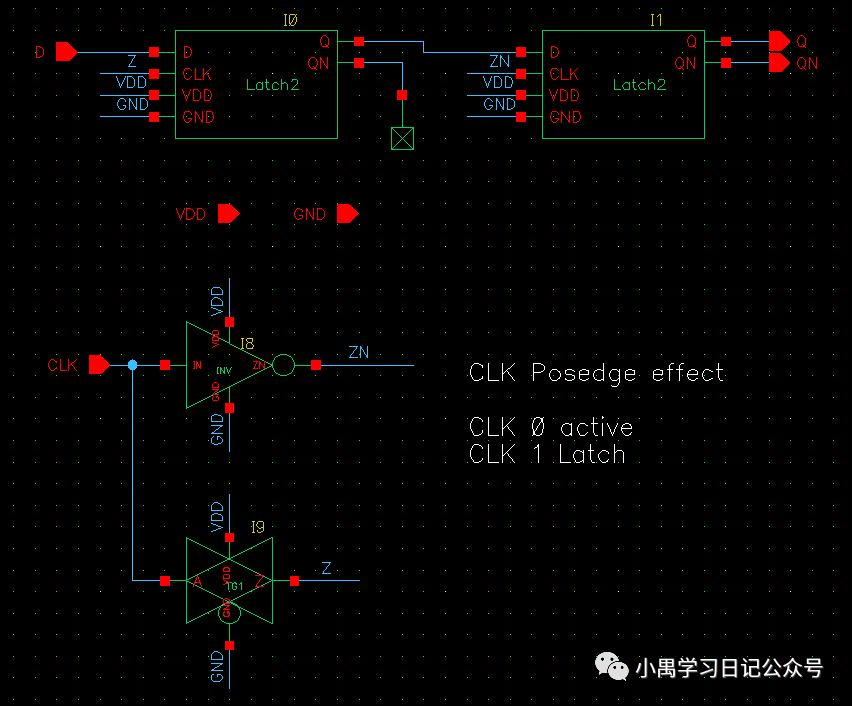

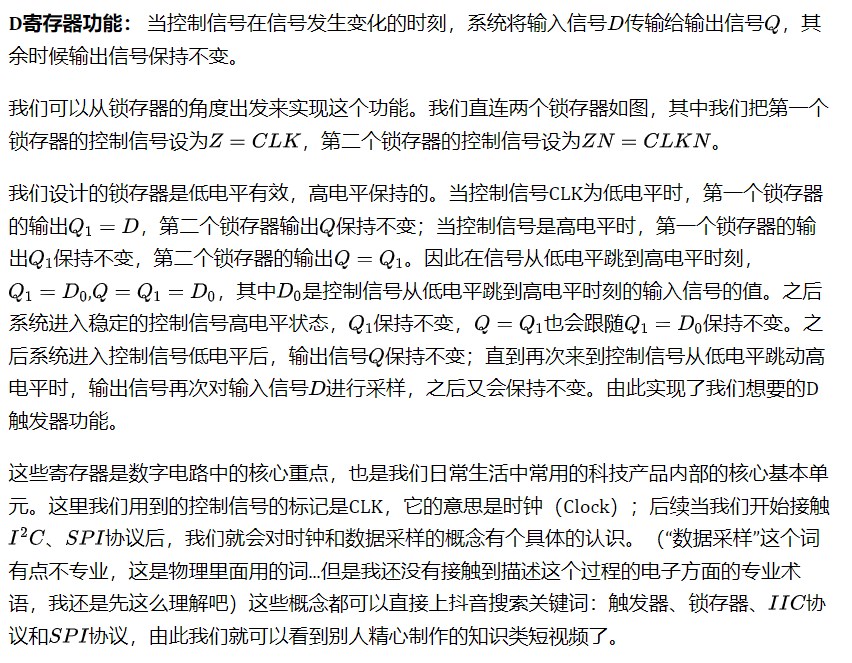

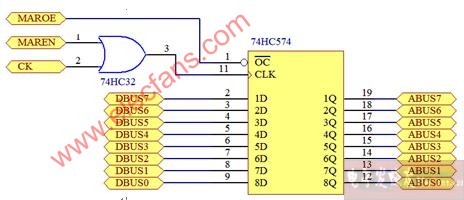

通过锁存器实现寄存器

上升沿有效D触发器

-

寄存器

+关注

关注

31文章

5622浏览量

130574 -

IC设计

+关注

关注

38文章

1406浏览量

108476 -

锁存器

+关注

关注

8文章

958浏览量

45525 -

触发器

+关注

关注

14文章

2065浏览量

63612 -

CLK

+关注

关注

0文章

132浏览量

18115

发布评论请先 登录

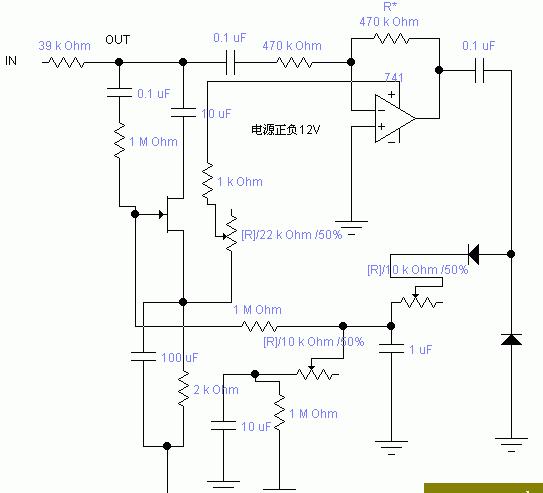

电子秤电路电气原理图

完整的电路原理图设计

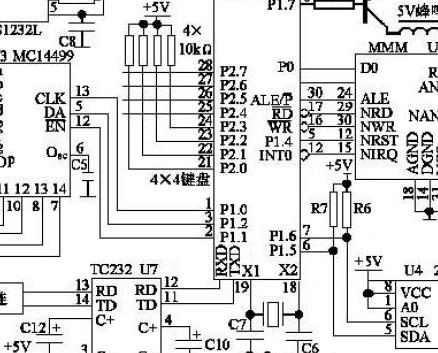

74HC574应用电路原理图 (用作寄存器)

ST堆栈寄存器原理图

模拟IC设计原理图2:寄存器的原理和电路原理图介绍

模拟IC设计原理图2:寄存器的原理和电路原理图介绍

评论