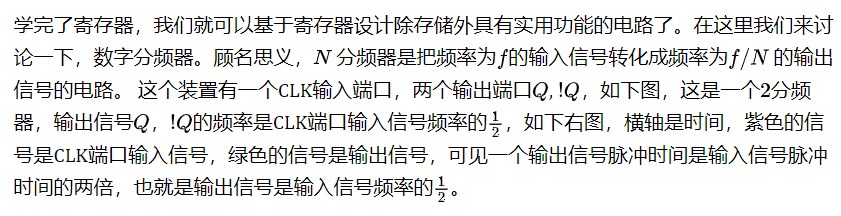

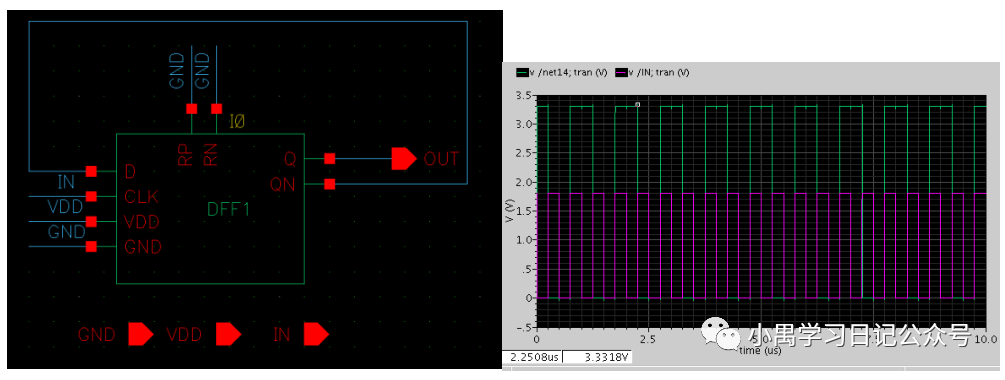

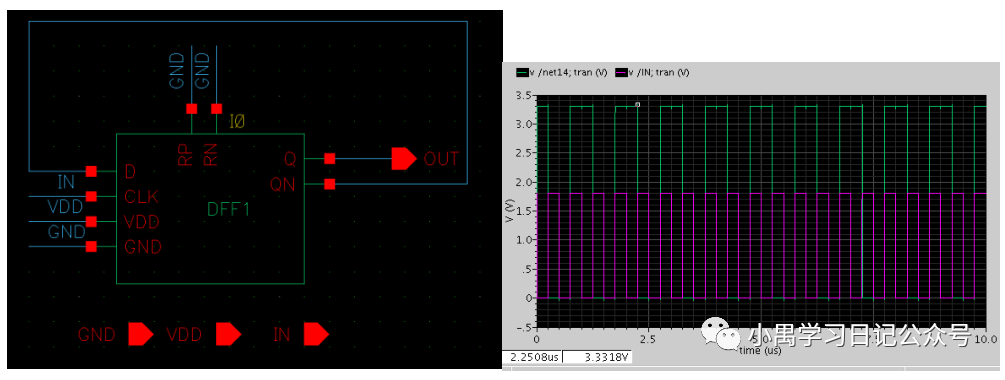

2分频器电路图,其中DFF1是D Flip Flop,即D触发器;右边是输入输出信号图

由于这篇文章有一定的技术含量,大家不一定能一口气全读完。因此先讨论本来写在结尾的闲谈。关于分频器,就我目前的接触主要是在时钟综合器、锁相环等时钟相关的模块中看到分频器,在FPGA等数字IC或者RFIC中也有用到分频器。

为了了解分频器的重要性,我们来看一个实例,石英晶振,通过这个例子,我们还能知道时钟信号为什么被称为时钟信号了。

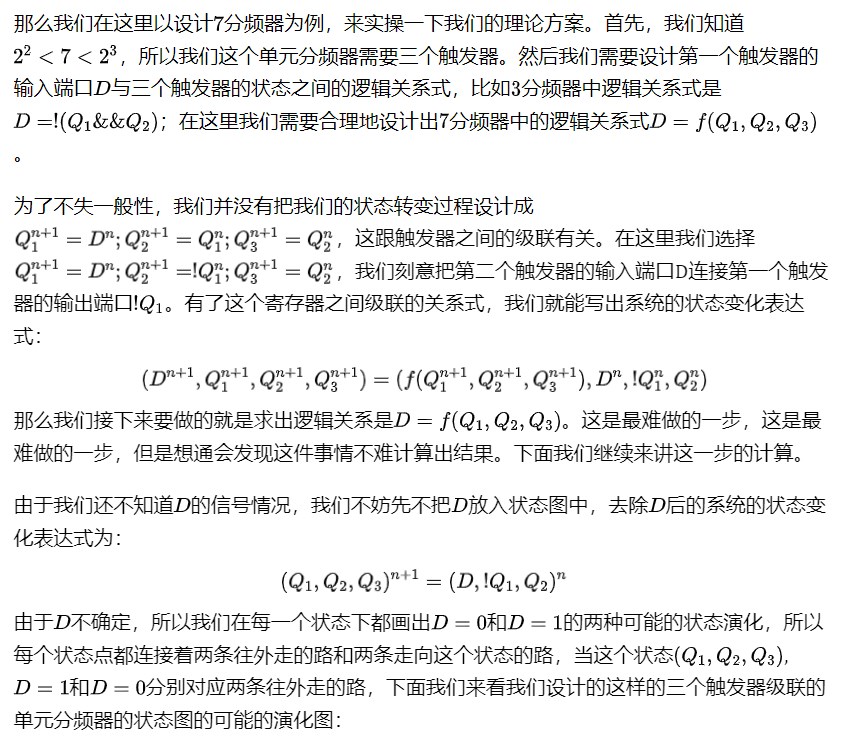

石英晶振是一种基于压电效应的振荡器,压电也就是说施加在石英上的压力会转化成电压,电压会转化成对石英的压力。

通过这个特性,我们石英晶振接在一个反向放大电路后,石英晶振就会产生振荡信号(关于震荡信号的产生,我们会在之后的振荡器章节再进行系统地讨论)。

(专业人士可能会想了解分数分频器,不过分数分频器一般是通过FPGA来实现,它是通过Verilog代码综合出电路;在这里我们由于当前还没学会Verilog综合,因此没有实际可供参考的模拟分数分频器电路来做研究,因此没法通过模拟IC的方法直接搭建分数分频器。)

2分频器电路图,其中DFF1是D Flip Flop,即D触发器;右边是输入输出信号图

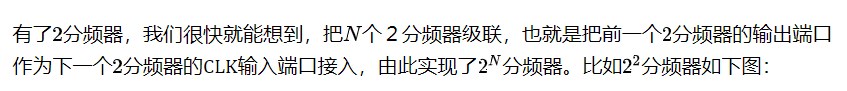

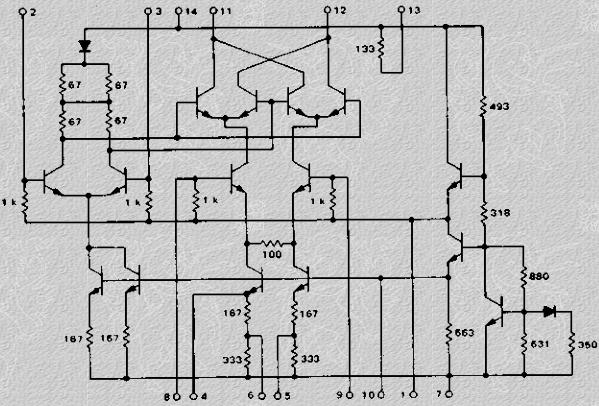

分频器的原理图与输入输出信号对比图

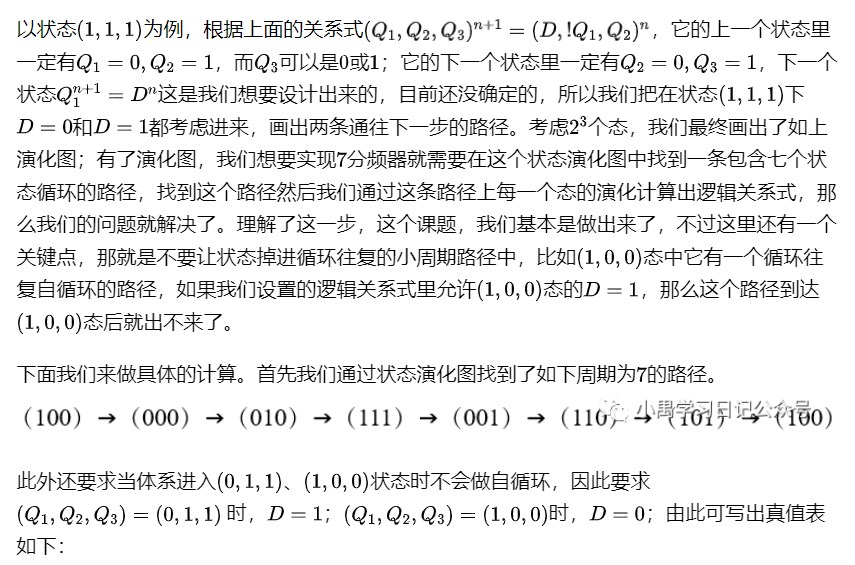

3. 任意整数N分频器的构建

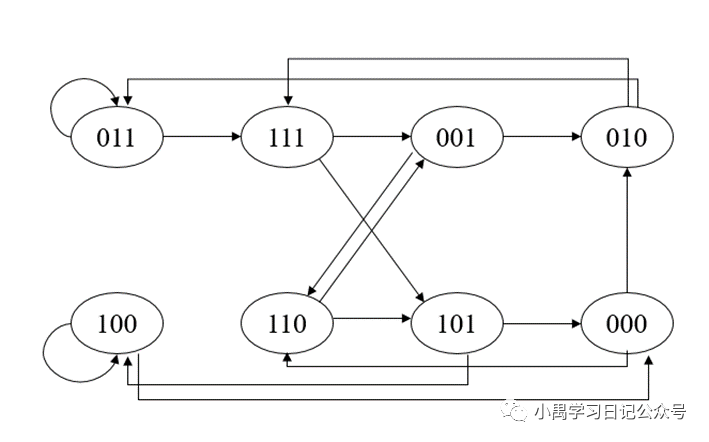

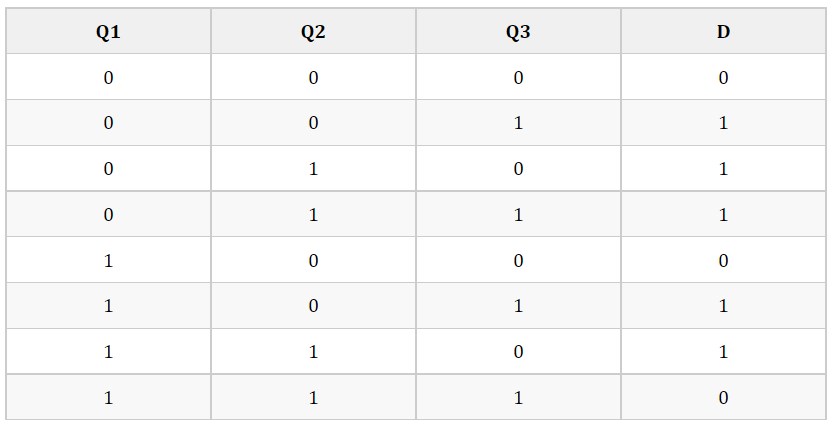

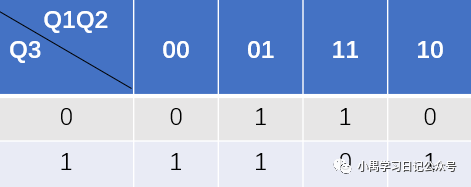

有了真值表,我们就能得到卡诺图如下:

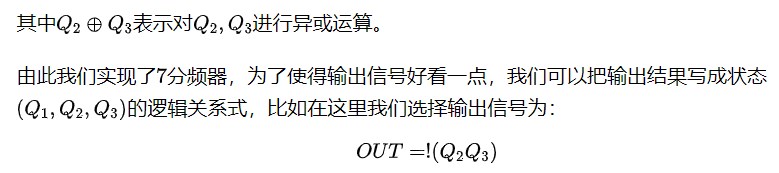

进一步计算出逻辑关系式:

或者可以省去与符号写成:

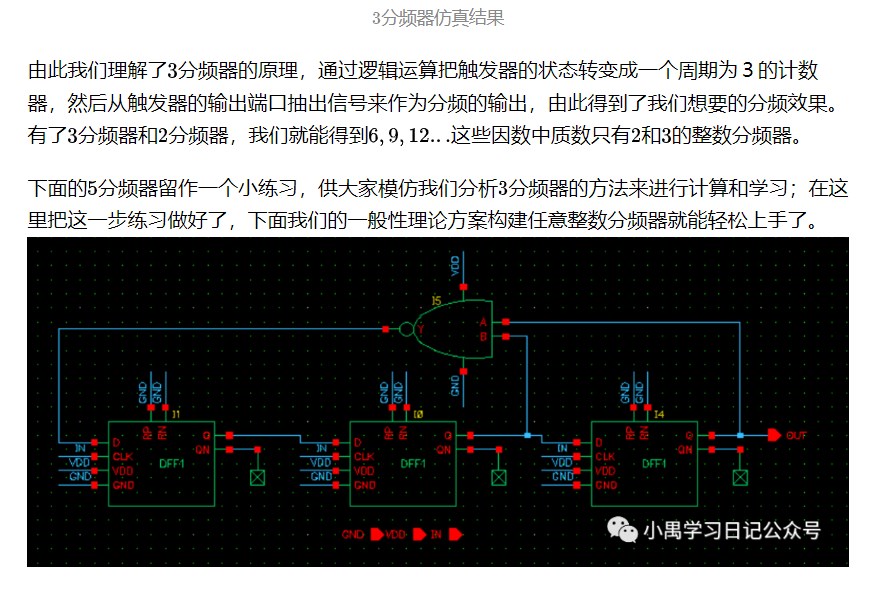

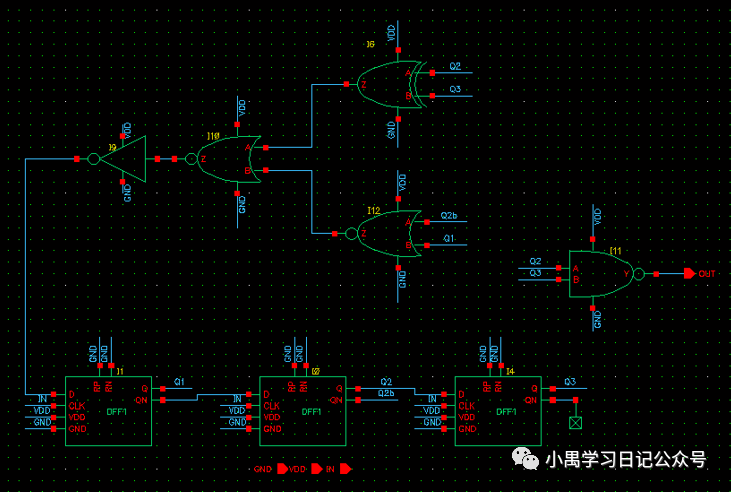

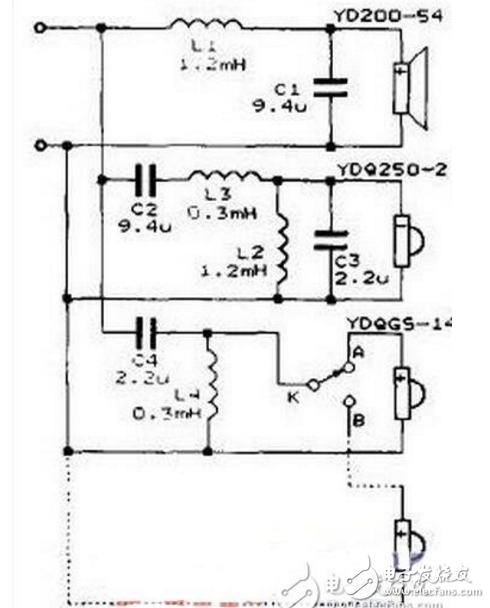

原理图如下:

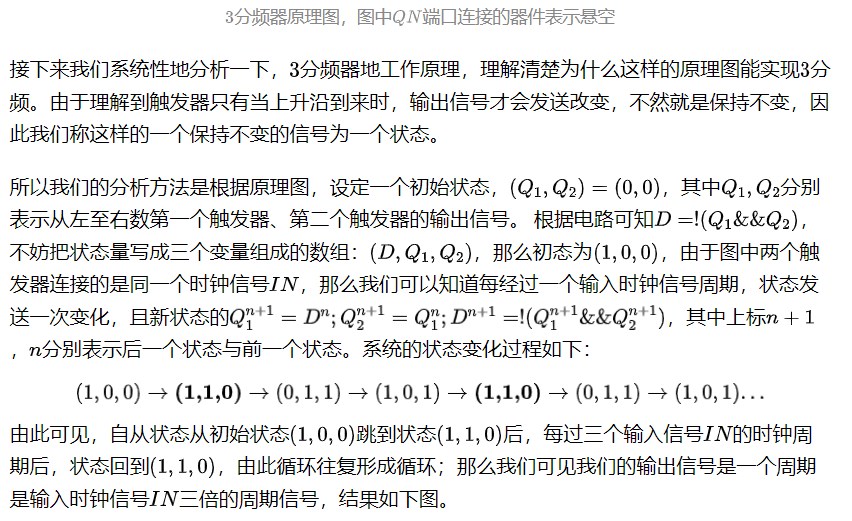

分频器原理图

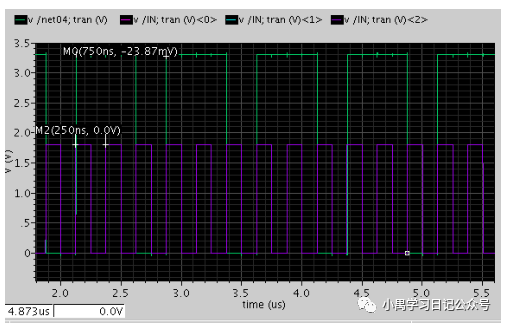

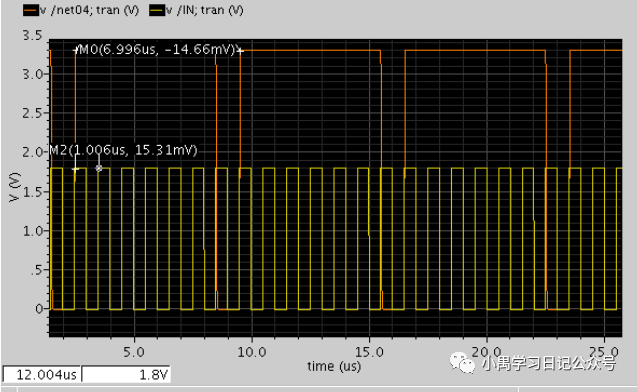

分频器仿真结果

-

锁相环

+关注

关注

35文章

589浏览量

87826 -

IC设计

+关注

关注

38文章

1298浏览量

104123 -

分频器

+关注

关注

43文章

447浏览量

50002 -

触发器

+关注

关注

14文章

2000浏览量

61252 -

状态机

+关注

关注

2文章

492浏览量

27590

发布评论请先 登录

相关推荐

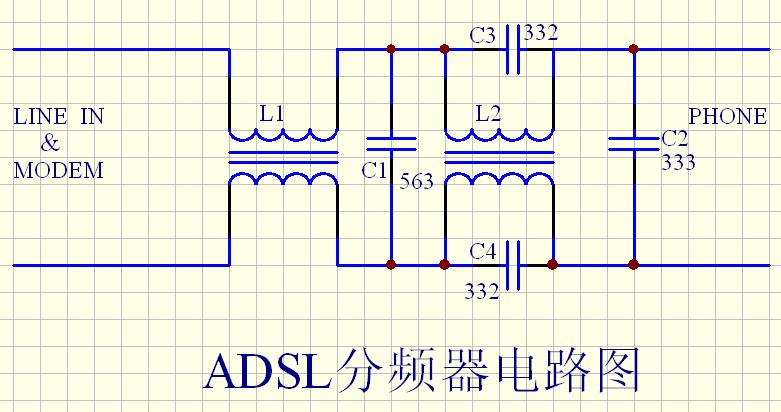

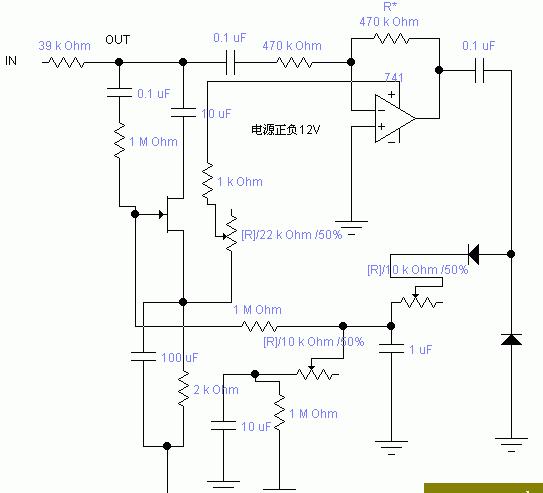

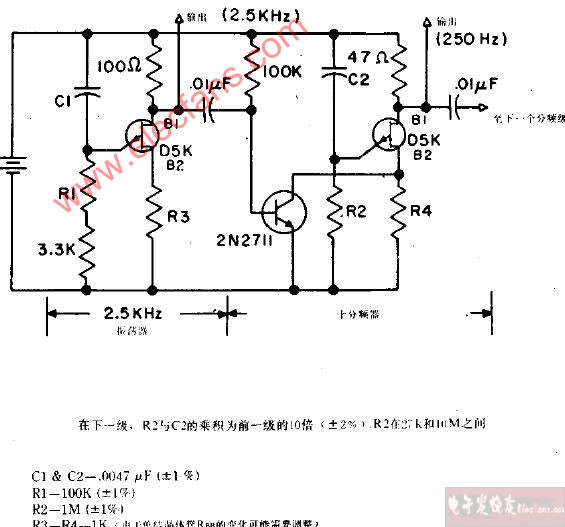

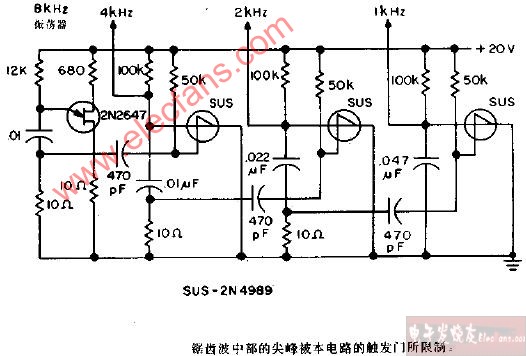

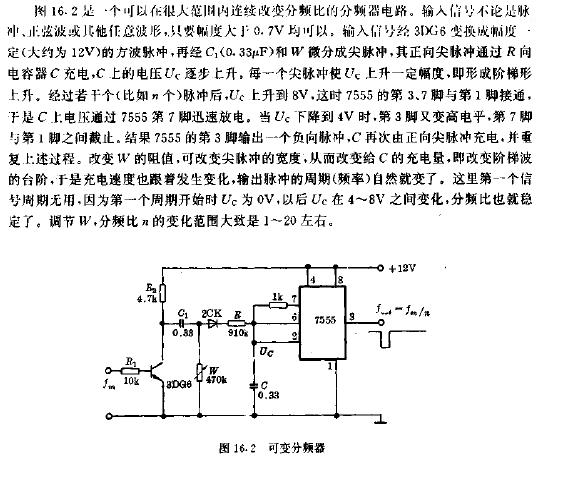

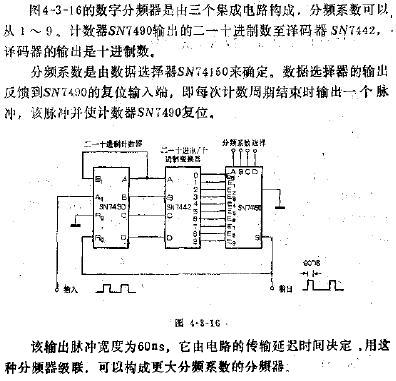

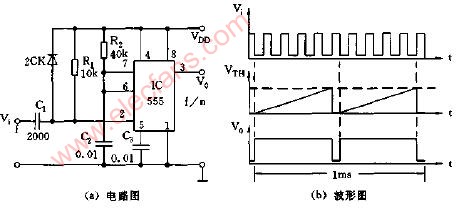

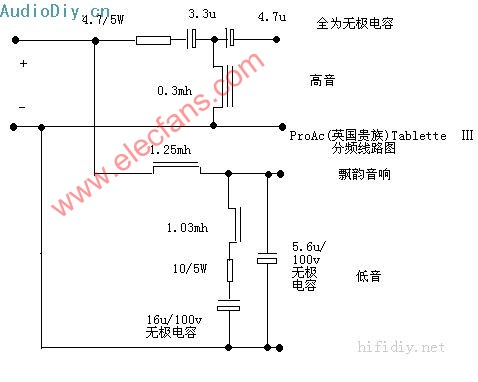

电子分频器电路图大全(六款电子分频器电路设计原理图详解)

分频器的作用是什么 半整数分频器原理图分析

模拟IC设计原理图3:数字分频器的原理和电路原理图

模拟IC设计原理图3:数字分频器的原理和电路原理图

评论