5.1.指令的本质

虽然把“总线”比喻成“高速公路”,但是两者之间还是有很大的不同,在现实的高速公路上,汽车向着同一个方向前进,每个汽车有不同的目的地,在不同的路口下高速。但是在电路中,电子的传输速度是光速,信号会同时出现在所有的路口,也就是说不可能要求“总线”中的信号去哪个路口,不去哪个路口。

所以我们控制信号的手段是当数据信号在总线中的时候,可以通过控制哪些元件从“总线”中读取信号或者控制哪些元件往总线中写入数据的方式来达到控制整个电路运行的目的。

那么具体到电路中,应该如何实现控制信号进出总线呢?从第四章我们知道,存储器(寄存器、内存)有两个读、写两个控制开关。让我们好像找到了的“命门”,只要控制好这些读、写开关,当某个寄存器设置为读,数据从寄存器传导到总线,当某个寄存器设置为写,实现把数据从总线读入寄存器,如此就能控制好整个电路,让它做我们想做的事情。

为了更加清楚的说明整个控制过程,我们再看看从内存中读取数据相加的控制过程,具体计算步骤实现如下(表 5-1):

表 5-1 相加电路的实现步骤

| 步骤序号 | 步骤描述 | 设置 |

|---|---|---|

| 1 | 读被加数 | 内存(M)的R=1;暂存寄存器(TR1)的W=1;其余开关=0 |

| 2 | 读加数和相加一起 | 内存(M)的R=1;暂存寄存器(TR1)的R=1;暂存寄存器(TR2)的W=1;其余开关=0 |

| 3 | 保存结果 | 内存(M)的W=1;暂存寄存器(TR2)的R=1;其余开关=0 |

表中的每一行就是一个指令,指令是计算机程序发给计算机处理器的命令。每一个指令,我们通过完成几个寄存器的读写设置,完成一个具有一定功能的动作组合。

5.2.指令寄存器

为了保存当前需要运行的指令,设置指令寄存器组,由指令操作码和地址寄存器两个8位寄存器组成。指令操作码寄存器存放的指令的编号,通过指令译码器选择执行的动作;地址寄存器指的是该指令执行过程中需要的内存地址。

图 5-1 指令格式

表 5-2 电路支持的指令列表

| 操作码 | 说明 |

|---|---|

| 0000 0000 | 读取被加数 |

| 0000 0001 | 读取加数,并相加 |

| 0000 0010 | 将相加的结果存储内存 |

| 0000 0100 | 在常量寄存器中存入一个常量 |

| 0000 0101 | 把常量寄存器的数存到内存中 |

5.3.指令译码器

为了使得控制更加简单,可以把每一个步骤(指令)设置一个开关,一键完成一个步骤。

进一步,可以在错误!未找到引用源。基础上添加译码器,实现指令控制的电路。指令译码器的实现还是通过逻辑真值表来辅助设计。

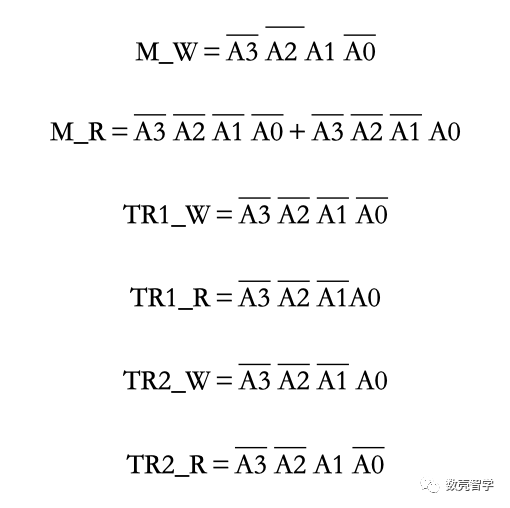

每个指令的操作码对应多个寄存器的设置操作。比如从内存中读取是指,并且把值放入加法的加数暂存器TR1中的指令,指令操作码是 0000,需要将内存的R端口和加数暂存起TR1的W端口设置为1;执行加法的指令,指令操作码是0001,需要同时设置M寄存器的R=1,暂存器TR1的R=1,暂存器TR2的W=1。根据(表 5-1),重新建立操作码和寄存器设置的真值表如下表:

表 5-3 指令操作码和设置动作的真值表

| 指令操作码A3A2A1A0 | 指令描述 | 内存M | 加数暂存器TR1 | 和暂存器TR2 |

|---|---|---|---|---|

| W | R | W | R | W |

| 0 0 0 0 | 读被加数 | 1 | 1 | |

| 0 0 0 1 | 读加数,相加 | 1 | ||

| 0 0 1 0 | 存结果 | 1 |

逻辑表达式:

逻辑电路:

图 5-2指令译码器电路图

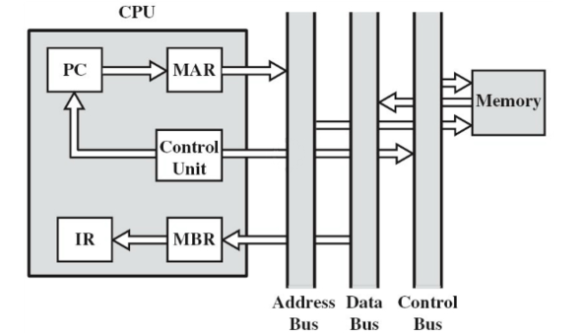

5.4.内存相加电路实现

图 5-3 基于内存的加法功能电路

图 5-4 简单内存示意图

完成本章的内存相加功能,假设如图 5-4 a、b、c的内存地址,读取a、b的值,把相加的结果保存到c,完整指令步骤如下:

5.5.小节

本章提出一个如何将内存中的两个数字相加的功能的问题,绘制以内存和加法器为主体的功能电路,同时,为了电路图的布局更加的合理,引入“数据总线”、“地址总线”、“控制总线”的概念。

详细的阐述指令的本质控制电路完成特定功能,解构指令译码器的内部解构,并提出增加指令寄存器,最后给出了较为完整的内存数据相加的逻辑电路。

但是本章对于指令寄存器的指令的加载和按顺序执行指令的过程没有阐述,下一章将重点解决这个问题。

-

寄存器

+关注

关注

31文章

5328浏览量

120113 -

内存

+关注

关注

8文章

3008浏览量

73918 -

指令

+关注

关注

1文章

607浏览量

35665 -

译码器

+关注

关注

4文章

310浏览量

50291

发布评论请先 登录

相关推荐

一条指令的执行需要多少个时钟周期

MOVX指令的执行过程

ARM与X862.ARM中指令的执行

浅谈51单片机指令执行的过程

单片机MOVX指令执行时序深入分析

[STM32]STM32F407系列教程之三,c语言知识点巩固 指令执行过程

![[STM32]STM32F407系列教程之三,c语言知识点巩固 <b class='flag-5'>指令</b><b class='flag-5'>执行</b>过程](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

指令如何执行

指令如何执行

评论