相位噪声和抖动是对时钟频谱纯度的两种表述形式,一个是频域一个是时域,从原理上来说,它们是等效的。

工程中以PLL为例,往往需要对PLL进行噪声建模,建模的目的是根据各模块的电压、电流、相位噪声及各模块(PFD、CP、LPF、VCO、PREDIV、FBDIV)到输出的传函得到时钟上的RJ抖动。

这里就涉及到电压、电流、相位噪声如何转换成时域抖动,电压、电流噪声到抖动的转换相对简单,本篇重点介绍相位噪声(如VCO、DIV)到抖动的转换。

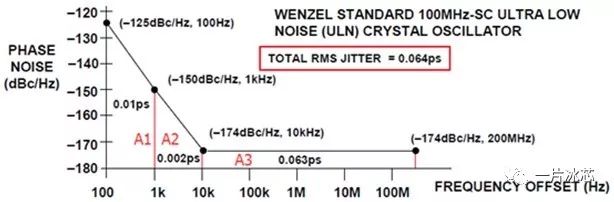

相位噪声转换到抖动的基本思想就是对相位噪声曲线进行积分。参考文献给出了相位噪声与抖动之间的转换关系如图1所示,其中A1~A4代表图形面积(可通过积分算出),fo为中心频率。

Fig1.Calculating Jitter from Phase Noise

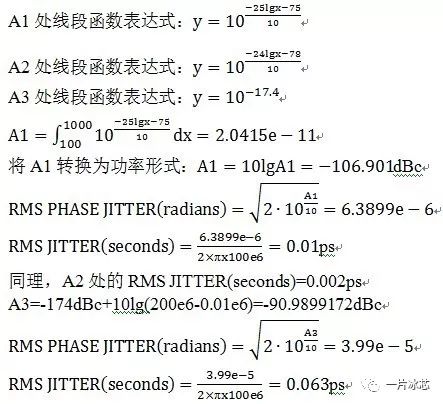

图1给出了计算抖动的公式,图2为参考文献中给出的A1~A3 RMS JITTER计算结果,下面给出具体计算方法。

Fig2. Jitter Calculationfor Low Noise 100-MHz Crystal Oscillator

A1在对数坐标下(100,-125)和(1000,-150)两点之间的斜率恒定,计算面积时用对数坐标是不合理的,因此转换后A1~A3处的函数表达式如下:

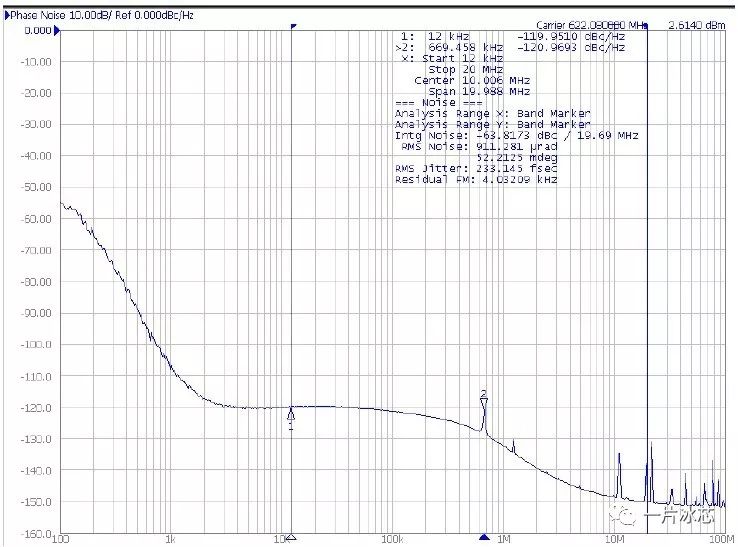

上述红色字体与图3计算结果一致!

-

时钟抖动

+关注

关注

1文章

61浏览量

15917 -

RMS

+关注

关注

2文章

137浏览量

35745 -

相位噪声

+关注

关注

2文章

180浏览量

22834 -

PFD

+关注

关注

0文章

11浏览量

14397 -

PLL技术

+关注

关注

0文章

10浏览量

3668

发布评论请先 登录

相关推荐

怎样将相位噪声和抖动降至最低及其估算方法

相位噪声的RMS抖动

怎么将相位噪声转换为抖动?

时钟抖动(CLK)和相位噪声之间的转换

相位噪声到抖动的转换(上)

相位噪声到抖动的转换(上)

评论