单重中断与多重中断

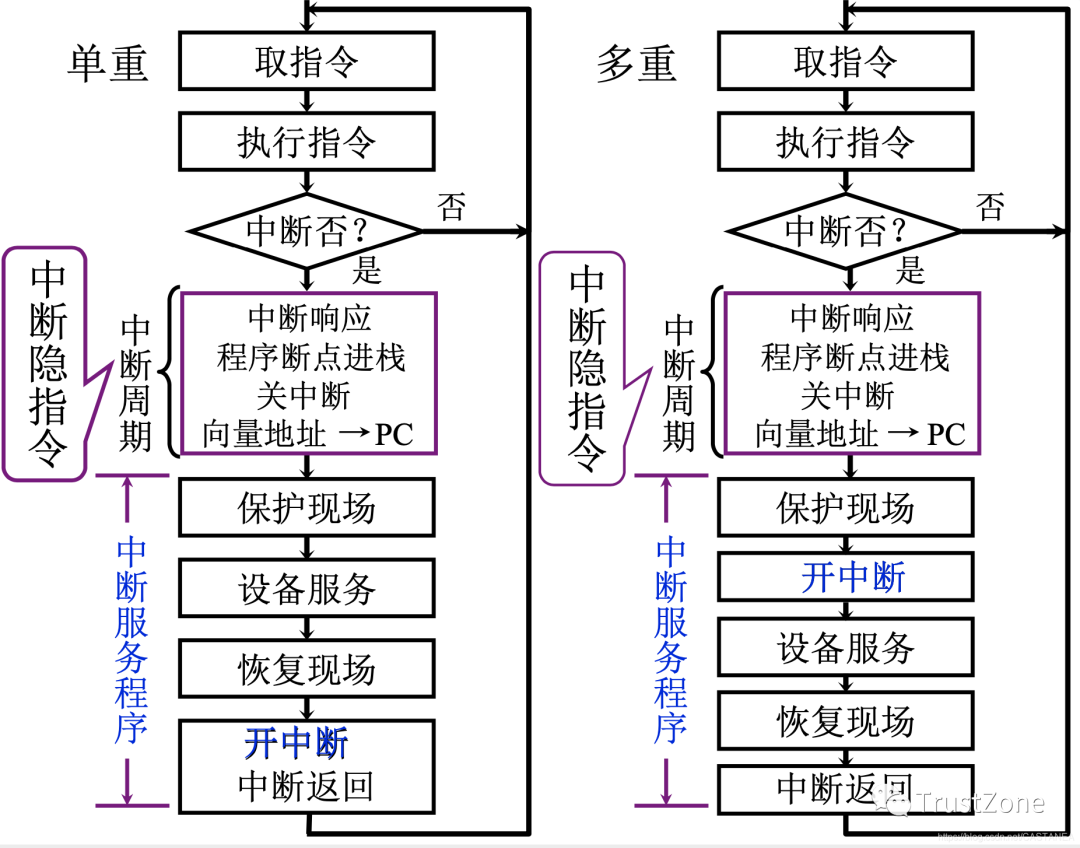

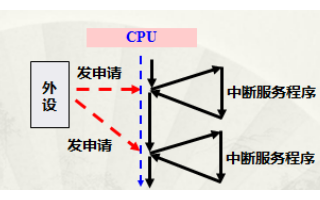

•单重中断在CPU执行中断服务程序的过程中不能被打断。当有新的更高优先级的中断发生时,正在执行的中断服务程序不会被暂停,转而执行新的中断服务程序。

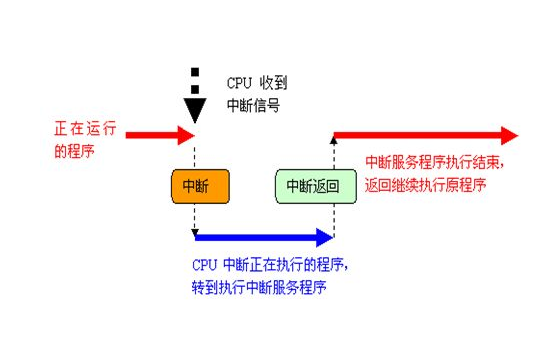

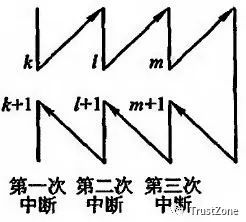

•多重中断在执行某个中断服务程序的过程中,CPU可以去响应更高的中断请求。这被称为中断嵌套。比如,当一个中断服务程序正在执行时,发生了另一个更高优先级的中断,CPU会暂停当前的中断服务程序,转而执行新的中断服务程序。一旦新的中断服务程序执行完毕,CPU会返回到原来被暂停的中断服务程序,继续执行。

注意:单重中断和多重中断的区别在于“开中断”的设置时间不同。对于单重中断,开中断指令设置在最后“中断返回”之前,意味着在整个中断服务处理过程中,不能再响应其他中断源的请求。

而对于多重中断,开中断指令提前至“保护现场”之后,意味着在保护现场之后,若有更高级别的中断源提出请求,CPU也可以响应,从而实现中断嵌套,这是二者的主要区别。

多重中断与中断屏蔽技术

上面我们知道了单重中断和多重中断的区别:

中断的嵌套不能一直嵌套下去,为了保证正在执行的中断服务程序的完整性和提高系统的效率和响应速度,有时候我们在执行种的时候不想新的中断请求干扰正在执行的中断服务程序来提高系统的效率和响应速度和保证正在执行的中断服务程序的完整性。

-

cpu

+关注

关注

68文章

10931浏览量

213533 -

中断

+关注

关注

5文章

900浏览量

41881 -

程序

+关注

关注

117文章

3800浏览量

81575

发布评论请先 登录

相关推荐

关于MPSoC的中断处理介绍

中断系统详解、外部中断

微机原理——8086中断类型以及中断向量表、中断响应、中断返回

12 . 中断

基于单片机的外部中断实验 中断系统知识介绍

什么是中断,中断的介绍

单重中断与多重中断介绍

单重中断与多重中断介绍

评论