1. PI的数学原理

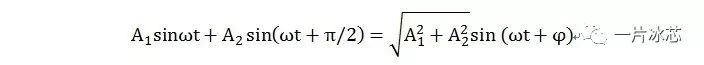

对于信号sin ωt和sin (ωt+π/2),可通过调整二者幅值,实现相位在0~π/2之间的信号。

其中,

对于,

C为常量,上式可写为:

函数tanx和

的趋势相似,在x=0时,二者均为0,tanx在x=π /2时趋于无穷大,

在x趋于C时趋于无穷大。

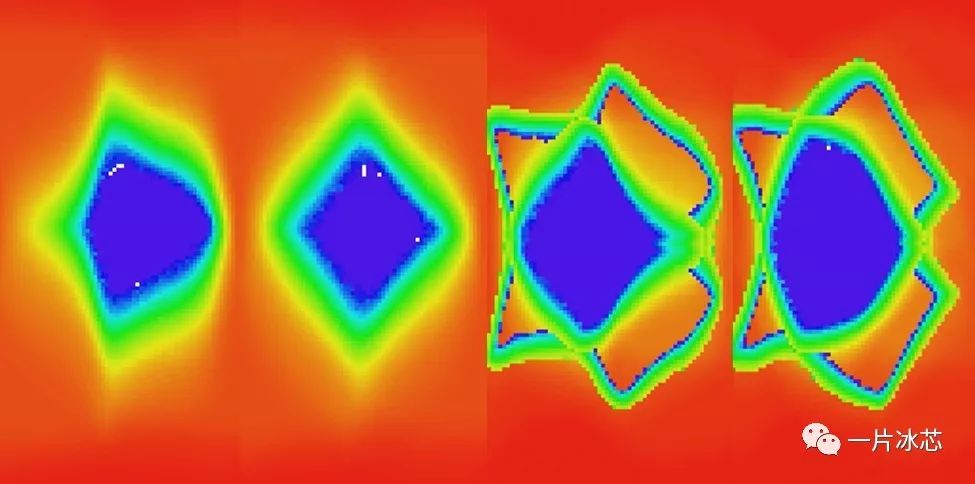

设C为1,利用Matlab,画出相位φ与A2的关系如下图所示。其中,蓝线为相位φ与A2的关系,红线为理想关系曲线。

Fig1. 相位与幅值的关系

可以将公式中π/2推广到π/4,π/8…,可推导出分相数越多线性度越好,但电路设计越复杂,一般都是分成四个相限。

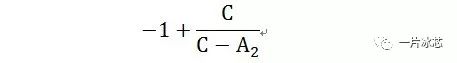

2. PI结构及原理

PI的核心功能就是对来自cpll或qpll的四相位时钟进行相位插值,从而使输出相位能跟随PI code变化,最终使时钟边沿与数据中心位置对齐,达到最佳采样。PI整体框图如图2所示,通路包括DCC Circuit、Clock Buffer、Phase Mixer、Limiting Amplifier、CML-to-CMOS Converter、Divider Circuit、Bias和DAC电路。

Fig2. PI整体框图

PI通路上的每个电路都不可或缺,下面章节将逐一分析每个模块的功能。

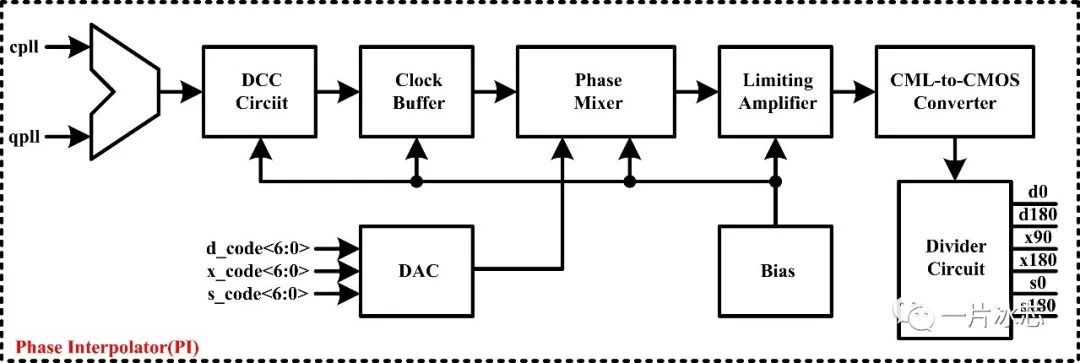

2.1 DCC Circuit

cpll或qpll本地产生的四相位时钟可以保证每个相位50%的占空比,但由于SerDes整体规模庞大,pll时钟往往经过上千微米的走线,layout中即使采用顶层金属,外加电源或地的Shielding也不可避免的产生干扰,进而影响PI输入时钟的占空比,而占空比失真对CDR的影响是致命的,占空比必须要严格限制在50%左右,有些设计会在PI进入CDR的slicer之前加入复杂的占空比校正电路。

本人用到的占空比校正电路较简单,结构如图3所示。该结构是一个电流源作负载的源级负反馈电路,整体传函呈现带通特性,可滤除pll时钟通路上低频干扰引起的占空比失真。

Fig3. Duty-Cycle-Correction Circuit

2.2 Clock Buffer

正弦信号和三角波信号插值可提高PI线性度,因此进入Phase Mixer之前需要将方波信号(通常为半摆幅)整形为正弦信号(三角波不易实现)。Clock Buffer通常采用一级或多级CML结构的Buffer,同时为了保证宽频率范围内都为正弦信号,Clock Buffer的负载电阻、电容及尾电流源通常设为可编程结构。

2.3 Phase Mixer

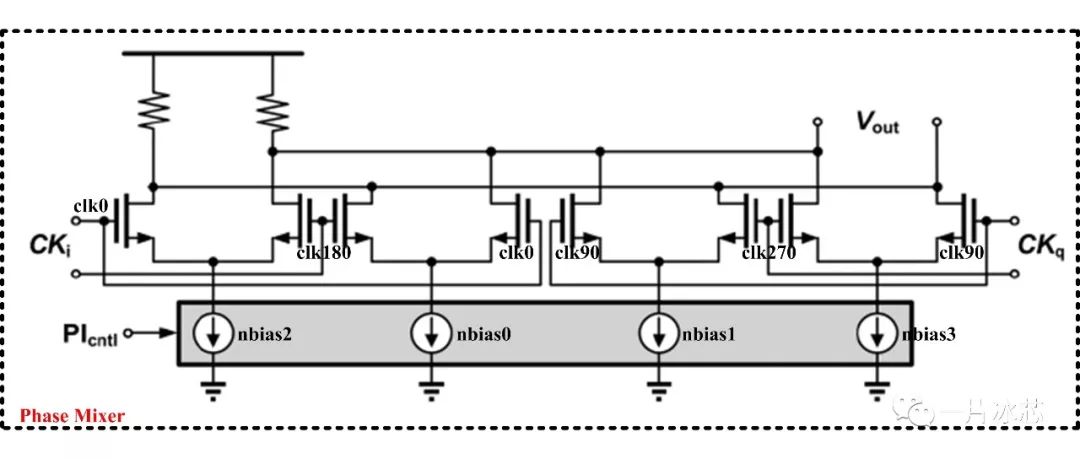

Phase Mixer采用CML结构,如图4所示。其中PIcntl每个相位区间(共四个相位区间)共有32种电流组合,因此插值精度为360°/128=2.8125°。

Fig4. Phase Mixer

进行相位插值时每次只选中两个尾电流源,选中方式由DAC单元中的d/x/s_code<6:0>中的高两位决定。具体控制方式如图5所示,其中Sel6和Sel5对应d/x/s_code<6:5>位,1LSB的ilive电流用于解决相位区间切换时尾电流建立时间引起的PI非线性。

Fig5.相位插值区间真值表

2.4 Limiting Amplifier

Phase Mixer输出信号幅度受DAC输入code调制,这会引入非线性,因此后一级需要增加限幅放大器,来解决幅度变化引起的PI非线性。限幅放大器与Clock Buffer结构类似,都是采用CML结构。

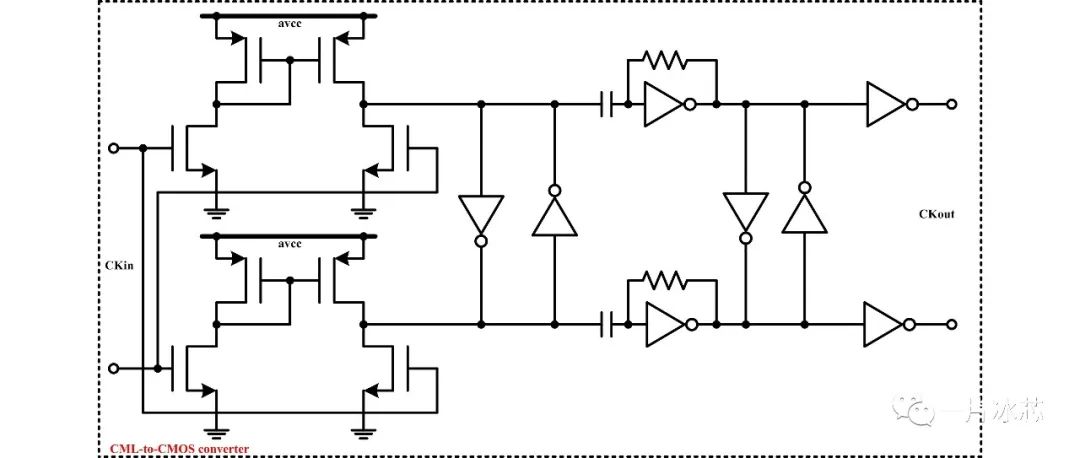

2.5 CML-to-CMOS Converter

前级Limiting Amplifier输出信号幅度为半摆幅的CML电平,进入分频器之前需要转换为CMOS电平,这就需要CML-to-CMOSConverter,结构框图如图6所示。

Fig6.CML-to-CMOS Converter

反相器自偏置的ac-coupling circuit结构可以隔离前级直流干扰,进而改善时钟占空比。

2.6 Divider Circuit

分频电路通过DFF级联的方式,对时钟信号进行1/2/4/8/16分频,来满足不同速率需求。分频器要特别注意复位时序,复位时序会影响时钟的初始相位,初始相位错乱,会导致后面所有相位固定错误。

2.7 Bias

Bias电路用于产生通路上所需的偏置电流。

2.8 DAC

相位插值器是在相位差为90°的4个相位区间进行相位插值,每个相位区间为了得到32个相位,需要一个5位DAC。为了获得较高精度的DAC设计,一般采用分段式结构的电流舵DAC。该结构是将数字码分为两部分进行转换,一般是较高位的数字码采用温度计码,低位的数字码采用二进制码。

相位插值器将相位控制信号转化为带权重的电流,再根据两个输入信号之间的相位关系对两个电流信号进行混合,通过负载电阻又将电流信号转换为电压信号输出。

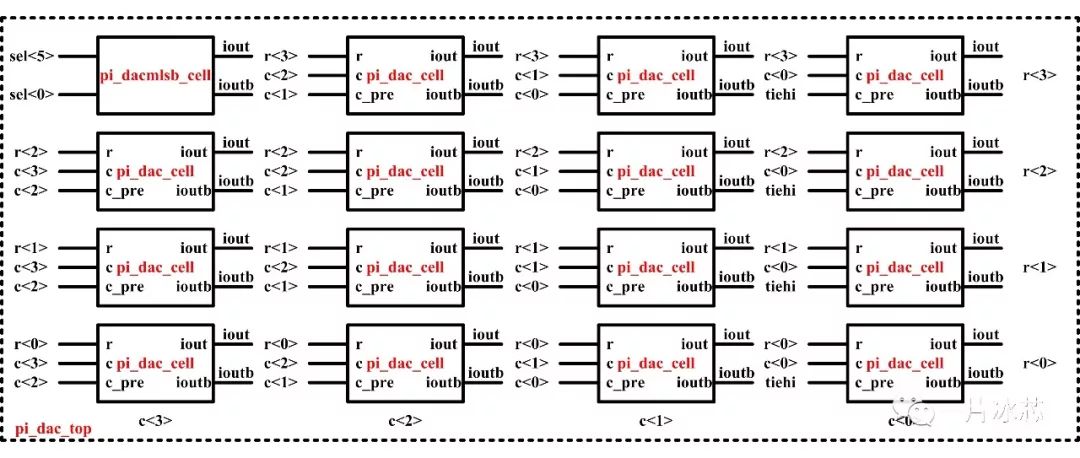

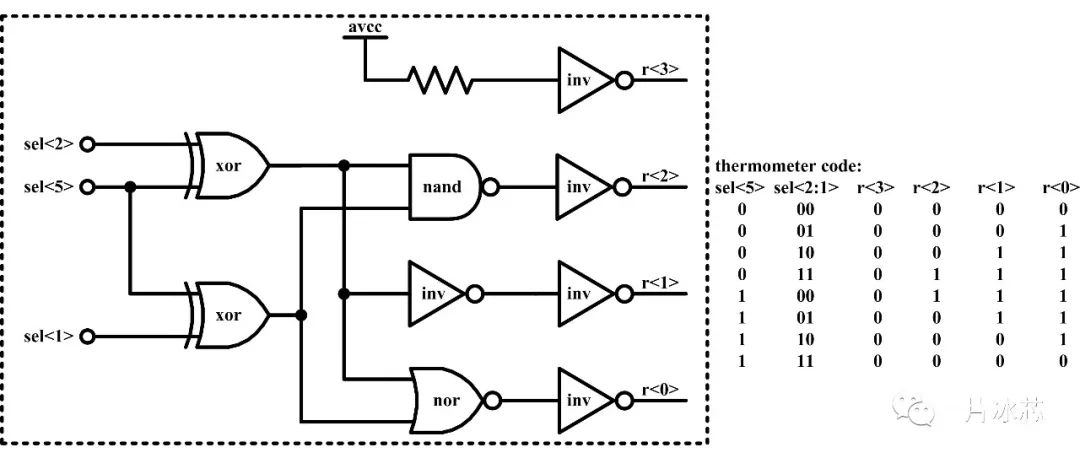

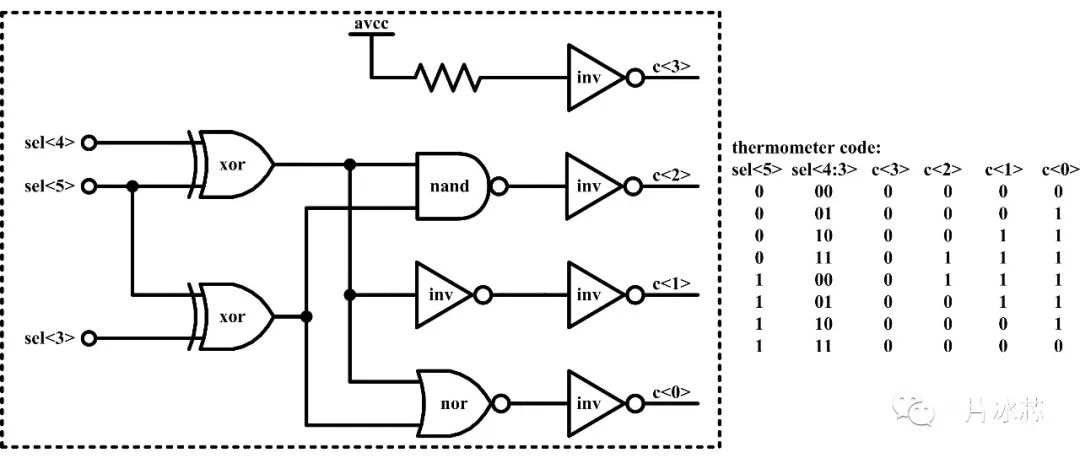

该DAC电路输入的5位数字码采用高4位,低1位的分段结构,高位码为温度计译码,低位码为二进制码。行列译码为4位二进制码到温度计码的译码方式,其中行列译码都为2位二进制到温度计译码,即sel<4:1>位是温度计编码,控制15路电流源;sel<0>是二进制编码,控制1路电流源,通过5位控制编码可以产生32个电流台阶步长。

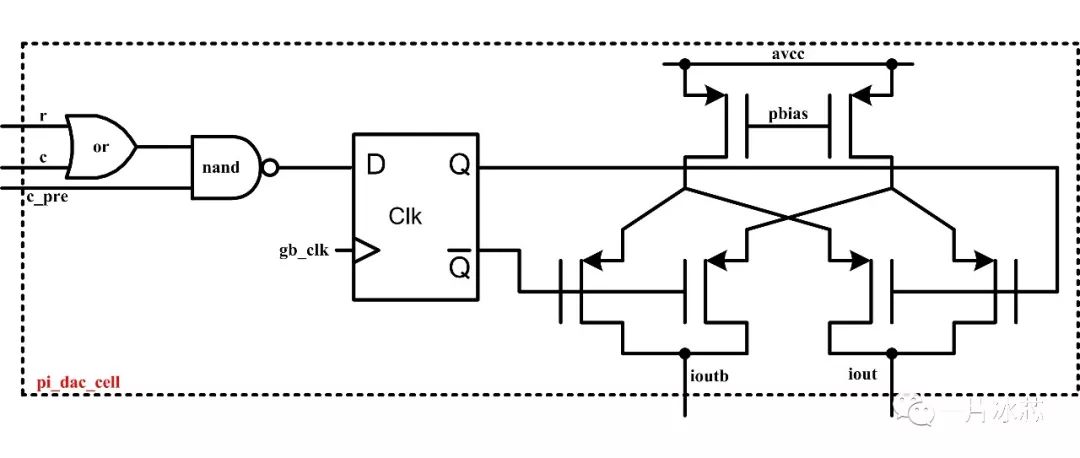

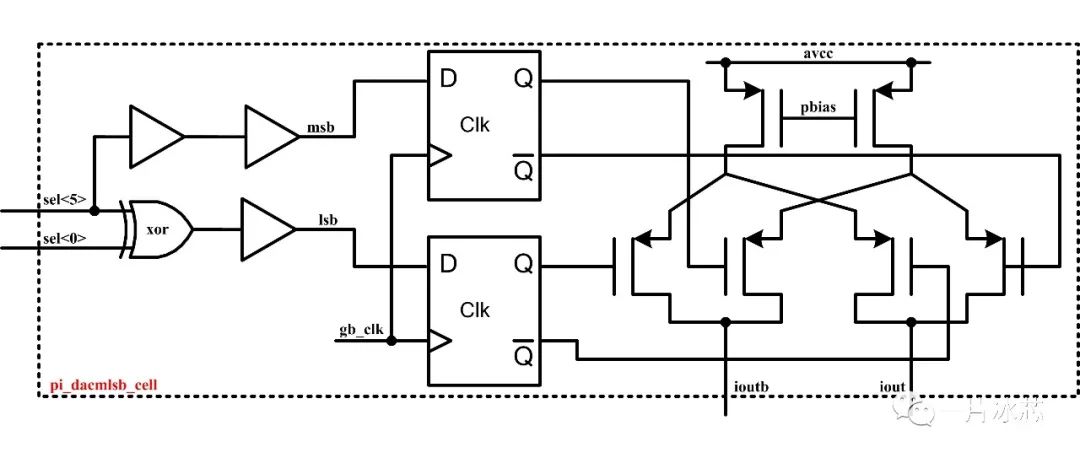

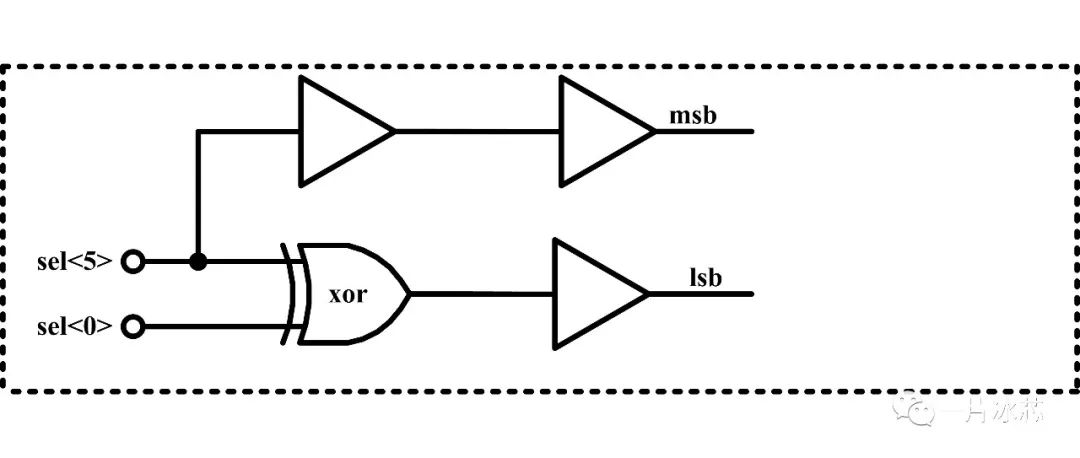

sel<4:0>都与sel<5>进行异或操作,这样可以保证相位区间切换时,电流不会发生突变。图7给出了采用行列译码方式的电流舵DAC顶层框图,其中pi_dacmlsb_cell和pi_dac_cell内部结构分别如图8和图9所示,行列译码和二进制译码逻辑如图10~12所示。

Fig7.DAC Top

Fig8. DAC Top中的pi_dac_cell单元

Fig9.DAC Top中的pi_dacmlsb_cell单元

Fig10. 行译码产生温度码

Fig11. 列译码产生温度码

Fig12.高位和低位二进制码

**3. **测试结果

某一速率下,s路线性度对眼图的影响如图13所示。可以看出,s路非线路会导致眼图形状畸变,相当于眼图测量的“尺子”刻度不均匀。

Fig13. s路非线性对眼图的影响

**4. **总结

①PI输出时钟要满足50%占空比,一般会加入占空比校正电路;

②正弦信号和三角波插值线性度高,插值之前需要整形;

③在非插值区间引入一个LSB的小电流,可以减小区间切换时尾电流的建立时间,从而提高PI线性度;

④PI后增加限幅放大器可以减小PI Code对幅度的调制,从而提高PI线路度;

⑤反相器自偏置的ac-coupling circuit结构可以隔离前级直流干扰,进而改善时钟占空比;

⑥分频器复位时序会影响时钟的初始相位,初始相位错乱,会导致后面所有相位固定错误,设计时应多加留意;

⑦DAC产生的电流要呈现温度码特性。

-

负反馈电路

+关注

关注

1文章

35浏览量

9575 -

CMOS电平

+关注

关注

0文章

24浏览量

7547 -

时钟信号

+关注

关注

4文章

511浏览量

30161 -

限幅放大器

+关注

关注

1文章

50浏览量

10570 -

负载电阻

+关注

关注

0文章

112浏览量

8696

发布评论请先 登录

PI推出电源设计软件PI Expert7.1.5版PI

raspberry_pi各版本差别

冷或门系列PI2121、PI2123 及 PI2125的应用指南

raspberry pi官网

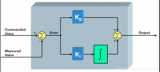

PI调节器介绍及设计

串联型PI和并联型PI调节器的比较

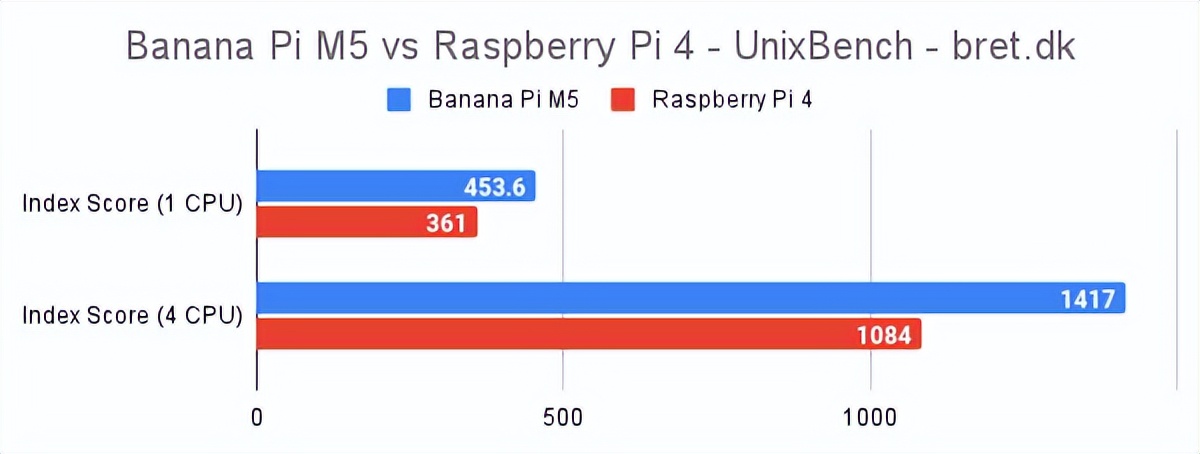

Banana Pi M5 与 Raspberry Pi 4 – 基准测试

PI的数学原理 PI结构及原理

PI的数学原理 PI结构及原理

评论